Waseda University Doctoral Dissertation

# Research on LDPC Decoder Design Methodology for Error-Correcting Performance and Energy-Efficiency

Xiongxin ZHAO

Graduate School of Information, Production and Systems

Waseda University

February 2014

## Abstract

Low-Density Parity-Check (LDPC) codes, as linear block error-correcting codes (ECC), which were invented by Gallager in 1963 and rediscovered by MacKay in 1999, nowadays become a hot topic in a variety of application fields. Due to inherently paralleled decoding algorithm and near Shannon limit error-correcting performance, LDPC codes have been widely adopted in modern communication standards, such as Wi-Fi (IEEE 802.11n), WiMAX (IEEE 802.16e), WPAN (IEEE 802.15.3c) and the second-generation of digital video broadcasting (DVB-x2) family of standards. Moreover, storage systems and optical transmission systems also adopt them for improving the lifetime and reliability of devices or communication distances.

LDPC codes can be decoded in time linear to their code-lengths by using iterative belief propagation (BP) or Two-Phase Message-Passing (TPMP) algorithm which was involving firstly invented by Gallager variable-node and check-node message-updating phases. The independence of calculations among variable-nodes or check-nodes in each phase enables arbitrary parallelism for parallel implementation of decoders. Fully-parallel decoders, in which all the variable-node and check-node processing units are implemented, can achieve the highest parallelism but usually suffer from extremely complicated placement and interconnection. A practical solution is the so-called partial-parallel implementation, in which both or either of variable-node and check-node phases are divided into groups and processed separately to trade-off hardware complexity. Structured LDPC codes such as IRA-(irregular repeat-accumulate) LDPC codes and QC- (quasi-cyclic) LDPC codes are invented for partial-parallel implementation and have been adopted in a variety of wireless/wired communication standards.

On the other hand, for most of application cases, supporting multi-mode (multiple code-lengths and multiple code-rates) decoding in one single decoder is appreciated since the communication channel status may change at all times. However, previous decoders designed with TPMP algorithm largely depend on the codes' properties,

which makes the multi-mode decoding almost impossible. Due to the introduction of Layered decoding algorithm by Mansour in 2003, the development of LDPC decoders obtains a tremendous progress. It cannot only achieve up to twice convergence speed compared to traditional TPMP algorithm, but also provide practical solution for the multi-mode partial-parallel decoder architectures. The Layered algorithm applies the same check-node functions as TPMP algorithm but different variable-node message-passing schedule, which can increase the flexibility of decoder for multi-mode decoding. Actually, almost all the multi-mode decoders for modern wireless communication systems are designated based on the Layered algorithm. As multi-mode LDPC decoders, many works are developed from the multi-mode prototype designed by Mansour (JSSC 2006). Y. Sun (ISCAS 2007) presents a partial-parallel Layered LDPC decoder for QC-LDPC codes. S. Muller (DATE 2009) presents a LDPC decoder IP for DVB-S2 standard with the partial-parallel Layered architecture. B. Xiang (JSSC 2011) presents a dual-path partial-parallel Layered LDPC decoder for WiMAX to increase implementation parallelism. X. Peng (A-SSCC 2011) proposes bit-serial Layered LDPC decoder for WiMAX to further increase parallelism.

However, there are still many problems to be solved for decoder design technologies. 1) Previously published early termination (ET) schemes, which is applied tremendously increase the decoding throughput or reduce the power consumption, are not well-designed. The termination criteria based on approximation methods lead to significant error-correcting performance degradation and insufficient termination speed. 2) For IRA-LDPC decoder architectures which adopt Layered algorithm for multi-mode decoding, the so-called message updating conflict problem involved in Layered scheduling is not yet solved. Previous solutions such as S. Muller's work (DATE 2009) apply approximation method which degrades the convergence speed. 3) The partial-parallel Layered decoder architecture restricts decoding parallelism which makes it be not applicable for applications with high-throughput or ultra-low power consumption requirements.

This dissertation focuses on design methodology for solving the above problems

in multi-mode LDPC decoders. 1) For generic Layered LDPC decoders, an ET scheme named as LSC-ET (last-iteration satisfaction check) scheme is proposed to reduce total decoding time while maintaining the error-correcting performance. 2) For DVB-T2 LDPC decoder, new message updating conflict resolution is proposed to prevent the conflict from occurring during variable-node message updating in Layered decoding. The degradation of error-correcting performance can be avoided. 3) To break the parallelism bottleneck of partial-parallel Layered decoder architecture, 3-state bit-serial fully-parallel Layered decoder architecture is proposed for WiMAX LDPC decoders to increase the decoding parallelism for higher energy-efficiency and enhanced error-correcting performance.

This dissertation consists of the following six chapters.

**Chapter 1 [Introduction]** introduces the scope and purpose of this dissertation. By a brief discussion on related works, problems and deficiencies of previous LDPC decoders are discussed. Finally, the organization of this dissertation is presented.

**Chapter 2** [Background] introduces the fundamentals on LDPC codes, decoding algorithms and decoder architectures. Representations of LDPC codes, including the structured QC-LDPC and IRA-LDPC codes are presented. Evolution of decoding algorithms and their approximation for decoder implementation are also described. Finally, the previous partial-parallel Layered decoder architectures is discussed.

Chapter 3 [A BER Performance-Aware Early Termination Scheme for Generic Layered LDPC Decoder] presents a BER (bit error rate) performance-aware ET scheme for Layered LDPC decoder.

In Layered LDPC decoders, ET scheme without disturbing the decoding schedule is appreciated. Due to the frequently updated a-posteriori probability (APP) messages, hard-decisions (sign of variable-nodes) may be flipped even within each iteration, which means that sequential satisfaction of all check-nodes cannot deduce successful decoding. Previous ET schemes in Layered decoders, such as the HDA-ET scheme (Shao's, IEEE Comm. 1999) and CSC-ET scheme (Ueng's, ISCAS 2009), process the decoding and ET processes concurrently. The former one terminates decoding when the hard-decisions in two successive iterations are the same. The parity-check equations are not checked so that it cannot guarantee successful decoding. The latter one terminates decoding when the parity-checks are satisfied sequentially, which cannot deduce successful decoding.

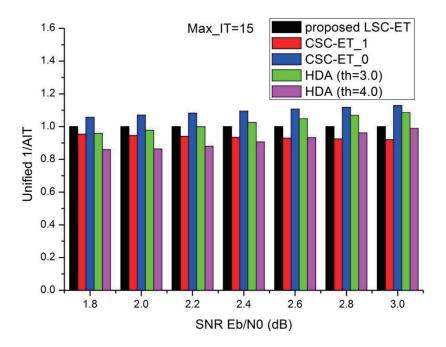

The last-iteration satisfaction check based early termination (LSC-ET) scheme is proposed in this dissertation. In current iteration the parity-check process is done with the hard-decisions generated from the previous iteration. By applying this scheme, lossless BER performance and fast termination speed can be achieved with slight hardware overhead. Compared with CSC-ET scheme, the decoding time reduction is 5%~10% for WiMAX 1/2 rate codes and 2%~5% for DVB-S2 1/2 rate codes.

**Chapter 4 [DVB-T2 LDPC Decoder with Perfect Conflict Resolution]** presents a Layered LDPC decoder for DVB-T2 standard with a novel resolution to the message updating conflict problem.

The message updating conflict problem in Layered implementation becomes a big obstacle for multi-mode decoder design. In previous resolution such as in Muller's work (DATE 2009) the Layers with conflict sub-blocks are decoded in TPMP algorithm. In order to achieve this function, arithmetic units are increased by 50% in processing modules and also the convergence speed is slightly reduced compared to pure Layered decoding.

This dissertation focuses on the conflict resolution for DVB-T2 LDPC decoders against the error degradation. Unlike the previous resolutions, the Layered algorithm is directly applied without modification to the parity-check matrices (PCM) or the decoding algorithm. DVB-T2 LDPC decoder architecture is also proposed with two new techniques which can guarantee conflict-free Layered decoding. The PCM Rearrange technique largely reduces the number of conflicts and eliminates all of data dependency problems between Layers to ensure high pipeline efficiency. The Layer Division technique divides the remaining conflict Layers into two sub-layers and processes them concurrently with a well-designed, overlapped pipeline decoding schedule, so that at most 1.2% of decoding time redundancy is required. As a result, the proposed decoder architecture can reduce the extra arithmetic units involved in Muller's solution and reduce around 1/3 error bits compared to Muller's method.

**Chapter 5** [High-Parallel Performance-Aware LDPC Decoder for WiMAX] presents a synthesizable LDPC decoder IP for WiMAX system with high parallelism and enhanced error-correcting performance.

For high energy-efficiency LDPC decoder design, the proper parallelism is the most important factor. When the parallel level exceeds the maximum Layer size of PCM, energy-efficiency will decrease because of data dependency problem. Although the partial-parallel Layered architecture proposed by Sun can support multi-mode decoding with more than 1Gbps throughput for WiMAX, the limited decoding parallelism restricts decoders from further improved energy-efficiency. Xiang's dual-path partial-parallel Layered decoder architecture (JSSC 2011) focuses on the dependency problem and achieves almost twice parallelism. Peng's bit-serial Layered decoder (A-SSCC 2011) processes each Layer in fully-parallel way to further increase parallelism. However, the saturation process for bit-serial variable-node message updating requires doubled interconnection circuits. Also, the serial-parallel conversion requires huge decoder area since the decoder functionality cannot be composed of bit-serial components only.

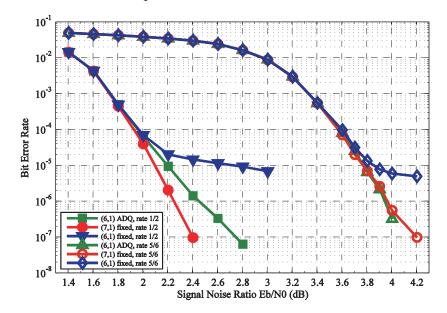

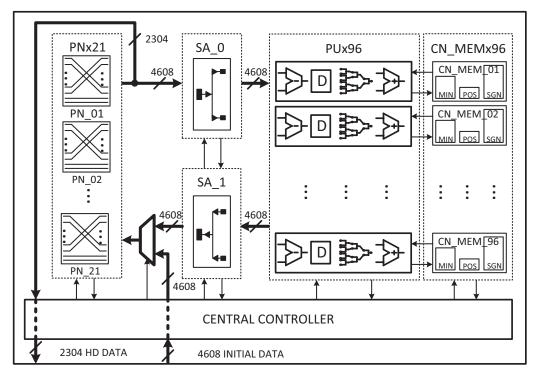

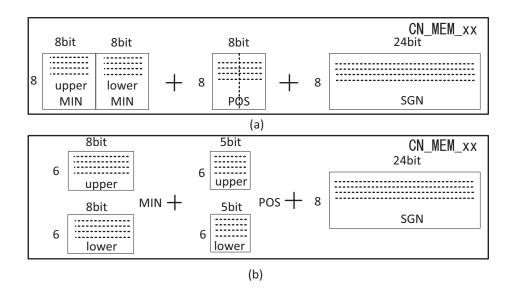

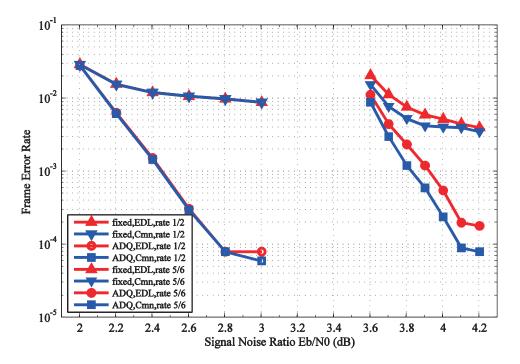

The 3-state fully-parallel Layered decoder is proposed in this dissertation. Two bit-width serial processing is applied instead of 1 bit-width design, which achieves doubled parallelism compared with Peng's work. A new message saturation strategy is proposed to reduce 50% of the interconnection circuits. The improvement in serial-parallel conversion circuits makes the total area increase only 1%. Power synthesis result shows that the proposed decoder achieves 5.83pJ/bit/iteration energy-efficiency which is 46.8% and 72.1% improvement compared to Peng's work and Xiang's work, respectively. Furthermore, an advanced dynamic quantization (ADQ) technique is proposed and implemented in the decoder to enhance BER performance. 6-bit ADQ achieves BER performance close to 7-bit fixed quantization with improved error floor performance.

**Chapter 6 [Conclusion]** concludes the contribution of this dissertation and discusses about the future work.

# Acknowledgement

First of all, I would like to thank my supervisor, Professor Satoshi Goto, for his guidance in my research work, encouragement in my daily life and sufficient financial support. His great foresight and sagacity guide me throughout my research work. His hard working and understanding personality encourage me to follow him all the time. Without his support, I can never get the confidence to defeat every difficulty aboard.

I would like to thank Professor Takahiro Watanabe, Professor Shinji Kimura and Associate Professor Fumiaki Maehara for my research in Waseda University. Thanks for their advices and comments to my dissertation, which is professional and helpful.

Especially, I show my great thanks to Dr. Xiao Peng, Dr. Zhixiang Chen and Dr. Dajiang Zhou for their valuable works in my research and unstopped care in my daily life. I would like to thank Dr. Wen Ji, Dr. Xianghui Wei, Mr. Yichao Lu, Mr. Qian Xie, Ms. Ying Cui, Mr. Nanfan Qiu and Ms. Xin Xiao for working together with me on the LDPC field. I also want to thank all the members of Goto's laboratory together with me during these five years. Thanks to you, I have enjoyed a happy research life in Japan without any homesick and loneliness.

I also extend my heartfelt thanks to my family and my wife. I cannot even live without their support and care in every aspect.

Finally, I should thank the Japanese government scholarship given by MEXT throughout my three-year-long Ph.D. course for my research and life in Japan.

# Contents

| Abstra                                                                                               | nct                                                                                                                                                                                                                                                                                                                                                                                              | I                                                  |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Ackno                                                                                                | wledgement                                                                                                                                                                                                                                                                                                                                                                                       | VI                                                 |

| 1.                                                                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                  |

| 1.1<br>1.2<br>1.2.1<br>1.2.2<br>1.2.3<br>1.3                                                         | Scope of This Research<br>Related Works on LDPC Decoders<br>Early Termination Schemes<br>DVB-x2 LDPC Decoders<br>Multi-Mode QC-LDPC Decoders<br>Organization                                                                                                                                                                                                                                     | 4<br>4<br>5<br>6                                   |

| 2.                                                                                                   | Background                                                                                                                                                                                                                                                                                                                                                                                       | 11                                                 |

| 2.1<br>2.1.1<br>2.1.2<br>2.2<br>2.2.1<br>2.2.2<br>2.3<br>2.3.1<br>2.3.2<br>2.3.3<br>2.4<br><b>3.</b> | LDPC Codes and Their Representations<br>PCM Representation<br>Tanner Graph Representation<br>Structured LDPC Codes<br>QC-LDPC Codes<br>IRA-LDPC Codes<br>LDPC Decoding Algorithms<br>Sum-Product Algorithm<br>Algorithm Approximation for Hardware Implementation<br>Layered Decoding Schedule<br>Partial-parallel LDPC Decoder Architecture<br><b>A BER Performance-Aware Early Termination</b> | 11<br>12<br>13<br>14<br>15<br>17<br>18<br>20<br>22 |

| J.                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                  | 27                                                 |

| 3.1<br>3.1.1<br>3.1.2<br>3.2<br>3.3<br>3.4                                                           | Scheme for Generic Layered LDPC Decoders         Problems in Previous ET Schemes for Layered LDPC Decoder Architecture         HDA-ET Criterion         CSC-ET Criterion         Last-iteration Satisfaction Check Early Termination (LSC-ET) Scheme         Simulation Results and Comparisons         Summary                                                                                  | 27<br>28<br>29<br>30<br>32                         |

| 4.                                                                                                   | DVB-T2 LDPC Decoder with Perfect Conflict                                                                                                                                                                                                                                                                                                                                                        |                                                    |

|                                                                                                      | Resolution                                                                                                                                                                                                                                                                                                                                                                                       | 37                                                 |

| 4.1                                                                                                  | Introduction                                                                                                                                                                                                                                                                                                                                                                                     | 37                                                 |

| 4.2   | Message Updating Conflict in Layered DVB-T2 LDPC Decoder         | 38 |

|-------|------------------------------------------------------------------|----|

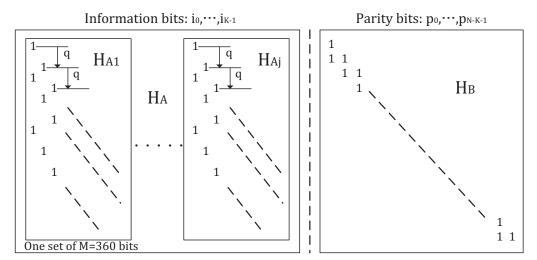

| 4.2.1 | LDPC Codes in DVB-T2 Standard                                    | 38 |

| 4.2.2 | Message Updating Conflict in DVB-T2                              | 40 |

| 4.2.3 | Problems in Previous Conflict Resolutions                        | 41 |

| 4.3   | Resolution to Message Updating Conflict for DVB-T2 LDPC Decoders | 42 |

| 4.3.1 | PCM Rearrange                                                    | 42 |

| 4.3.2 | Layer Division                                                   | 46 |

| 4.4   | Proposed DVB-T2 LDPC Decoder Architecture                        | 52 |

| 4.4.1 | Top-level Decoder Architecture                                   | 53 |

| 4.4.2 | Particular Function Modules                                      | 55 |

| 4.5   | Results and Comparisons                                          | 56 |

| 4.5.1 | Performance Simulation Results                                   | 56 |

| 4.5.2 | Implementation Results                                           | 58 |

| 4.6   | Summary                                                          | 59 |

# 5. High-Parallel Performance-Aware LDPC Decoder for

|         | WiMAX                                                          | 61 |

|---------|----------------------------------------------------------------|----|

| 5.1     | Introduction                                                   | 61 |

| 5.2     | Preliminaries                                                  | 63 |

| 5.2.1   | Layered Decoding Algorithm with Quantization                   | 63 |

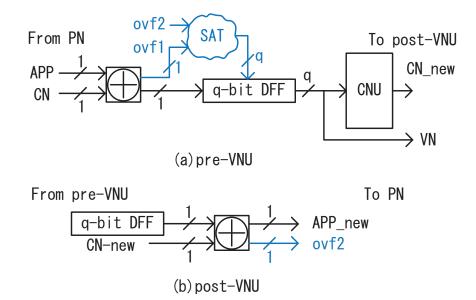

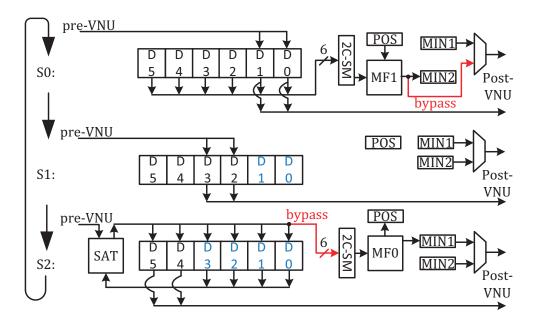

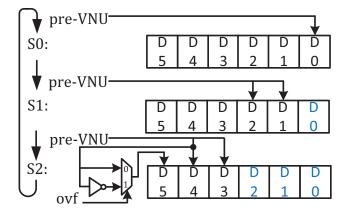

| 5.2.2   | Message Saturation Solution in Bit-serial Decoder Architecture | 65 |

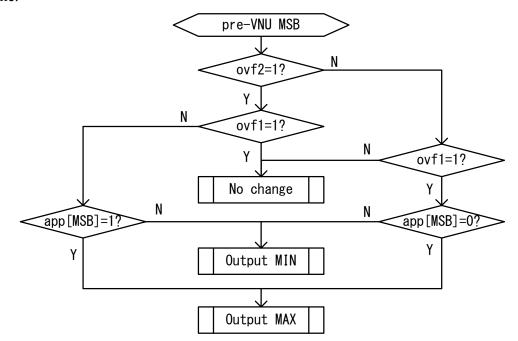

| 5.2.3   | Bit-Serial Layered LDPC Decoder Architecture                   | 67 |

| 5.3     | Advanced Dynamic Quantization Technique                        | 69 |

| 5.3.1   | Saturation Effects in Layered LDPC Decoder                     | 70 |

| 5.3.2   | Advanced Dynamic Quantization                                  | 71 |

| 5.4     | Fully-Parallel Layered LDPC Decoder                            | 74 |

| 5.4.1   | Proposed Decoder Architecture                                  | 74 |

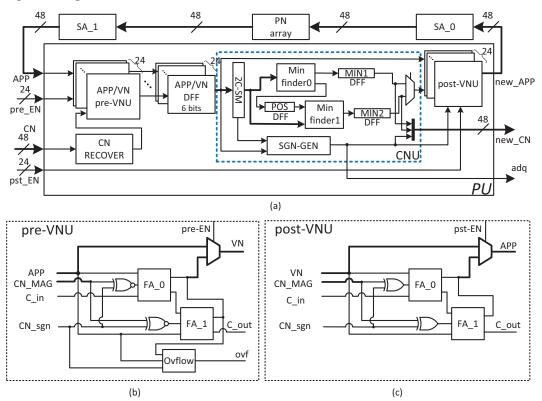

| 5.4.2   | 3-State Processing Unit (PU)                                   | 76 |

| 5.4.3   | Early-detect-logic Based Saturation Process for Post-VNU       | 79 |

| 5.4.4   | Implementation of ADQ Technique                                | 81 |

| 5.5     | Implementation and Comparison Results                          |    |

| 5.6     | Summary                                                        |    |

| 6.      | Conclusion                                                     | 87 |

| Referen | ıce                                                            | 89 |

| Publica | tion List                                                      | 95 |

# **Index of Figures**

| Fig.1.  | Transmission system with FEC using LDPC codes2       |

|---------|------------------------------------------------------|

| Fig.2.  | Parity-check matrix of a (10, 5) linear block code12 |

| Fig.3.  | Tanner graph of a (10, 5) linear block code13        |

| Fig.4.  | PCM of a QC-LDPC code14                              |

| Fig.5.  | Tanner graph for IRA codes16                         |

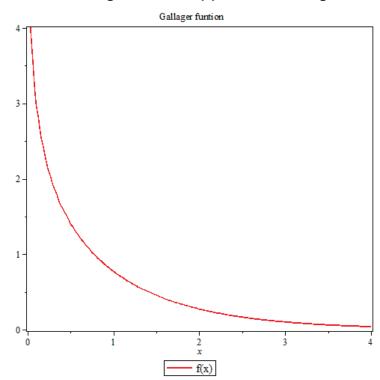

| Fig.6.  | Gallager function curve20                            |

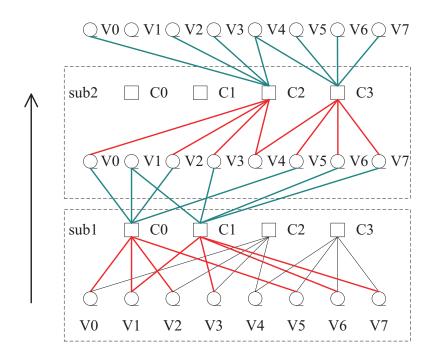

| Fig.7.  | Message updating schedule of layered algorithm23     |

| Fig.8.  | Message updating schedule of TPMP algorithm23        |

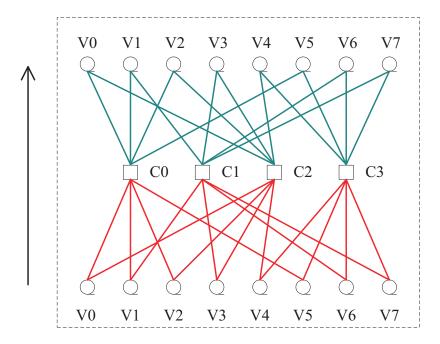

| Fig.9.  | Top-level architecture for partial-parallel layered  |

|         | LDPC decoders25                                      |

| Fig.10. | CSC-ET criterion problem29                           |

| Fig.11. | Last-updated information in PCM31                    |

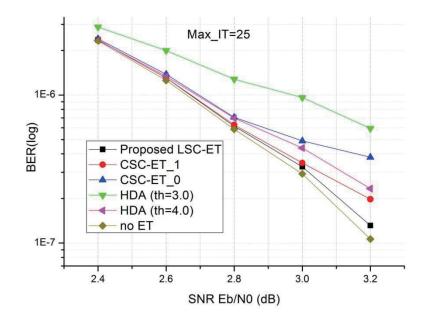

| Fig.12. | BER performance comparison (64800, 1/2)33            |

| Fig.13. | BER performance comparison (2304, 1/2)33             |

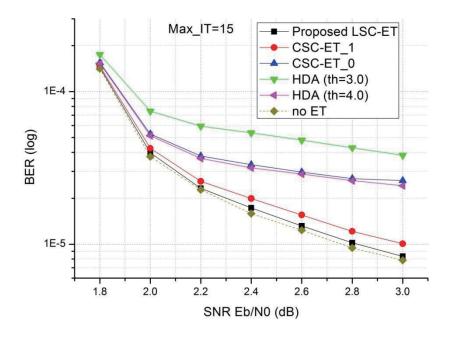

| Fig.14. | AIT performance comparison (64800, 1/2)34            |

| Fig.15. | AIT performance comparison (2304, 1/2)               |

| Fig.16. | PCM of DVB-T2 LDPC codes                             |

| Fig.17. | Three types of blocks in QC-like PCM40               |

| Fig.18. | Example for message updating conflict41              |

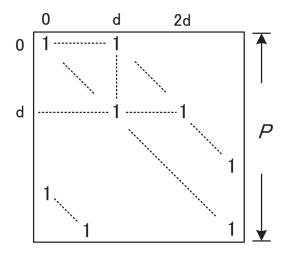

| Fig.19. | Seed matrix of DVB-T2 after rearrangement46          |

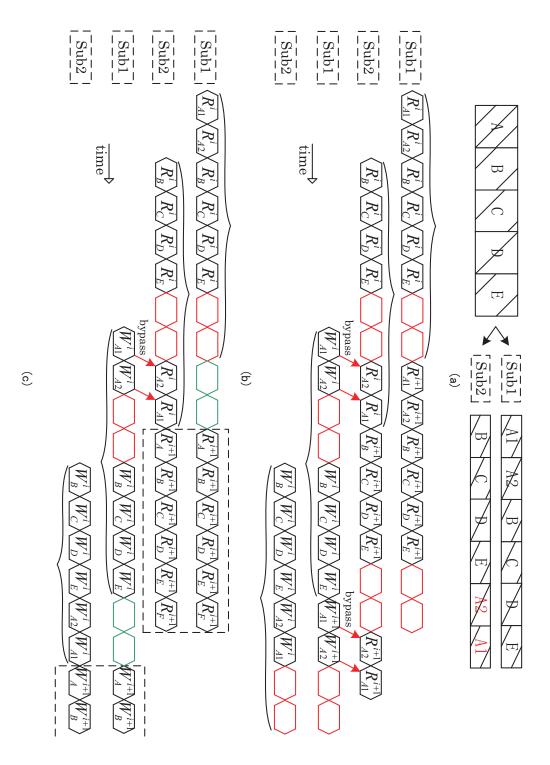

| Fig.20. Layer Division for 8x8 conflict block47               |

|---------------------------------------------------------------|

| Fig.21. Example of (P, d) conflict pattern48                  |

| Fig.22. Division algorithm for (P, d) conflict block          |

| Fig.23. Three division patterns and corresponding d values    |

| for $P = 40$                                                  |

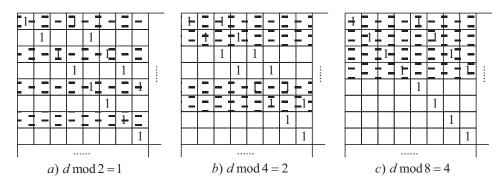

| Fig.24. Timing diagram of fully-overlapped pipeline for       |

| normal layers50                                               |

| Fig.25. Timing diagram of overlapped pipeline for conflict    |

| layers                                                        |

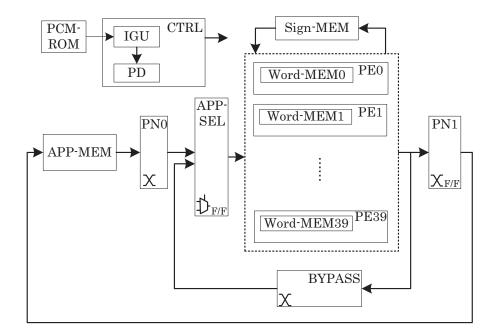

| Fig.26. Top-level decoder architecture for DVB-T253           |

| Fig.27. (a) IGU structure and (b) PE structure56              |

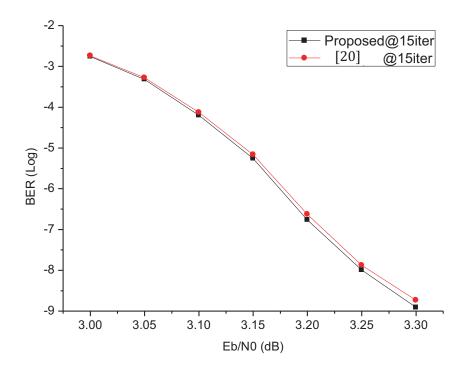

| Fig.28. BER performance comparison of different strategies    |

| for rate 5/6 of DVB-T2 normal frame58                         |

| Fig.29. Diagrams of VNU in bit-serial architecture66          |

| Fig.30. Previous solution to saturation process in bit-serial |

| decoder67                                                     |

| Fig.31. Processing unit structure and timing diagram of       |

| bit-serial layered decoder69                                  |

| Fig.32. Saturation effects in TPMP (a) and layered algorithm  |

| (b)70                                                         |

| Fig.33. BER performance for WiMAX code-rate 1/2 and 5/6       |

| codes using OMS layered algorithm, max 10 iterations,         |

|         | with (6,1) ADQ, (7,1) fixed and (6,1) fixed quantization |    |

|---------|----------------------------------------------------------|----|

|         | schemes                                                  | 73 |

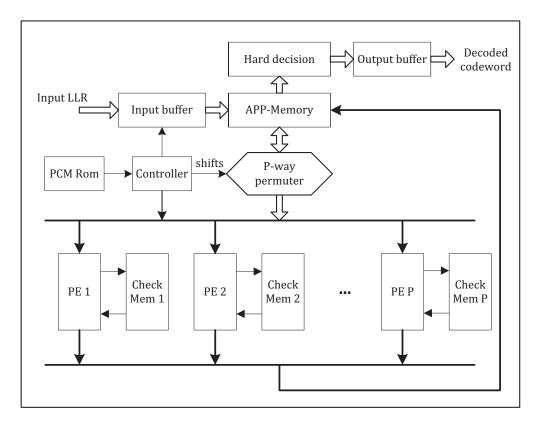

| Fig.34. | Block diagram of the proposed fully-parallel layered     |    |

|         | LDPC decoder architecture                                | 75 |

| Fig.35. | CN message storage method, (a) in [29], (b) in this      |    |

|         | paper                                                    | 76 |

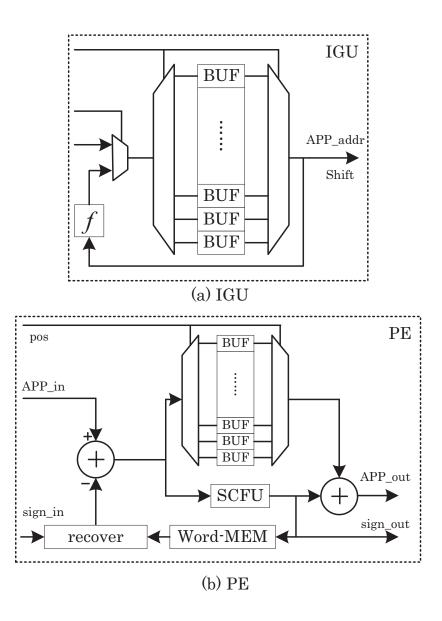

| Fig.36. | Structures of 3-state processing unit (a), pre-VNU (b),  |    |

|         | post-VNU (c)                                             | 77 |

| Fig.37. | Processing tasks in different states                     | 78 |

| Fig.38. | FER performance for early-detect-logic and common        |    |

|         | saturation processes with fixed quantization and ADQ     |    |

|         | schemes for WiMAX code-rate 1/2 and 5/6 codes            | 80 |

| Fig.39. | Execution mechanism for quantization change of APP       |    |

|         | messages                                                 | 82 |

# **Index of Tables**

| Table | 1 Unified  | 1/AIT     | for   | WiMAX              | 1/2   | code    | with  | no-ET |    |

|-------|------------|-----------|-------|--------------------|-------|---------|-------|-------|----|

|       | scheme     | •••••     |       | •••••              |       | •••••   | ••••• |       | 35 |

| Table | 2 Values o | f q and   | code  | -rates of <b>I</b> | OVB-  | S2/T2   | LDPC  | codes | 40 |

| Table | 3 Number   | of conf   | licts | in DVB-T           | 2 nor | rmal fr | ame   |       | 43 |

| Table | 4 Implem   | entation  | and   | comparis           | on re | esults  | ••••• |       | 58 |

| Table | 5 Compar   | rison wit | h pr  | evious Wi          | MAX   | K decoo | lers  |       | 83 |

# **1. Introduction**

In recent years, the demand of efficient, reliable transmission and storage systems for digital data increases rapidly. The emergence of large-scale, high-speed data networks for exchanging, processing and storing the digital data in commercial, military and many other areas further accelerate this trend. The major concern of the system designer is the control of transmission errors to make it more reliable. Such technology is called error control coding (ECC) [1].

Error control strategies for one-way communication systems must use the forward error correction (FEC), in which they employ error-correcting codes (ECC) that automatically correct errors detected at the receiver. Although two-way communication systems can use error detection and retransmission strategy, called automatic repeat request (ARQ), FEC is commonly combined with ARQ to maintain transmission throughput.

Low-Density Parity-Check (LDPC) codes [2], as linear block ECC, which were invented by Gallager in 1963 but mostly ignored by coding researchers for more than 30 years until rediscovered by MacKay in 1999 [3], nowadays become a hot topic in a variety of application fields. Due to inherently paralleled decoding algorithm and near Shannon limit error-correcting performance, LDPC codes have been widely adopted in modern communication standards, such as Wi-Fi (IEEE 802.11n) [4], WiMAX (IEEE 802.16e) [5], WPAN (IEEE 802.15.3c) [6] and the second-generation of digital video broadcasting (DVB-x2) family of standards [7]. Moreover, next generation storage systems and optical transmission systems also adopt them for improving the reliability of devices or communication distances. The rediscovery of LDPC codes makes them strong competitors with turbo codes [8] and BCH codes [9] which occupy FEC field for a long period in a variety of applications such as CD, DVD, SSD, wireless communication standards and optical fiber transmission.

## 1.1 Scope of This Research

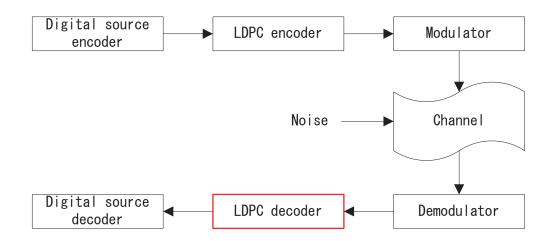

A typical transmission system with FEC using LDPC codes can be represented by the block diagram as shown in Fig.1. During LDPC encoding process, redundant information should be added to the encoded source data against the noise of transmission channel. LDPC Decoder attempts to correct the error occurs in the transmission to recover the original source data. Compared to the LDPC encoder and modulator/demodulator, the LDPC decoder is much more complicated and critical module, since the throughput requirement and error-correcting capability becomes more and more critical in recent applications. In this dissertation, contributions are focused on design techniques of LDPC decoders.

Fig.1. Transmission system with FEC using LDPC codes

Error-correcting capability is the first factor should be taken into consideration for LDPC decoders. Especially in the one-way transmission systems, such as DVB-T2 standard [10], DVB-S2 standard [11], optical fiber transmission system and many kinds of storage media. Even in the FEC-ARQ based systems such as WiMAX system, higher error-correcting capability can effectively enlarge the transmission throughput. The energy-efficiency of decoders, i.e. electrical energy dissipation for per decoded bit, is another important indicator for LDPC decoders. For mobile devices, such as portable TV, smart phone and tablet PC, the communication modules still dissipate a large proportion of power supply. On the other hand, decoders which can only decode one kind of LDPC code is inconvenient in many applications. Apart from the changeable channel conditions of wireless communications, even for wired communication systems such as Ethernet transmission, the signal attenuation could be changed a lot due to different Ethernet cable lengths. Capability of multi-mode (multi-length and multi-rate) decoding in one single LDPC decoder is appreciated and becomes universal in both industrial products and academic researches.

In this dissertation, we emphasis on both the error-correcting performance and energy-efficiency of multi-mode LDPC decoders. For generic multi-mode LDPC decoders which are decoded with layered algorithm, (i.e. multi-mode oriented architectures) we have proposed an new early termination scheme to reduce power consumption while it can maintain the error-correcting performance. [12] The proposed ET scheme terminates the decoding process immediately when it detects a successful decoding during iterative layered LDPC decoding schedule. Furthermore, the proposed ET scheme already combines the parity-check process so that signals can be generated exactly to indicate successful decoding.

We also design two LDPC decoders for two totally different applications as follows.

- For DVB-T2 standard which adopts structured irregular repeat-accumulate (IRA) LDPC codes, we have designed full-mode partial-parallel LDPC decoder architecture to enhance error-correcting performance by solving the inherent message updating conflict problem when the decoder applies the layered decoding algorithm. It is the first time DVB-T2 LDPC decoder can apply pure layered scheduling. [13]

- 2) For WiMAX standard which adopts structured quasi-cyclic (QC) LDPC codes, we have designed full-mode, fully-parallel LDPC decoder architecture to increase the decoding parallelism. Power synthesis result shows that the proposed decoder achieves 5.83pJ/bit/iteration energy-efficiency at over 1Gbps throughput, which is 46.8% improvement compared to state-of-the-art WiMAX LDPC decoder [14]. Furthermore, a newly proposed advanced dynamic quantization (ADQ) scheme

for layered algorithm is combined in the decoder to enhance error-correcting performance so that 6-bit ADQ quantization can achieve performance close to 7-bit fixed quantization with largely improved error floor performance.

## 1.2 Related Works on LDPC Decoders

Previously published works which relate to the contributions of this dissertation are briefly discussed in this section. Especially, the problems and techniques which need to be improved of the previous works are described in detail.

#### 1.2.1 Early Termination Schemes

Early termination (ET) scheme is a hot topic not limited to LDPC decoder design since it can tremendously increase the decoding throughput or reduce the power consumption. Many works have been done for both traditional TPMP decoder architecture and layered decoder architecture. [15]-[19] ET schemes are usually focused on two different aspects: one is to terminate the decoding process when a codeword is not able to be successfully decoded before reaching the maximum iteration time; [17][18] another one is to terminate the decoding process when a codeword is successfully decoded (or almost finishes decoding) before reaching the maximum iteration time. [15][16][19]

Early termination scheme in layered decoder architecture is different from that in TPMP architecture since the a-posteriori probabilities (APP) are updated more than once in a single iteration of layered decoding process which are only updated once in each iteration of TPMP. For ET schemes in layered decoding schedule, previous works have been done in [15],[16].

In [15], the popular hard-decision aided (HDA) ET scheme, which is traditionally applied in turbo decoding algorithm, stores all the hard-decisions and compares the decoded codeword in two successive iterations. If the decoded codeword of these two iterations are exactly the same, the decoding will be terminated. Otherwise, the decoding process will be terminated when a predefined maximum iteration time is reached. However, this ET scheme does not verify the parity-check equations so that it cannot guarantee lossless BER performance. Sometimes an additional constraint is added to increase the reliability, in which all the absolute values of APP should be larger than a predefined threshold. The threshold value for HDA varies from different channel conditions thus it needs to be determined through simulations for better BER performance. The extra condition reduces termination speed but still cannot ensure lossless BER performance. In [16], the current-iteration satisfaction check based early termination (CSC-ET) which examines the parity-check equations layer by layer during the decoding process. When all the parity-check equations are satisfied sequentially in a single iteration, the decoding process will be terminated immediately or after additional iterations for better BER performance. Both of them can terminate the decoding to reduce average iteration numbers without disturbing the layered pipelined schedule.

However, both of them bring BER performance degradation, which worsens the decoding performance and is not suitable to be implemented in BER performance-aware decoders, such as DVB-S2 standard. Moreover, both of schemes just terminate the decoding process without checking the parity-check equations. For two-way transmission applications which adopt FEC-ARQ error control strategy such as WiMAX, parity-check equations must be checked to generate successful decoding signals. In such case, decoders must be combined with extra parity-check logics.

#### 1.2.2 DVB-x2 LDPC Decoders

The DVB-x2 family of standards, which contains DVB-S2 (satellite transmission system), DVB-T2 (terrestrial transmission system) and DVB-C2 (cable transmission system), adopt code-length as long as 64k bits IRA-LDPC codes as their inner ECC concatenated with outer BCH codes to achieve quasi-error-free (QEF) reception conditions within 0.8dB from the Shannon limit.

11 kinds of code-rates and 2 kinds of code-lengths of LDPC codes have been

adopted in DVB-S2 standard for various transmission channel conditions and applications, while DVB-T2 and DVB-C2 standards pick up 6 and 4 kinds of code-rates out of 11 for their own application fields, respectively. These specialized applications require decoders to support multi-mode decoding. For such extremely long structured IRA-LDPC codes, many researchers attempt to implement multi-mode LDPC decoders with layered algorithm for efficient partial-parallel decoding in similar ways as for multi-mode QC-LDPC decoders. [20]-[24]

To apply the layered algorithm for decoders, PCM should be divided into layers and in each layer the check-node processing should be processed in parallel way. However, the IRA-LDPC codes usually cannot be implemented with layered algorithm as straightforward as QC-LDPC codes because of the so-called message updating conflict problem which appears while divides the PCM into layers. Simply ignoring the conflicts will cause a lot of cutting-edge problems during layered decoding, which leads to significant performance loss and relatively high error floor. The BER performance degradation can be larger than 0.2dB compared with conflict-free layered decoding performance. [24] In order to solve this problem, authors in [20] and [21] decoded the conflict layers with TPMP algorithm while authors in [22] and [23] tried to modify the PCM of conflict layers. The author in [24] proposed a selective recalculation strategy adding to the layered decoding algorithm is quite not hardware-friendly due to its instability of complexity.

### 1.2.3 Multi-Mode QC-LDPC Decoders

The structured QC-LDPC codes have been adopted in many wireless communication standards, not limited to WiMAX, Wi-Fi and WPAN standards. For various transmission channel conditions and applications, multi-mode decoding capability is required in such standards.

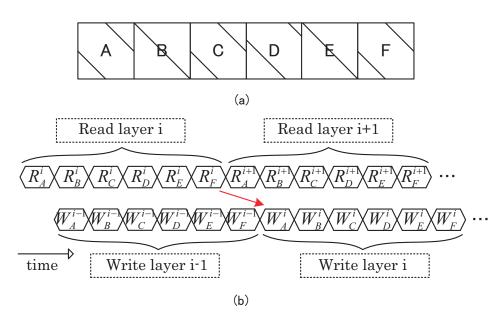

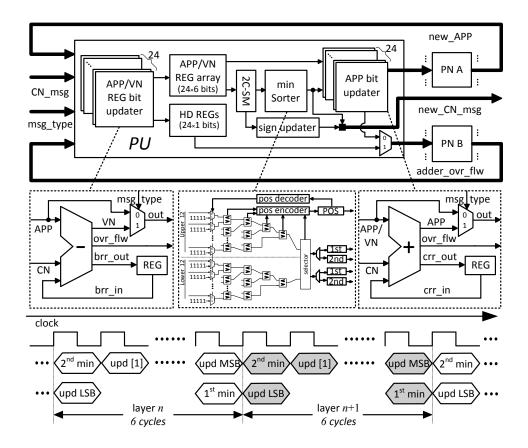

For multi-mode QC-LDPC decoders, previous works have been done in [25]-[29]. Some of the decoder works can only support multi-lengths decoding such as [28]. The authors in [25] present a partial-parallel layered LDPC decoder for QC-LDPC codes, which can support variable code-length and code-rate decoding. The presented partial-parallel layered architecture can deal with different PCMs (i.e. different code-rates) by changing the barrel shifter factors of the so-called permutation network. However, Such kind of block by block layered decoding schedule suffers from the data dependency problem in layered decoding which limits the decoding parallelism and throughput. By using this architecture, WiMAX LDPC codes need at least 76~88 clock cycles for decoding each iteration. Authors in [26] present a dual-path partial-parallel layered LDPC decoder for WiMAX in order to increase decoding parallelism with two sets of processing units. By utilizing the sub-matrix reordering and complex bypass controlling techniques to reduce the influence from data dependency problem, they finally reduce the number of clock cycles to 48~54 per iteration. In order to further increase decoding parallelism for better energy-efficiency, we propose a bit-serial layered LDPC decoder for WiMAX in [29]. In this work, the data dependency between adjacent layered does not exist and the block by block decoding schedule is changed to fully-parallel schedule. Bit-serial message processing style is applied to avoid complicated processing units and interconnection. As a result, the number of clock cycles per iteration is reduced to 24~48 while the area of decoder is as large as that of [26].

## 1.3 Organization

This dissertation contains the following six chapters.

Chapter 1 introduces the scope and purpose of this dissertation. By a brief discussion on related works, problems and deficiencies of previous LDPC decoders are discussed. Finally, the organization of this dissertation is presented.

Chapter 2 introduces the fundamentals on LDPC codes, decoding algorithms and decoder architectures. Representations of LDPC codes, including the structured QCand IRA-LDPC codes are presented. Evolution of decoding algorithms and their approximation for decoder implementation are also described. Finally, commonly adopted partial-parallel decoder architectures are demonstrated.

Chapter 3 presents a BER performance-aware ET scheme for layered LDPC decoder. Unlike the ET schemes in traditional TPMP decoders, in layered LDPC decoders ET scheme without disturbing the decoding schedule is not easily designed. Due to the frequently updated a-posteriori probability (APP) messages, hard-decisions may be flipped even within each iteration, which means sequential satisfaction of all check-nodes cannot deduce successful decoding. Previous ET schemes in layered decoders, such as the HDA-ET scheme (Shao's, IEEE Trans. On Comm. 1999) and CSC-ET scheme (Ueng's, ISCAS 2009), suffer from both significant performance loss and slow termination speed. The most important is that the above schemes do not check the parity-check equations so that extra parity-check logics need to be implemented in the decoder.

The last-iteration satisfaction check based early termination (LSC-ET) scheme is proposed in this dissertation. In current iteration the parity-check process is done with the hard-decisions generated from the previous iteration. By applying this scheme, lossless BER performance and fast termination speed can be achieved with acceptable hardware overhead. Moreover, the proposed ET scheme is not limited to any LDPC codes or check-node message-updating functions.

Chapter 4 presents a layered LDPC decoder for DVB-T2 standard with a novel resolution to the message updating conflict problem. Although the structured IRA-LDPC codes specified in DVB-x2 family achieve excellent coding gain, the message updating conflict problem in layered implementation becomes a big obstacle for multi-mode decoder design. In previous resolution such as in Muller's work (DATE 2009) the layers with conflict sub-blocks are decoded in TPMP algorithm. In order to achieve this function, arithmetic units are increased by 50% in processing modules and also the convergence speed is slightly reduced compared to pure layered decoding. Simulation results show that compared to pure layered decoding performance this strategy leads to 1.5 times of error bits in the same condition in the worst case.

In this dissertation we focus on the conflict resolution for DVB-T2 LDPC

decoders against the error degradation. Unlike the previous resolutions, we can directly apply the layered algorithm without modifying parity-check matrices (PCM) or the decoding algorithm. DVB-T2 LDPC decoder architecture is also proposed with two new techniques which can guarantee conflict-free layered decoding. The PCM Rearrange technique largely reduces the number of conflicts and eliminates all of data dependency problems between layers to ensure high pipeline efficiency. The Layer Division technique deals with the remaining conflicts with a well-designed, overlapped pipeline decoding schedule. At most 1.2% of decoding time redundancy is required. As a result, the proposed decoder architecture can reduce the maximum iteration number required in DVB-T2 decoder and the extra arithmetic units involved in Muller's solution can be avoided.

Chapter 5 presents a synthesizable LDPC decoder IP for WiMAX system with high parallelism and enhanced error-correcting performance. Although the partial-parallel layered architecture can support multi-mode decoding with more than 1Gbps throughput for WiMAX, the limited decoding parallelism restricts decoders from better energy-efficiency. By taking the advantages of both layered scheduling and fully-parallel architecture, the 3-state fully-parallel decoder is proposed in this dissertation, which can fully support multi-mode decoding specified in WiMAX with the parallelism more than 4 times higher than Xiang's dual-path partial-parallel layered decoder architecture (JSSC 2011) and twice than our previous bit-serial decoder (Peng's, A-SSCC 2011).

In the proposed decoder, 6-bit quantized messages are split into bit-serial style and 2 bit-width serial processing lines work concurrently so that only 3 clock cycles are required to decode one layer. By reducing the redundant MUX logics and check message memory of our previous work (Peng's, A-SSCC 2011), it doubles the parallelism and solves the message saturation problem of bit-serial arithmetic with only 1% area increase. Power synthesis result shows that the proposed decoder achieves 5.83pJ/bit/iteration energy-efficiency which is 46.8% and 72.1% improvement compared to Peng's work and Xiang's work, respectively. Furthermore, an advanced dynamic quantization (ADQ) technique is proposed and implemented in the decoder to enhance BER performance in layered decoder architecture. With about 2% area overhead, 6-bit ADQ can achieve BER performance close to 7-bit fixed quantization with improved error floor performance.

Chapter 6 concludes the contribution of this dissertation and discusses about my future work.

# 2. Background

This chapter introduces the fundamentals on LDPC codes, decoding algorithms and decoder architectures. Representations of LDPC codes, including the structured QC- and IRA-LDPC codes are presented. Evolution of decoding algorithms and their approximation for decoder implementation are also described. Finally, commonly adopted partial-parallel decoder architectures are demonstrated.

## 2.1 LDPC Codes and Their Representations

An LDPC code is a linear block code for which the parity-check matrix (PCM) has a low density of 1's. Like all kinds of linear block codes, it can be defined via a sparse parity-check matrix H of size  $M \times N$ .

Regular (n, k) LDPC codes are one kind of LDPC codes whose parity-check matrix H contains exactly Wc ones per column and Wr = Wc (n/m) ones per row, where Wc << m. The number of ones in common between any two rows is no greater than one.

If the number of ones per column or per row is not constant, the code are called irregular LDPC codes. It has been shown that long random irregular LDPC codes perform arbitrarily close to the Shannon limit.

Gallager did not provide a good code constructing method algebraically and systematically. Good LDPC codes that have been found are largely computer generated, and their encoding is very complex. But later many researchers introduced their ways to construct LDPC codes based on finite geometries. Some long finite-geometry LDPC codes have error-correcting performance only a few tenths of a decibel away from the Shannon limit.

#### 2.1.1 PCM Representation

PCM representation is a common method to represent an LDPC code. The PCM H for a given code can be derived from its generator matrix G (and vice-versa).

When one defines a code, he usually uses PCM or generator matrix to show it while PCM is convenient for decoding and generator matrix for encoding. Of course, both regular and irregular LDPC codes can be represented by PCMs.

A (10, 5) linear block code which is the null space of the following PCM is shown in Fig.2. It is easy to check that this code is a (4, 2) regular LDPC code.

|     | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

|-----|---|---|---|---|---|---|---|---|---|---|

|     | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 |

| H = | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 |

|     | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

| H = | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 1 |

Fig.2. Parity-check matrix of a (10, 5) linear block code

#### 2.1.2 Tanner Graph Representation

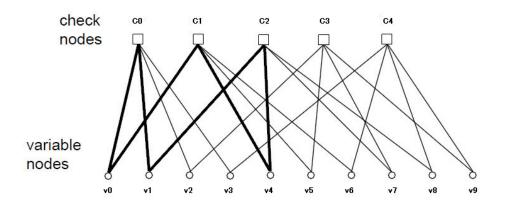

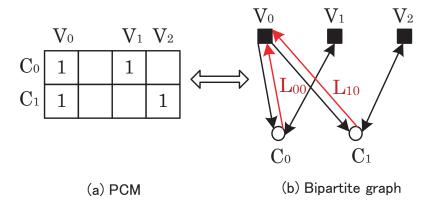

A useful graphical representation of linear block codes is the representation by a factor graph or Tanner graph [30], which displays the incidence relationship between the codeword bits and the parity-check sums that check on them. There are two classes of nodes in a Tanner graph, the variable-nodes and check-nodes. The Tanner graph of a code is drawn according to the following rule:

Check-node j is connected to variable-node i whenever element  $h_{ji}$  in H is a '1'.

Fig.3 shows the corresponding Tanner graph to that its PCM is shown in Fig.2. When there is a '1' in the PCM, there is an edge between the corresponding variable-node and check-node.

Fig.3. Tanner graph of a (10, 5) linear block code

For a regular LDPC code, the degrees of all the variable-nodes in the Tanner graph are the same and equal to the column weight of the parity-check matrix; and the degrees of all the check-nodes are the same and equal to the row weight of the parity-check matrix. Such a Tanner graph is said to be regular. Furthermore, there are no two variable-nodes of an LDPC code are both checked by two different check-nodes. This implies that the Tanner graph of an LDPC code does not contains cycles of length 4. Short cycles will degrade the iterative decoding performance and even prevent the decoding from convergence.

## 2.2 Structured LDPC Codes

The performance of LDPC codes largely depends on their code structures. A large number of LDPC codes are proposed to achieve near capacity performance, efficiency in encoding and decoding processes, reduced memory requirement, and so on. In this chapter, we put emphasis on two kinds of structured LDPC codes which are the quasi-cyclic (QC) LDPC codes and irregular repeat accumulate (IRA) LDPC codes. For parallel decoder implementation, structured LDPC codes such as IRA-LDPC codes and QC-LDPC codes have been adopted in a variety of wireless/wired communication standards.

## 2.2.1 QC-LDPC Codes

Originally, a quasi-cyclic code is defined as a linear code for which cyclically shifting a codeword a fixed number  $n_0 \neq 1$  of symbol position either to the right or to the left results in another codeword. For  $n_0 = 1$ , a quasi-cyclic code is a cyclic code. [31]

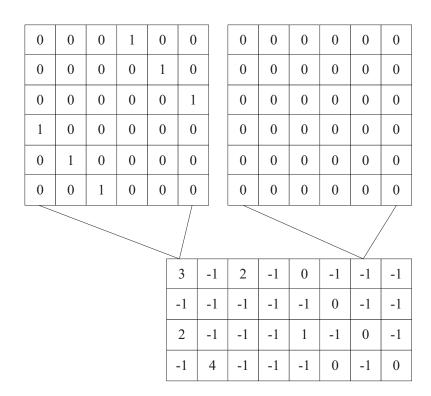

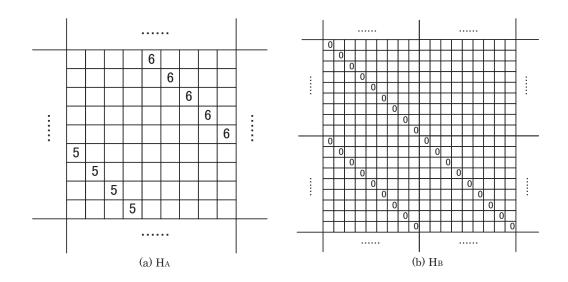

While in real applications, the definition of QC-LDPC structure is a little bit different from the original QC code definition. LDPC codes such as in WiMAX are defined as QC-LDPC codes. QC-LDPC codes are characterized by the parity-check matrix that consists of small square blocks, which is also called sub-blocks, that are zero matrices or shifted identities. A simple example is shown in Fig.4.

Fig.4. PCM of a QC-LDPC code

Fig.4 shows the  $48 \times 24$  parity-check matrix of a QC-LDPC code. The  $8 \times 4$  matrix with numbers is named as the seed matrix. Each position in the seed matrix specifies a zero matrix or a cyclically shifted identity. In this example each block is a  $6 \times 6$  sub-matrix. '-1' in the seed matrix means a zero matrix as shown above and the

non-negative numbers in blocks are the shift values for shifted identities. Due to the cyclic property of QC-LDPC codes, they are effectively suitable for parallel implementation. We can easily combine each row block or column block in the PCM as a partition to process partial-parallel decoding.

The WiMAX LDPC codes belong to such kind of QC-LDPC codes. There are six different classes of codes, which contain four different code rates R from 1/2 to 5/6 [5]. All of the codes have the similar code structure and can be encoded and decoded efficiently. They consist of a fix size of twenty-four columns in their seed PCM, in which the block size is z by z (z is the expansion factor). The first R\*24 columns in the seed PCM correspond to the information part and the remained columns correspond to the parity part. The number of rows in the seed PCM depends on the code rate R and equals to the parity part. The parity part has a fixed structure according to the encoding scheme.

The size of z is ranged from 24 to 96 with a step size equal to 4. There are totally 19 kinds of code length, which range from 576 to 2304 bits.

For the variable sizes of sub-matrices, the WiMAX standard only gives six seed matrices for the longest code-length. For other sizes of sub-matrices, they propose equations (2.1) and (2.2) to scale the shift value p(f, i, j) accordingly.

$$p(f,i,j) = \begin{cases} p(i,j), p(i,j) \le 0\\ \left\lfloor \frac{p(i,j)z_f}{z_0} \right\rfloor, p(i,j) > 0 \end{cases}$$

(2.1)

$$p(f,i,j) = \begin{cases} p(i,j), p(i,j) \le 0\\ \mod(p(i,j), z_f), p(i,j) > 0 \end{cases}$$

(2.2)

Equation (2.1) is for rate 1/2, 3/4A, 3/4B, 2/3B and 5/6 codes while equation (2.2) is only for rate 2/3A codes.

#### 2.2.2 IRA-LDPC Codes

Irregular repeat accumulate (IRA) codes are a generalization of the repeat accumulate (RA) codes. [32] IRA codes can be encoded and decoded in linear time.

Compared to the standard LDPC codes, IRA codes have reduced encoding time [41]. IRA codes can be divided into two types: the non-systematic and systematic ones. In this dissertation, we only focus on the systematic IRA codes.

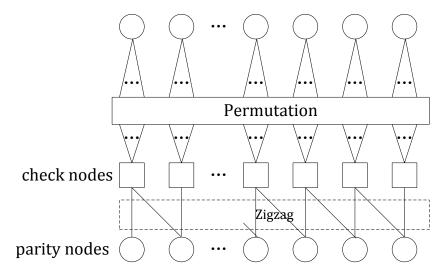

The Tanner graph for IRA codes is shown in Fig.5.

#### Information nodes

Fig.5. Tanner graph for IRA codes

The variable nodes can be divided into information nodes and parity nodes. The variable nodes connect to the check nodes randomly, and the parity nodes connect to the check nodes in a zigzag pattern as shown in Fig.5. The zigzag pattern enables the encoding process of IRA codes to be realized with accumulators.

The parity-check matrix of the systematic IRA code consists of two parts. One part is deterministic, and the other part is generated randomly. Therefore the PCM H can be described by equation (2.3) as follows.

$$H_{M \times N} = \begin{bmatrix} A_{M \times K} & \begin{vmatrix} 1 & 0 & 0 & \cdots & 0 \\ 1 & 1 & 0 & & 0 \\ 0 & 1 & 1 & & 0 \\ \vdots & & \ddots & \vdots \\ 0 & \cdots & 0 & 1 & 1 \end{bmatrix}$$

(2.3)

We denote the codeword by  $c = (i_1, ..., i_K, p_1, ..., p_M)$  where *i* are information bits and *p* are parity bits. Then, using this PCM, the encoding can be carried out by

$$p_1 = \sum_{k=1}^{K} i_k h_{1,k} \tag{2.4}$$

$$p_m = p_{m-1} + \sum_{k=1}^{K} i_k h_{m,k}, 2 \le m \le M$$

(2.5)

The most important property is that the parity bits are determined from the information bits and the random part of PCM without any computation of the generator matrix. So that the encoding process can be simplified.

LDPC codes specified in DVB-x2 standards are systematic IRA codes. The code-lengths are 64800 bits for normal frame and 16200 bits for short frame. For different channel conditions and applications, there are totally 11 kinds of code-rates defined in DVB-x2 standards, ranged from 1/4 to 9/10. More detail about the features of LDPC codes in this family of standards will be discussed in chapter 4.

## 2.3 LDPC Decoding Algorithms

LDPC codes can be decoded in various ways. Among them the Sum-product algorithm (SP), also called Message-passing algorithm or Belief propagation algorithm (BP), provides the best error-correcting performance and yet is practically implementable. In this section, firstly the basic SP decoding algorithm and some approximations for simplifying the decoder implementation are discussed. Then we pay attention to the layered decoding schedule and explain the reason why most of multi-mode decoders adopted such algorithm.

### 2.3.1 Sum-Product Algorithm

LDPC codes can be decoded iteratively with the SP algorithm as described in [1]. In this algorithm, firstly we define the column index sets A(m) and the row index sets B(n) as follows:

$$A(m) = \left\{ n | H_{mn} = 1 \right\}$$

$$B(n) = \left\{ m | H_{mn} = 1 \right\}$$

For the Additive white Gaussian noise (AWGN) channel with noise variance  $\sigma^2$ and received signal  $y_i$ , the conditional probability of being  $x_i = 0$  or  $x_i = 1$  is represented as follows:

$$P(y_i \mid x_i = 0) = \frac{1}{\sqrt{2\pi\sigma^2}} \exp(-\frac{(y_i - 1)^2}{2\sigma^2})$$

$$P(y_i \mid x_i = 1) = \frac{1}{\sqrt{2\pi\sigma^2}} \exp(-\frac{(y_i + 1)^2}{2\sigma^2})$$

The input to the SP algorithm is the initial message of  $\lambda_n$ . As a log likelihood ratio, the initial message  $\lambda_n$  for the AWGN channel can be represented as follows:

$$\lambda_{n} = \ln \frac{P(y_{n} \mid x_{n} = 0)}{P(y_{n} \mid x_{n} = 1)} = \frac{\frac{1}{\sqrt{2\pi\sigma^{2}}} \exp(-\frac{(y_{n} - 1)^{2}}{2\sigma^{2}})}{\frac{1}{\sqrt{2\pi\sigma^{2}}} \exp(-\frac{(y_{n} + 1)^{2}}{2\sigma^{2}})}$$

$$= -\frac{(y_{n} - 1)^{2}}{2\sigma^{2}} + \frac{(y_{n} + 1)^{2}}{2\sigma^{2}} = \frac{2y_{n}}{\sigma^{2}}$$

(2.6)

Following steps shows the detailed process of the logarithm domain SP decoding:

#### [Initialization]

Calculate the logarithm likelihood ratio (LLR)  $\lambda_n$  for n = 1, 2, ..., N - 1using equation (2.6), where  $\sigma^2$  is the variance of noise generated by the AWGN Channel. Set  $\beta_{mn} = \lambda_n$  for each (m, n) satisfying  $H_{mn} = 1$ . Set the loop counter l = 1 and the maximum number of iterations is set to  $l_{max}$ .

#### Step 1 [Check-Node Update]

For all the check-nodes  $C_m$  in the order from m = 1, 2, ..., M, compute the intermediate messages  $\alpha_{mn}$  according to equation (2.7), where each set (m, n) satisfies  $H_{mn} = 1$ .

$$\alpha_{mn} = \left(\prod_{n' \in A(m) \setminus n} sign(\beta_{mn'})\right) \times f\left(\sum_{n' \in A(m) \setminus n} f(|\beta_{mn'}|)\right)$$

(2.7)

Where function f(x), which is also called Gallager function, is defined as follows:

$$f(x) = \ln \frac{\exp(x) + 1}{\exp(x) - 1}$$

#### Step 2 [Variable Node Update]

For all the variable-nodes  $V_n$ , in the order from n = 1, 2, ..., N, compute the message  $\beta_{mn}$  with equation (2.8), for each set of (m, n) satisfying  $H_{mn} = 1$ .

$$\beta_{mn} = \lambda_n + \sum_{m' \in B(n) \setminus m} \alpha_{m'n}$$

(2.8)

#### Step 3 [Hard-Decision]

Calculate all the tentative hard-decision bits  $\hat{y}_n$  for n = 1, 2, ..., N.

$$\hat{y}_n = \begin{cases} 0, sign(\lambda_n + \sum_{m' \in B(n)} \alpha_{m'n}) = +1\\ 1, sign(\lambda_n + \sum_{m' \in B(n)} \alpha_{m'n}) = -1 \end{cases}$$

#### Step 4 [Parity-Check]

If the tentative hard-decision vector  $(\hat{y}_1, \hat{y}_2, \dots, \hat{y}_N)$  satisfies the parity-check equation (2.9), output the codeword, and terminate the decoding iteration. If not, go to step 1.

$$H \cdot (\hat{y}_1, \hat{y}_2, \cdots, \hat{y}_N)^T = 0 \tag{2.9}$$

#### **Step 5 [Maximum Iteration Check]**

If  $l \le l_{\max}$ , set the loop counter  $l \leftarrow l+1$  and go to Step 1. Otherwise output the

decoded codeword  $(\hat{y}_1, \hat{y}_2, \cdots, \hat{y}_N)$  and stop decoding.

## 2.3.2 Algorithm Approximation for Hardware Implementation

The original SP algorithm is not hardware-friendly due to the non-linear Gallager function which involves large numbers of exponential, multiplicative, and look-up table (LUT) operations in the check-node (CN) message updating functions. The Min-sum (MS) approximation [33] is invented to achieve lower computation complexity.

Consider the curve of Gallager function f(x) as shown in Fig.6.

Fig.6. Gallager function curve

We may conclude that the term of Gallager function more depending on the smallest  $\beta_{mn'}$  value in  $f\left(\sum_{n'\in A(m)\setminus n} f(|\beta_{mn'}|)\right)$  so that we can get the rough

approximation as follows:

$$f(\sum_{n'\in A(m)\setminus n} f(|\beta_{mn'}|)) \approx \min_{n'\in A(m)\setminus n} |\beta_{mn'}|.$$

(2.10)

Equation (2.10) shows that the MS algorithm can make the CN message

updating function performed only by addition and comparison operations, which is comparably suitable for hardware implementation.

Since the original MS algorithm degrades the error-correcting performance significantly, in real implementation, the modified types MS algorithms are introduced. The most popular and simple ones are the so-called Normalized min-sum (NMS) algorithm [34] and Offset min-sum (OMS) algorithm [35]. The two variations of the MS algorithm usually adopted in recent LDPC decoder implementations to make trade-off between error-correcting performance and implementation complexity. By delicate selecting the corresponding parameters, both can achieve approaching error-correcting performance as SP algorithm.

The NMS approximation algorithm is that on the basis of MS algorithm, CN messages multiply a normalize factor  $\kappa$  as defined in equation (2.11), which can make the calculation of CN messages  $\alpha_{mn}$  much accuracy. Parameter  $\kappa$  is usually set to 0.625 (= 5/8), 0.75 (= 3/4) or 0.875 (= 7/8) for hardware implementation consideration.

$$\alpha_{mn} = \left(\prod_{n' \in A(m) \setminus n} sign(\beta_{mn'})\right) \times \kappa \min_{n' \in A(m) \setminus n} |\beta_{mn'}|$$

(2.11)

The OMS approximation algorithm is that on the basis of MS algorithm, CN messages make an offset subtraction of the minimum value as defined in equation (2.12). In order not to flip the sign of CN messages, additional condition is added to the subtraction operation. Experimental parameter  $\beta$  is usually set to 0.125 (= 1/8) for implementation.

$$\alpha_{mn} = \left(\prod_{n' \in A(m) \setminus n} sign(\beta_{mn'})\right) \times \max(\min_{n' \in A(m) \setminus n} |\beta_{mn'}| - \beta, 0)$$

(2.12)

Notice that for different LDPC codes and signal to noise ratio (SNR) status, the above approximated algorithms may quite performance different results. In real applications, the selection should be based on carefully and systematic simulations.

## 2.3.3 Layered Decoding Schedule

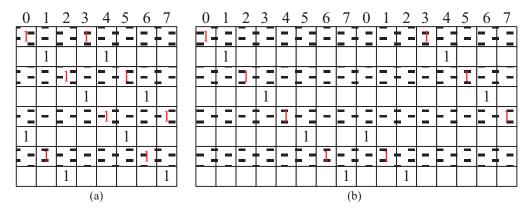

The Layered decoding algorithm, which is also called Turbo-decoding Message-passing (TDMP) algorithm, is invented to make trade-off between error-correcting performance and hardware complexity. The CN function is the same as SP algorithm, but the message updating schedule is totally different. The SP algorithm or TPMP schedule uses one phase to process CN message updating and another for VN message updating. Unlike the TPMP schedule, the layered schedule divides check-nodes into several groups. It seems like that one iteration is divided into several sub-iterations. Inside each sub-iteration, the decoding schedule is the same as TPMP. It means that during a single iteration the APP messages can be updated several times. For each CN (or group of CN), the APP messages are updated after the CN message updating immediately in layered algorithm. The updated APP messages participate in the CN updating of the following CN (or group of CN) within the iteration, which is different from TPMP who cannot use such updated information until the next iteration. It is already proven that the more frequent APP message updating accelerates the convergent speed by at most twice in [36]. Fig.7 and Fig.8 show the difference between layered algorithm and TPMP on message updating schedules. It can be seen clearly that in layered schedule for each sub-iteration the connection become simpler than TPMP algorithm, so that the layered decoding schedule can be considered as one possible solution for partial-parallel implementation.

Nevertheless, the data dependency problem will become serious in layered algorithm due to frequent APP message updating, which will limit the flexibility and parallelism of its hardware implementations.

Fig.7. Message updating schedule of layered algorithm

Fig.8. Message updating schedule of TPMP algorithm

Following steps shows the detailed process of the layered decoding algorithm:

#### [Initialization]

Calculate the log likelihood ratio (LLR)  $\gamma_n$  for n = 1, 2, ..., N - 1 using equation (2.6), where  $\sigma^2$  is the variance of noise generated by the AWGN Channel.

Set  $\beta_{mn} = \lambda_n$  for each (m, n) satisfying  $H_{mn} = 1$ . Set the loop counter l = 1 and the maximum number of iterations is set to  $l_{max}$ . Set intrinsic message  $\lambda_{mn} = 0$ .

#### Step 1 [Layer Update]

For each layer: a subtraction calculates the difference, then the new intrinsic messages and APP is calculated with equation (2.13), (2.14), (2.15):

$$\rho_{mj} = \gamma_j - \lambda_{mj} [l-1] \tag{2.13}$$

$$\lambda_{mj}[l] = (\prod_{n \in A(m) \setminus j} sign(\rho_{mn})) \times f(\sum_{n \in A(m) \setminus j} f(|\rho_{mn}|))$$

(2.14)

$$\gamma_{j} = \rho_{mj} + \lambda_{mj}[l] \tag{2.15}$$

#### Step 2 [Hard-Decision]

Compute all the tentative LDPC codeword bits  $\gamma_n^{\wedge}$  for n = 1, 2, ..., N.

$$\hat{\gamma}_{n} = \begin{cases} 0, sign(\gamma_{n}) = +1\\ 1, sign(\gamma_{n}) = -1 \end{cases}$$

(2.16)

#### Step 3 [Parity-Check]

If the tentative hard-decision vector  $(\hat{\gamma}_1, \hat{\gamma}_2, \dots, \hat{\gamma}_N)$  satisfies the parity-check equation (2.9), output the codeword, and terminate the decoding iteration. If not, go to step 1.

$$H \cdot (\hat{\gamma}_1, \hat{\gamma}_2, \cdots, \hat{\gamma}_N)^T = 0 \tag{2.17}$$

#### **Step 4 [Maximum Iteration Check]**

If  $l \leq l_{\max}$ , set the loop counter  $l \leftarrow l+1$  and go to Step 1. Otherwise output the decoded codeword  $(\hat{\gamma}_1, \hat{\gamma}_2, \dots, \hat{\gamma}_N)$  and stop decoding.

Since the layered decoding algorithm accelerates the convergence speed for decoding LDPC codes and is especially suitable for multi-mode LDPC decoder implementation, the contributions in this dissertation are all based on layered decoding algorithm.

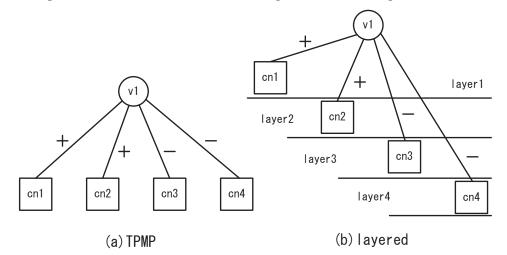

# 2.4 Partial-parallel LDPC Decoder Architecture

The general partial-parallel layered LDPC decoder architecture is shown in Fig.9. Not limited to QC-LDPC codes, all the structured LDPC codes which can be divided into layers and for each layer the corresponding CN message updating functions can be independently processed, can utilize this decoder architecture.

Fig.9. Top-level architecture for partial-parallel layered LDPC decoders

The functions for important modules are described as follows.

- 1) **APP-Memory**: APP message memory, store APP messages with bit-width of w, where w is the APP message quantization bit size;

- 2) PE {1, 2, ..., P}: Processing elements, paralleled execute the layer message updating functions for each CN of each layer;

- 3) Check memory {1, 2, ..., P}: Check-node message memory, exchange messages directly with corresponding PEs to update CN messages;

- 4) PCM Rom: Store the parity-check matrix information in a

particular way;

- 5) Controller: Generate all the addresses for memories and control the iterative, pipelined decoding process;

- 6) P-way Permuter: Permute a number of P APP messages to corresponding PEs, which allows changeable connections between CNs and VNs, enabling multi-mode decoding. For QC-LDPC codes, P is equal to the expansion factor and it is usually constructed with barrel shifters.

The pipelined iterative decoding schedule is that in each clock cycle a proper APP message block is fetched from APP Memory and goes through the P-way Permuter for a barrel shift operation, and then goes into all the PEs waiting for layer messages updating with proper check messages. After a whole layer inputted and calculated, the updated APP messages and check messages will be written back to the corresponding addresses. The read and write operations will not be stopped until a data hazard occurs.

The partial-parallel layered decoder architecture is widely adopted in such as WiMAX and Wi-Fi decoders because of its moderate parallelism and capability for multi-mode decoding. However, the data dependency problem between adjacent layers limits the parallel level, which restricts this architecture from achieving higher parallelism for high-speed applications.

# 3. A BER Performance-Aware Early Termination Scheme for Generic Layered

# **LDPC Decoders**

Besides the decoding schedules, early termination (ET) scheme is another hot topic in LDPC decoding field since it can tremendously increase the decoding throughput or reduce the power consumption. Many works have been done for both traditional TPMP decoder architecture and layered decoder architecture. Early termination in layered decoder architecture is different to that in TPMP one since the APP messages are updated more than once in a single iteration of layered decoding process which are only updated once in TPMP. For ET schemes in layered decoding schedule, previous works have been done. [15][16] Both of them can terminate the decoding rapidly without disturbing the pipelined layered decoding schedule. However, they bring significant BER performance degradations, which worsen the decoding performance and cannot be applied in BER performance-aware applications, such as DVB-S2 standard.

In this chapter, we propose a BER performance-aware ET scheme for generic layered LDPC decoder. Unlike the previous solutions, it terminates the decoding process based on parity-check functions to ensure successful decoding. By using the proposed scheme, the lossless BER performance and fast termination speed are achieved with acceptable hardware overhead. As a hardware module, the proposed ET scheme is not limited to any standards or check-node message updating functions.

## 3.1 Problems in Previous ET Schemes for Layered

# LDPC Decoder Architecture

Due to the difference between TPMP and layered decoding schedule, traditional -27-

early termination schemes, which verify the satisfaction of all the parity-check equations, are not precise anymore for the layered decoding architectures since the hard-decisions of APP messages are frequently changed.

The termination criteria of the previous works [15][16] are introduced and also the problems of them are discussed.

#### 3.1.1 HDA-ET Criterion

The most famous ET scheme is the popularly used hard-decision aided (HDA) ET scheme which is originally implemented in turbo decoder. It temporarily stores the hard-decisions and compares the decoded codeword in two successive iterations. If the decoded codeword of two iterations are the same, the decoding will be terminated. Otherwise, the decoding process will be terminated when a predefined maximum iteration time is reached. Since this scheme cannot guarantee acceptable BER performance, sometimes an additional constraint is added to enhance the reliability, in which all the magnitude values of APP are larger than a predefined threshold. The threshold value for HDA-ET varies from different channel conditions and LDPC codes thus it needs to be determined via simulations for better BER performance.

The mechanism for HDA-ET scheme is simply based on observations that in successful decoding the average magnitudes of APP messages are growing faster during iterations and hard-decisions converge to the true codeword. On the opposite, in failed decoding the average magnitudes of APP messages are oscillated and small.

However, two special cases sometimes happen. One is that the hard-decisions converge to a pattern with small number of errors. The HDA-ET criterion terminates the decoding before reaching the maximum iteration time but cannot report a unsuccessful decoding. Another is that the hard-decisions already converge to the true codeword, but several APP cannot get larger due to quantization effect. In such case the decoding cannot be terminated until reaching the maximum iteration time.

Obviously, bigger APP threshold values make the prediction much reliable. They greatly affect the termination speed while cannot get rid of BER performance

- 28 -

degradation effectively. Moreover, the HDA-ET scheme makes the error floor occurred quite early. This worsens the error-correcting performance especially in high SNR conditions.

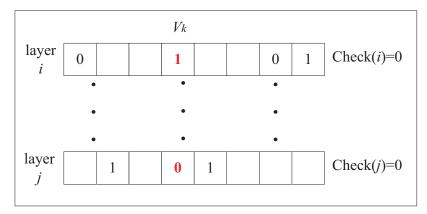

#### 3.1.2 CSC-ET Criterion

Another ET scheme for layered decoding in [16], which we name it as current-iteration satisfied check early termination scheme (CSC-ET), examines the parity-check equations layer by layer with the decoding. When all the parity-check equations are satisfied sequentially in a single iteration, the decoding process will be terminated immediately (CSC-ET\_0) or after additional n iterations (CSC-ET\_n) for better BER performance.

Since the updating of each APP message is more than once in a single iteration, such kind of serial satisfaction of parity-check equations always utilizes temporary hard-decisions of APP messages. It is not equal to the successful decoding criterion, in which all the parity-check equations should be satisfied at the same time. Fig.10 shows an particular case, in which the CSC-ET constraint is met but it is not correctly decoded.

Fig.10. CSC-ET criterion problem

In Fig.10 layers *i* and *j* are two check-nodes in PCM. Positions with numbers mean that there are connections between variable-nodes and check-nodes. The number '0' represents positive value of APP, while '1' represents negative one. Variable-node  $V_k$  connects to both of them. When the decoder processes on layer *i*

and layer *j* respectively, the parity-check equations *i* and *j* are both satisfied, but the hard-decision  $V_k$  is updated from '1' to '0'. Thus when the parity-check equation *j* is processed, the already satisfied parity-check equation *i* becomes unsatisfied. Through simulations we find that the above phenomenon does happen in the codeword terminated by CSC-ET and it will worsen the BER performance.

Similar situations will occur in CSC-ET criterion as HDA-ET. For successful decoding, there can be flipping hard-decisions which make the intermediate parity-check functions be unsuccessful. In such case, termination speed will be slowed down. Another case is as shown in Fig.10 that CSC-ET criterion may introduce extra errors.

Processing extra iterations when CSC-ET criterion is met can improve BER performance effectively since the sequential satisfaction of parity-check equations is a powerful indicator for codeword which can be successfully decoded. But it is still not equal to successful decoding, thus involves error-correcting performance loss.

## 3.2 Last-iteration Satisfaction Check Early Termination

## (LSC-ET) Scheme

By investigating the unsatisfied-constraint problem of CSC-ET, for layered decoder architecture we propose the last-iteration satisfaction check based early termination (LSC-ET) scheme. Unlike the previous schemes, the proposed one can terminate the decoding process without any BER performance loss. Moreover, compared with above two ET schemes, the proposed one achieves smaller average iteration times (AIT) which greatly influences the decoding throughput or power consumption.

The main idea of the proposed LSC-ET scheme is that the decoder executes the parity-check equations during (i+1)th iteration with hard-decisions generated from *ith* iteration. The decoding process is terminated only if all of the parity-check equations in a single iteration are satisfied. Otherwise it will be terminated after predefined

maximum iteration time. As the CSC-ET scheme, it verifies the parity-check equations layer by layer. The only difference is that LSC-ET utilizes hard-decisions generated from last iteration which CSC-ET uses the ones from current iteration.

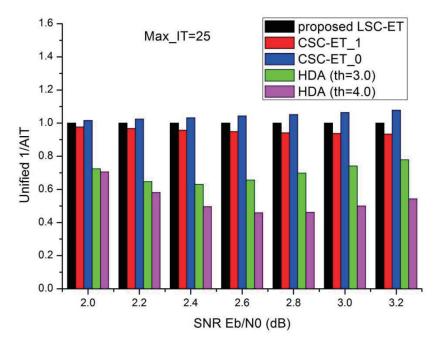

Since all of APP messages are updated more than once in a single iteration, we should memorize the last-updated hard-decisions in a single iteration. A simple example shown in Fig.11 explains how our method memorizes the last-updated values. Considering each row as a layer in the PCM, layers 0 to 5 are decoded sequentially. The '1's marked with bold red are last-updated positions for each variable-node.

| layer 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

|---------|---|---|---|---|---|---|---|---|---|---|---|---|

| layer 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 |

| layer 2 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 |

| layer 3 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 |

| layer 4 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| layer 5 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

Fig.11. Last-updated information in PCM

This method can ensure that all the hard-decisions of variable-nodes are only updated once and they are the latest values. The LSC-ET scheme is described as follows:

- a) Enlarge one bit (hard-decision bit) for all APP messages and initialize them as zero;

- b) When decoding to each layer, only for marked variable-nodes the hard-decision bits are updated according to updated APP messages;

- c) Without in the first iteration, process parity-check equations with the hard-decision bits in all layers;

- d) When all of parity-check equations are satisfied in a whole iteration, stop the decoding process.

For the satisfaction check in (i+1)th iteration, the last-updated hard-decisions obtained from *ith* iteration should be passed to the correct PEs, so they are combined with APP messages together for convenience. In real implementation, we enlarge the data bit-width of both APP memory and permutation network by one bit to achieve this function. Compared to additional parity-check logics, the increased hard-decision bits for APP messages occupy the most part of hardware overhead of LSC-ET scheme. For example in DVB-S2 decoders, the total memory overhead is no larger than 3% (8 bit quantization for APP messages) and it is the same level as HDA-ET, while hardware overhead of CSC-ET scheme can be ignored compared with our proposed one.