積層型機能性デバイスに向けた ハイブリッド接合技術に関する研究 Hybrid bonding technology for 3D integrated functional devices

2016年2月

仁村 将次 Masatsugu NIMURA 積層型機能性デバイスに向けた ハイブリッド接合技術に関する研究

Hybrid bonding technology for 3D integrated functional devices

# 2016年2月

早稲田大学大学院 先進理工学研究科 ナノ理工学専攻 マイクロシステム研究

仁村 将次 Masatsugu NIMURA

# 目次

| 目次                                                                            | I     |

|-------------------------------------------------------------------------------|-------|

| 図表一覧                                                                          | III   |

| 略語一覧                                                                          | VI    |

|                                                                               |       |

| 第1章 序論                                                                        |       |

| 1.1 研究背景                                                                      |       |

| 1.2 樹脂封止技術                                                                    |       |

| 1.3 本研究の目的                                                                    |       |

| 1.4 本論文の概要                                                                    | 6     |

| 1.5 参考文献                                                                      | 8     |

| 第 2 章 Lock and key 構造を用いたハイブリッド接合                                             | 19    |

| 第2章 Bock and key 構造を用いたパンプラフト複音                                               |       |

| 2.2 実験内容                                                                      |       |

| 2.2.1 Lock and key 構造の試作評価に用いたチップと基板                                          |       |

| 2.2.1 Eook and key 特遣のよれば 温にが、たりりりと塗板<br>2.2.2 チップへの Key 構造と基板への Lock 構造の作製方法 |       |

| 2.2.2 Lock and key 構造を用いたハイブリッド接合方法                                           |       |

| 2.3 結果と考察                                                                     |       |

| 2.3.1 チップへの Key 構造と基板への Lock 構造の作製結果                                          |       |

| 2.3.2 Lock and key 構造を用いたハイブリッド接合結果                                           |       |

| 2.4 結言                                                                        |       |

| 2.5 参考文献                                                                      |       |

|                                                                               | ····· |

| 第3章 Planar 構造を用いたハイブリッド接合                                                     | 29    |

| 3.1 緒言                                                                        | 29    |

| 3.2 実験内容                                                                      | 29    |

| 3.2.1 Planar 構造の試作評価に用いたチップと基板                                                | 29    |

| 3.2.2 チップと基板への Planar 構造の作製方法                                                 | 31    |

| 3.2.3 Planar 構造を用いたハイブリッド接合方法                                                 | 32    |

| 3.3 結果と考察                                                                     | 33    |

| 331 チップと基板への Planar 構造の作製結果                                                   | 33    |

| 3.3.2 Planar 構造を用いたハイブリッド接合結果     | 36        |

|-----------------------------------|-----------|

| 3.4 結言                            | 39        |

| 3.5 参考文献                          | 40        |

|                                   |           |

| 第4章 シングルミクロンピッチのバンプと樹脂で構成される Pla  | nar 構造を用  |

| いたハイブリッド接合                        | 42        |

| 4.1 緒言                            | 42        |

| 4.2 実験内容                          | 43        |

| 4.2.1 Planar 構造の試作評価に用いたシングルミクロンピ | ッチのバンプ    |

| を有するチップ                           | 43        |

| 4.2.2 シングルミクロンピッチのバンプを有するチップへの    | Planar 構造 |

| の作製方法                             | 44        |

| 4.2.3 シングルミクロンピッチのバンプと樹脂で構成される    | Planar 構造 |

| を用いたハイブリッド接合方法とその評価内容             | 47        |

| 4.3 結果と考察                         | 49        |

| 4.3.1 シングルミクロンピッチのバンプを有するチップへの    | Planar 構造 |

| の作製結果                             | 49        |

| 4.3.2 バンプと樹脂の表面段差構造のハイブリッド接合への    | 影響54      |

| 4.3.3 プラズマ表面処理の接合強度と接合界面への影響      | 56        |

| 4.4 結言                            | 60        |

| 4.5 参考文献                          | 61        |

|                                   |           |

| 第5章 結論と今後の展望                      | 64        |

| 5.1 結論                            | 64        |

| 5.2 今後の展望                         | 66        |

| 5.3 参考文献                          | 67        |

|                                   |           |

| 謝辞                                | 69        |

|                                   |           |

| 業績一覧                              | 70        |

# 図表一覧

| 第 | 1章                                                  |            |

|---|-----------------------------------------------------|------------|

| 図 | 1.1. バンプの微細化の流れ                                     | 2          |

| 図 | 1.2. キャピラリーアンダーフィル工法と先塗布工法の課題                       | 4          |

| 図 | 1.3. ハイブリッド接合技術                                     | 5          |

| 図 | 1.4. 本論文の概要                                         | 7          |

| 第 | 2 章                                                 |            |

| 図 | 2.1. Lock and key 構造の試作評価に用いたチップと基板の(a)設計図とう        | <b></b> ピ学 |

|   | 顕微鏡画像、(b)SEM 画像、(c)Au バンプ表面の AFM 画像                 | .15        |

| 図 | 2.2. 樹脂の粘度と温度の関係[1]                                 | .17        |

| 図 | 2.3. Lock and key 構造の設計値                            | .17        |

| 図 | 2.4. チップへの Key 構造の作製工程                              | .18        |

| 図 | 2.5. 基板への Lock 構造の作製工程                              | .18        |

| 図 | 2.6. Lock and key 構造を用いたハイブリッド接合方法                  | .20        |

| 図 | 2.7. Key 構造の作製工程における樹脂のスピンコート後の Au バンプ上の            |            |

|   | 硬化樹脂の断面 SEM 画像                                      | .21        |

| 図 | 2.8. Key 構造の作製工程における未硬化樹脂の熱加圧後の Au バンプとデ            |            |

|   | 化樹脂の断面 SEM 画像                                       | .21        |

| 図 | 2.9. Key 構造の作製工程における $O_2$ プラズマ照射後の $Au$ バンプと未列     | 更化         |

|   | 樹脂の SEM 画像、及び Au バンプ表面を拡大した SEM 画像                  | .21        |

| 図 | 2.10. Lock 構造の作製工程における $O_2/CHF_3$ プラズマ照射後の $Au$ バン | ノブ         |

|   | と硬化樹脂の SEM 画像、及び Au バンプ表面を拡大した SEM 画像               | .22        |

| 図 | 2.11. Lock 構造の作製工程における $O_2$ プラズマ照射後の $Au$ バンプと     | 更化         |

|   | 樹脂の SEM 画像、及び Au バンプ表面を拡大した SEM 画像                  | .22        |

| 図 | 2.12. Key 構造を作製したチップと Lock 構造を作製した基板を接合した           | き試         |

|   | 料の電気抵抗測定結果                                          | .24        |

| 図 | 2.13. Key 構造を作製したチップと Lock 構造を作製した基板を接合した           | き試         |

|   | 料の C-SAM 画像                                         | .25        |

| 図 | 2.14. Key 構造を作製したチップと Lock 構造を作製した基板を接合した           | き試         |

|   | 料のシェアテスト後の破断面の光学顕微鏡画像                               | .25        |

| 図   | 2.15. Key 構造を作製したチップと Lock 構造を作製した基板を接合した                |     |

|-----|----------------------------------------------------------|-----|

|     | 料の断面 SEM 画像                                              | .26 |

| 第   | 3章                                                       |     |

| 図   | 3.1. Planar 構造の試作評価に用いたチップと基板の(a)設計図と(b)SEM像             |     |

| 図   | 3.2. チップと基板への Planar 構造の作製方法                             |     |

|     | 3.3. Planar 構造を用いたハイブリッド接合方法                             |     |

| 図   | 3.4. 樹脂の各硬化状態をパラメータとした CMP の研磨量と時間の関係.                   | .34 |

| 図   | 3.5. チップへの Planar 構造の作製工程における CMP 後の未硬化樹脂と               | Au  |

|     | バンプの SEM 画像                                              | .34 |

| 図   | 3.6. 基板への Planar 構造の作製工程における CMP 後の半硬化樹脂と                | Au  |

|     | バンプの SEM 画像                                              | .35 |

| 図   | 3.7. (a)CMP 前の Au バンプ表面、(b)CMP 後のチップの Au バンプ表面           | 面、  |

|     | 及び(c)CMP 後の基板の Au バンプ表面の AFM 画像                          | .35 |

| 図   | 3.8. Planar 構造を作製したチップと基板を接合した試料の電気抵抗測器                  |     |

|     | 果                                                        |     |

|     | 3.9. Planar 構造を作製したチップと基板を接合した試料の C-SAM 画像               |     |

|     | 3.10. シェア強度測定で破壊されたチップと基板の画像                             |     |

| 図   | 3.11. Planar 構造を作製したチップと基板を接合した試料の断面 SEM 🗉               |     |

|     |                                                          |     |

| 凶   | 3.12. Planar 構造を作製したチップと基板を接合した試料の Au バンプ                |     |

|     | 界面の SEM 観察結果                                             | .39 |

| 绺   | 4章                                                       |     |

| ,,, | 4.1. 8 μm ピッチの Sn/Cu バンプの SEM 画像                         | 11  |

|     | 4.1. SiO <sub>2</sub> フィラー含有樹脂の粘度と温度の関係[2]               |     |

|     | 4.3. Sn/CuバンプとSiO <sub>2</sub> フィラー含有樹脂で構成されるPlanar 構造の作 |     |

|     | 方法                                                       |     |

| 図   | 4.4. Sn/CuバンプとSiO <sub>2</sub> フィラー含有樹脂で構成されるPlanar 構造を作 |     |

|     | したチップと Cu 膜を形成した基板のハイブリッド接合方法                            |     |

| 図   | $4.5.~{ m SiO}_2$ フィラー含有樹脂をスピンコートしたチップの ${ m Sn/Cu}$ バンス |     |

|     | SiO <sub>2</sub> フィラー含有樹脂の SEM 画像                        |     |

| 図   | $4.6.~SiO_2$ フィラー含有樹脂をスピンコートしたチップを CMP した後               |     |

|                                                  | Sn/Cu バンプと SiO <sub>2</sub> フィラー含有樹脂の SEM 画像51                                                 |

|--------------------------------------------------|------------------------------------------------------------------------------------------------|

| 図                                                | 4.7. CMP で研磨した後に $O_2/CHF_3$ プラズマを照射したチップの $Sn/Cu$ バ                                           |

|                                                  | ンプと SiO <sub>2</sub> フィラー含有樹脂の SEM 画像(O <sub>2</sub> /CHF <sub>3</sub> プラズマ照射時の O <sub>2</sub> |

|                                                  | と CHF <sub>3</sub> のガス流量は(a)5 sccm と 20 sccm、(b)10 sccm と 10 sccm、及び                           |

|                                                  | (c)20 sccm $\geq$ 5 sccm)                                                                      |

| 図                                                | 4.8. CMP で研磨した後に $O_2/CHF_3$ プラズマを照射したチップの $Sn/Cu$ バ                                           |

|                                                  | ンプと $\mathrm{SiO}_2$ フィラー含有樹脂の表面段差値の関係 $(\mathrm{O}_2/\mathrm{CHF}_3$ プラズマ照射                   |

|                                                  | 時の $O_2$ と $CHF_3$ のガス流量は $5$ $sccm$ と $20$ $sccm、10 sccmと10 sccm、及$                           |

|                                                  | び 20 sccm と 5 sccm)                                                                            |

| 図                                                | 4.9. $O_2/CHF_3$ プラズマの照射時間に対する $Sn/Cu$ バンプと $SiO_2$ フィラー含                                      |

|                                                  | 有樹脂の表面段差値の関係 $(O_2/CHF_3$ プラズマ照射時の $O_2$ と $CHF_3$ のガス流                                        |

|                                                  | 量は 10 sccm と 10 sccm)53                                                                        |

| 図                                                | 4.10. $O_2$ /CHF $_3$ プラズマを照射した後の $S_n$ /Cu バンプと $S_iO_2$ フィラー含有                               |

|                                                  | 樹脂の SEM 画像53                                                                                   |

| 図                                                | 4.11. Sn/Cu バンプと SiO $_2$ フィラー含有樹脂の表面段差構造を作製したチ                                                |

|                                                  | ップを基板へ接合した試料の断面 SEM 画像(接合したチップの表面段差値 c                                                         |

|                                                  | は 50 nm 以下、200 nm、及び 400 nm)54                                                                 |

| 図                                                | 4.12. 接合時の最終到達温度を(a) 80 °C、(b) 100 °C、(c) 130 °C、(d) 200 °C、                                   |

|                                                  | (e) 260 °C で接合した試料の C-SAM 画像55                                                                 |

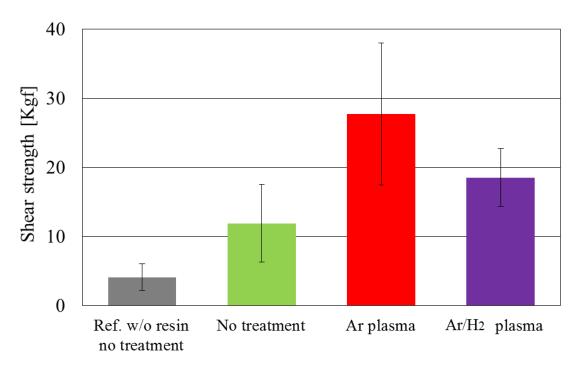

| 図                                                | $4.13$ . 未処理、 $Ar$ プラズマ表面処理、及び $Ar/H_2$ プラズマ表面処理をしたチ                                           |

|                                                  | ップと基板を接合した試料のシェア強度の測定結果57                                                                      |

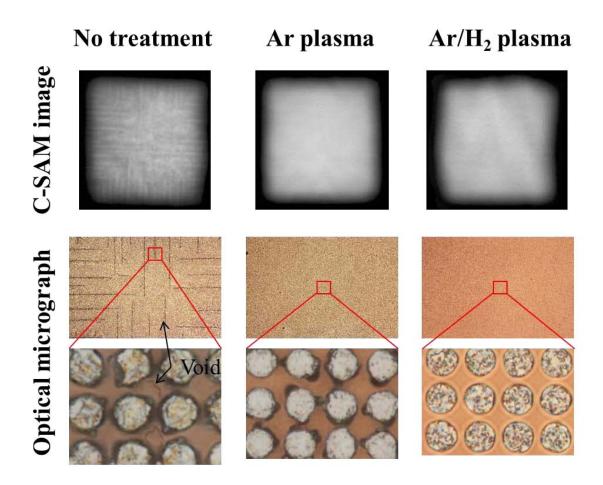

| 図                                                | $4.14$ . 未処理、 $Ar$ プラズマ表面処理、及び $Ar/H_2$ プラズマ表面処理をしたチ                                           |

|                                                  | ップと基板を接合した試料における $\mathrm{SiO}_2$ フィラー含有樹脂と $\mathrm{Cu}$ 膜の接合                                 |

|                                                  | 部の観察結果58                                                                                       |

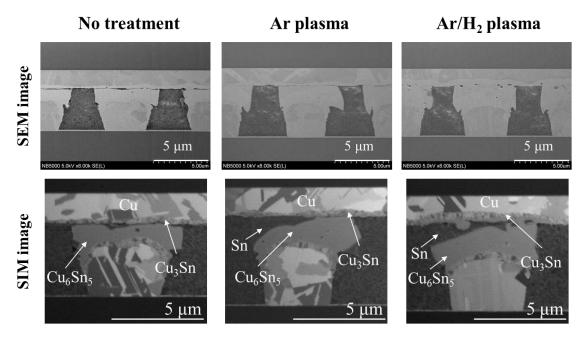

| 図                                                | $4.15$ . 未処理、 $Ar$ プラズマ表面処理、及び $Ar/H_2$ プラズマ表面処理をしたチ                                           |

|                                                  | ップと基板を接合した試料の断面 SEM 画像と断面 SIM 画像59                                                             |

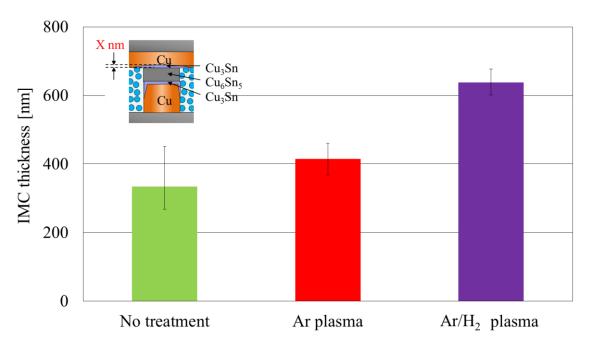

| 図                                                | $4.16$ . 未処理、 $Ar$ プラズマ表面処理、及び $Ar/H_2$ プラズマ表面処理をしたチ                                           |

|                                                  | ップと基板を接合した試料の Sn/Cu バンプと Cu 膜の接合界面に生成した                                                        |

|                                                  | IMC 膜厚の測定結果59                                                                                  |

|                                                  |                                                                                                |

| \ <del>\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\</del> |                                                                                                |

|                                                  | 5 章<br>5.1. チップ積層方法とウェハ積層方法の比較[8]                                                              |

# 略語一覧

AFM Atomic force microscope

CCP Capacitive coupled plasma

CMP Chemical mechanical polishing

CMOS Complementary metal-oxide semiconductor

CPU Central processing unit

DRAM Dynamic random access memory

FIB Focused ion beam

IMC Intermetallic compounds

IoT Internet of things

TSV Through silicon via

Rms Root mean square

SAM Scanning acoustic microscope SEM Scanning electron microscope

SIM Scanning ion microscope

LSI Large-scale integrated circuit

# 第1章 序論

#### 1.1 研究背景

従来の半導体デバイスの性能はムーアの法則に従ってトランジスタやコンデンサなどの素子を微細化することで向上されてきた[1]。しかし、その微細化は物理的限界に近づいており、従来のペースでの高性能化や低消費電力化が困難となりつつある。

近年 CPU(Central processing unit)と DRAM(Dynamic random access memory)の微細化技術に進歩の差が生じたことが原因で製品の性能向上が抑制されている問題、いわゆるメモリウォール問題が生じている[2]。CPUの演算能力は、微細化によるトランジスタの高密度化とシングルコアからマルチコアにすることで向上されてきた[3]。一方、DRAM の性能については、コンデンサの微細化に性能の律速要因があり、データ転送速度の指標であるバンド幅の向上と低消費電力化の両立が課題となっている。それでもなお、IoT(Internet of things)時代[4]に向けた通信技術や情報処理技術の今後の発達のためには半導体デバイスの高性能化、低消費電力化が必須となっている。

継続的な高性能化を達成する方法の 1 つとして、TSV(Through silicon via) を利用したデバイスの 3 次元積層化が注目されている[5-7]。ロジック上に DRAM を複数枚積層する 3 次元メモリでは、TSV による接続で従来に比べて広いバンド幅を実現できるためデータ転送速度の更なる向上や低消費電力化を達成できる[8-10]。また一方で、従来のノイマン型コンピューティングとは異なるアプローチとして、非ノイマン型のニューロコンピューティングが提案されている[11]。これは脳のニューロンの演算と記憶機能を模倣したコアを多数用いることで高効率に情報を処理し、超低消費電力化や並列処理を実現する。今後、脳の三次元的なネットワークを再現するために、シングルミクロンピッチレベルの電極の接続が必要とされている[12, 13]。

スマートフォンや車への普及が著しい CMOS(Complementary metal-oxide semiconductor)イメージセンサーでは、センサーとロジック、さらに DRAM を積層することで小型化、低ノイズ化、広ダイナミックレンジ化が実現されている[14, 15]。 さらに、高速移動する被写体撮影時のローリングシャッター歪みを解消するグローバルシャッター機能の実現[16]や次世代の高画質放送に向けた画素レベルの接続も研究されている[17]。加えて、自律知能ロボットなどへの搭

載に向けた脳型の視覚積層デバイスも提案されている[18, 19]。

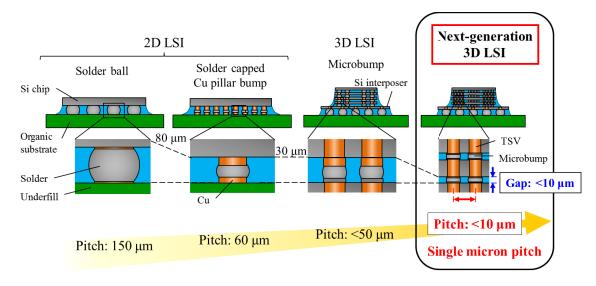

上記の背景の下、2 次元に集積化された半導体デバイスを 3 次元に積層することで従来の性能限界を打破し、更なる高性能デバイスの実現を期待できる。今後の 3 次元積層デバイスの継続的な進化を支えるためにはバンプのピン数増加とファインピッチ化に対応した積層技術の確立が必須である。図 1.1 に LSI(Large-scale integrated circuit)におけるバンプの微細化の流れを示す。従来の 2 次元 LSI のハイエンド製品では、はんだボールから Cu ピラーはんだバンプへ代わり、バンプのピッチは  $150~\mu m$  から  $60~\mu m$  へ減少している。3 次元 LSI では  $50~\mu m$  以下へとバンプのピッチの減少が進んでいる。さらに、次世代の 3 次元 LSI の実現には  $10~\mu m$  以下のピッチのバンプの接合が要求されるため、Si チップ間隔も  $10~\mu m$  以下にスケーリングする必要が生じる。そこで、本研究では、次世代の積層型機能性デバイスに向けたシングルミクロンピッチのバンプの接合と Si チップ間の樹脂封止を実現する技術に取り組んだ。

図 1.1. バンプの微細化の流れ

## 1.2 樹脂封止技術

従来の2次元LSIでは、デバイス素子が作製されたSiチップは、インターポーザーとしての有機基板の上にバンプで接合される。この有機基板のインターポーザーはSiチップとマザーボード間のバンプのピッチを変換する役割を果たす。また、3次元LSIにおいては、まず有機基板の上にインターポーザーとしてのSi基板がバンプで接合され、さらにその上に、複数枚のSiチップがバンプで接合される。このSi基板のインターポーザーはSiチップと有機基板間のピッ

チを変換する役割を果たす。これらを接合した後に、Si チップと有機基板間、Si チップと Si 基板間、及び積層した Si チップ間の隙間には、従来、アンダーフィルと呼ばれる樹脂が充填される。この樹脂は、Si チップと有機基板の熱膨張係数の差や Si チップ自体の反りで生じるバンプ接続部への応力を緩和する働きがあり、バンプ接合部の破断を防止する役割を果たす。また、バンプ接合部の腐食の防止や外力からの保護などの役割も果たす。すなわち、樹脂封止技術はデバイスを製品化する上で信頼性を保証するために必須の技術である。

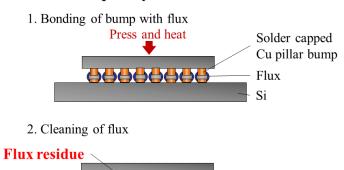

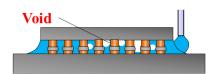

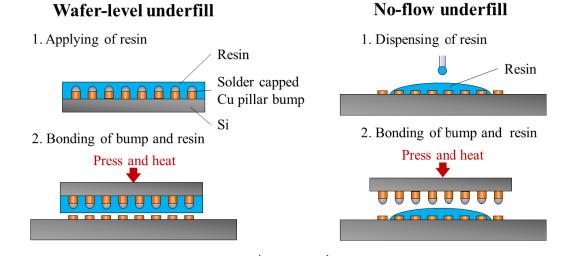

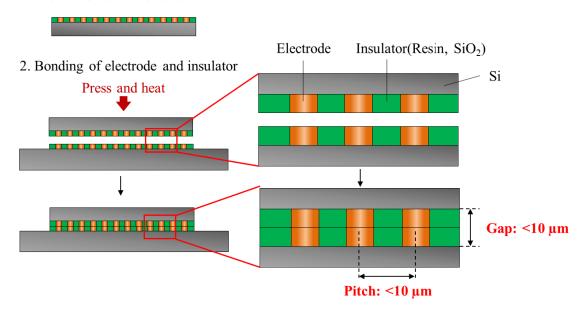

次に、これまでに提案されている樹脂封止技術とその問題について述べる。 従来、フラックスを用いてはんだを接合した後に樹脂をチップ周囲に塗布し、 毛細管力を利用してチップと基板、チップ間に樹脂を注入するキャピラリーア ンダーフィル工法が用いられている[20,21]。しかし、シングルミクロンピッチ のバンプの接合を必要とする次世代の積層デバイスでは、Si チップ間隔が 10 um 以下になるため、従来のフラックス洗浄や毛細管力を利用した樹脂注入自体 が困難とされ、図 1.2 に示すようにフラックス残渣やボイドの発生が問題となる。 積層デバイスがパッケージ化されて製品として使用される時に、フラックス残 渣によるバンプの接合部の腐食や、ボイドを起点とした樹脂剥離やバンプ接合 部のクラック等が発生する可能性がある。キャピラリーアンダーフィルの発展 技術として、真空アンダーフィル技術が報告されている[22]。これは真空下でチ ップ周辺に樹脂を塗布した後、大気下に戻し、大気圧差で樹脂を注入してボイ ドの発生を低減させる技術である。しかし、この技術においてもフラックス残 渣の問題は解決されない。フラックス残渣を解決する技術には、フラックスの 代わりに蟻酸やH<sub>2</sub>ラジカル処理を用いたフラックスレス接合が研究されている [23]。一方、はんだの接合前に樹脂をチップまたは基板へ塗布し、はんだ接合と 樹脂封止を同時に行う先塗布工法も提案されている。ノーフローアンダーフィ ル工法[24]とウェハレベルアンダーフィル工法[25-28]である。ノーフローアン ダーフィルは基板に樹脂を滴下して接合する工法である。ウェハレベルアンダ ーフィルはウェハに樹脂を形成した後、ダイシングでチップ化してから接合す る工法である。これらの先塗布工法のメリットは、フラックス洗浄工程が不要 な点であるが、図 1.2 に示すようにはんだ接合部の樹脂の噛み込みが新たな問題 となる。接合界面の樹脂ははんだが濡れると同時に接合界面から押し出される が、バンプのピッチが減少するとバンプサイズも小さくなり、はんだの量も少 なくなることから樹脂の噛み込みの問題はさらに顕著になると考えられる。こ れらの従来の樹脂封止技術における問題を解決する 1 つの技術として、図 1.3 に示すハイブリッド接合技術が提案されている[29-40]。この接合技術は、チッ

プまたは基板の接合面において電極の周囲に有機または無機の絶縁膜を形成した構造を用いて電極と電極、及び絶縁膜と絶縁膜を同時に接合する技術であるため、シングルミクロンピッチのバンプ接合と Si チップ間の樹脂封止を実現する可能性がある。

#### Capillary underfill

# 3. Injection of underfill

図 1.2. キャピラリーアンダーフィル工法と先塗布工法の課題

Resin trapping

#### **Hybrid bonding**

1. Fabrication of flat structure

図 1.3. ハイブリッド接合技術

## 1.3 本研究の目的

これまでに提案されているハイブリッド接合では、電極と絶縁膜の表面段差を極力抑えた平坦構造が用いられている。平坦構造の作製方法には、CMP(Chemical mechanical polishing)によるダマシン工法[29-32]やダイヤモンドの刃による電極と樹脂の同時切削[33-36]が提案されている。CMPによるダマシン工法では、電極のディッシングやエロージョンのため完全に電極と絶縁膜の表面高さを揃えることは困難である。ディッシングは、電極と絶縁膜の研磨レートの差で電極部が過剰に研磨されて電極表面が絶縁膜表面よりも凹む現象である。エロージョンは、緻密な電極箇所において絶縁膜が過剰研磨される現象である。ダイヤモンドの刃による切削では、機械的に電極と樹脂の表面を削るため接合面にスクラッチや削り屑の付着が生じ、接合不良が発生する可能性がある。また、平坦構造を用いたハイブリッド接合方法では、Si 基板の歪みや接合装置のヘッドとステージの平行不良によって接合時の荷重の不均一が生じるため、電極と絶縁膜の接合部において未接合部が発生する問題がある。そこで、この問題を解決する方法に、バンプの塑性変形と未硬化状態の接着性樹

脂の可塑性によって接合時にバンプと樹脂の表面段差を吸収可能な接合構造を 新たに提案する。この構造に採用する未硬化樹脂は、常温で固体であり、加熱 すると粘度が低下して可塑性を示す。加えて、この構造を作製するために、未 硬化樹脂をバンプ周囲に形成する工法も新たに提案する。そして、この接合構 造設計と作製方法を確立し、シングルミクロンピッチのバンプと樹脂を同時に 接合するハイブリッド接合の実現を本研究の最終目的とする。

#### 1.4 本論文の概要

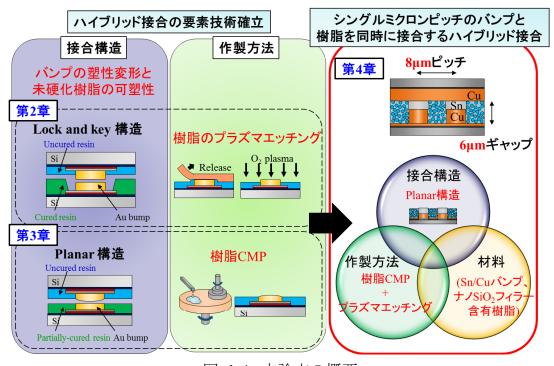

本論文の概要図を図 1.4 に示す。第 2 章と第 3 章では、ハイブリッド接合の要素技術である接合構造の設計とその作製方法の構築について述べる。第 4 章では、第 2 章と第 3 章で確立した接合構造の設計とその作製方法を応用し、さらに接合構造を構成する材料の視点も取り入れてシングルミクロンピッチのバンプと樹脂を同時に接合するハイブリッド接合の実現を目指した。

第1章「序論」では、まずデバイスの3次元積層化の背景とその応用について述べ、次世代の積層型機能性デバイスの実現に向けたシングルミクロンピッチのバンプの接合技術とチップ間の樹脂封止技術の必要性を論じた。次に、従来の樹脂封止技術の問題を解決する方法の1つとしてハイブリッド接合技術について述べた。そして、これまでに報告されているハイブリッド接合技術の問題を提起し、新たなハイブリッド接合技術の提案と本研究の目的について述べた。

第2章「Lock and key 構造を用いたハイブリッド接合」では、Au バンプの 塑性変形と未硬化樹脂の可塑性により Au バンプと樹脂の表面段差を吸収可能な Lock and key 構造を用いたハイブリッド接合技術を提案した。Lock and key 構造は接合時のバンプの位置ずれ防止の役割を果たす。この構造の作製方法にはバンプ上の樹脂をプラズマエッチングで除去する工法を提案した。

第3章「Planar 構造を用いたハイブリッド接合」では、樹脂を平坦化して得られる Planar 構造を用いたハイブリッド接合技術を提案した。Planar 構造は、Au バンプの塑性変形と未硬化樹脂の可塑性を利用して Au バンプと樹脂の表面段差を吸収する点において、第2章で述べた Lock and key 構造と類似するが、接合部が平坦な Planar 構造である点が大きく異なり、ファインピッチのバンプの接合構造にも対応できる特徴を有する。また、Planar 構造の作製には、チップと基板に樹脂をスピンコートし、CMPで研磨する工法を提案した。この作製

方法は工程数が少なく、汎用性が高い CMP 技術を用いるため量産化を可能とする。

第4章「シングルミクロンピッチのバンプと樹脂で構成される Planar 構造を用いたハイブリッド接合」では、8  $\mu$ m ピッチの Sn/Cu バンプと SiO2 フィラー含有樹脂で構成される Planar 構造を用いたハイブリッド接合技術を提案した。超高密度のバンプを有する接合構造に採用するバンプと樹脂の材料として、低圧で塑性変形する Sn をバンプ先端に用いた Sn/Cu バンプと、8  $\mu$ m ピッチの Sn/Cu バンプ間に充填可能なナノサイズの SiO2 フィラー含有樹脂を検討した。接合構造の作製方法には、第2章と第3章で確立した要素技術を応用して SiO2 フィラー含有樹脂の CMP と O2/CHF3 プラズマエッチングを組み合わせた工法を提案した。また、Planar 構造を作製したチップにおける Sn/Cu バンプと SiO2 フィラー含有樹脂の表面段差値と、Sn/Cu バンプと Cu 膜の接合界面への SiO2 フィラー含有樹脂の噛み込みの発生の関係を定量評価した。加えて、接合前のプラズマ表面処理の効果を評価するために、接合試料の接合強度測定、SiO2 フィラー含有樹脂と Cu 膜の接合部、及び Sn/Cu バンプの Sn と Cu 膜の接合部を解析した。

第 5 章「結論と今後の展望」では、本研究で得られた結果を総括し、結論と 今後の展望について述べた。

図 1.4. 本論文の概要

#### 1.5 参考文献

- [1] S. Natarajan, et al., "A 14nm Logic Technology Featuring 2nd-Generation FinFET, Air-Gapped" Interconnects, Self-Aligned Double Patterning and a 0.0588 m<sup>2</sup> SRAM cell size", Proceedings of IEEE International Electron Devices Meeting, pp. 3.7.1-3.7.3, 2014.

- [2] Sung-Kye Park, "Technology scaling challenge and future prospects of DRAM and NAND flash memory", Proceedings of IEEE International Memory Workshop, pp. 1-4, 2015.

- [3] P. Brofman, "IBM's packaging Technology Roadmap and the Collaboratory approach to Advanced Packaging Development", Proceedings of International Conference on Electronics Packaging, pp. 1-6, 2009.

- [4] Andrea Zanella, Nicola Bui, Angelo Castellani, Lorenzo Vangelista, and Michele Zorzi, "Internet of Things for Smart Cities", IEEE Internet of things journal, Vol. 1, No. 1, pp. 22-32, 2014.

- [5] Mitsumasa Koyanagi, Hiroyuki Kurino, Kang Wook Lee, Katsuyuki Sakuma, Nobuaki Miyakawa, Hikotaro Itani, "Future System-on-Silicon LSI Chips", IEEE Micro, Vol. 18, No. 4, pp. 17-21, 1998.

- [6] 佐久間克幸, "三次元集積化技術の開発動向," IEEJ Trans. SM, Vol.131, No.1, pp.19-25, 2011.

- [7] システムインテグレーション実装技術委員会, "2.5D/3D 積層デバイスの業界動向と技術課題", エレクトロニクス実装学会誌, Vol. 15, No. 1, pp. 34-37, 2012.

- [8] Uksong Kang, et al., "8 Gb 3-D DDR3 DRAM Using Through-Silicon-Via Technology", IEEE Journal of Solid-State Circuits, Vol. 45, No. 1, pp. 111-119, 2010.

- [9] Dong Uk Lee, Kyung Whan Kim, Kwan Weon Kim, Kang Seol Lee, Sang Jin Byeon, Jae Hwan Kim, Jin Hee Cho, Jaejin Lee, and Jun Hyun Chun, "A 1.2 V 8 Gb 8-Channel 128 GB/s High-Bandwidth Memory (HBM) Stacked DRAM With Effective I/O Test Circuits", IEEE Journal of Solid-State Circuits, Vol. 50, No. 1, pp. 191-202, 2015.

- [10] Joe Jeddeloh, and Brent Keeth, "Hybrid Memory Cube New DRAM Architecture Increases Density and Performance", Symposium on VLSI

- Technology Digest of Technical Papers, pp. 87-88, 2012.

- [11] Filipp Akopyan, et al., "TrueNorth: Design and Tool Flow of a 65 mW 1 Million Neuron Programmable Neurosynaptic Chip", IEEE transaction on Computer-Aided Design of Integrated Circuits and Systems, Vol. 34, No. 10, pp. 1537-1557, 2015.

- [12] Yasumitsu Orii, "Future packaging and required interposer technologies for cognitive computing devices" CPMT Seminar of the 64<sup>th</sup> Electronic Components and Technology Conference, 2014.

- [13] Kuniaki Sueoka, Sayuri Kohara, Akihiro Horibe, Fumiaki Yamada, Hiroyuki Mori, and Yasumitsu Orii, "Fine-pitch Solder Joining for High Density Interconnection", Proceedings of International Conference on Electronics Packaging, pp. 600-603, 2014.

- [14] Shunichi Sukegawa, et al., "A 1/4-inch 8Mpixel Back-Illuminated Stacked CMOS Image Sensor", IEEE International Solid-State Circuits Conference, pp. 484-485, 2013.

- [15] http://www.sony.jp/CorporateCruise/Press/201506/15-0626/

- [16] Jun Aoki, et al., "A Rolling-Shutter Distortion-Free 3D Stacked Image Sensor with -160dB Parasitic Light Sensitivity In-Pixel Storage Node", IEEE International Solid-State Circuits Conference, pp. 482-483, 2013.

- [17] 後藤正英, 萩原啓, 井口義則, 大竹浩, "画素並列信号処理を行う撮像デバイスの実現に向けた 3 次元集積回路の作製", NHK 技研 R&D, No. 153, 2015.

- [18] Makoto Motoyoshi, Junichi Takanohashi, Takafumi Fukushima, Yasuo Arai, and Mitsumasa Koyanagi, "Stacked SOI Pixel Detector using Versatile Fine Pitch μ-Bump Technology", Proceedings of 3D System Integration Conference, 2012.

- [19] Makoto Motoyoshi, Kohki Yanagimura, Junichi Takanohashi, Mariappan Murugesan, Masahiro Aoyagi, and, Mitsumasa Koyanagai, "Three-Dimensional Integration Technology for Sensor Application Using 5-μm-Pitch Au Cone Bump Connections", Proceedings of the 65<sup>th</sup> Electronic Components and Technology Conference, pp. 1365-1370, 2015.

- [20] Sejin Han, and K. K. Wang, "Analysis of the flow of encapsulant during underfill encapsulation of flip-chips," IEEE Transactions on components, packaging, and manufacturing technologies, Vol. 20, No. 4, pp. 424-591, 1997.

- [21] Yoshihiro Tomita, Tadahiro Morifuji, Tatsuya Ando, Masamoto Tago, Ryoichi Kajiwara, Yoshihiko Nemoto, Tomonori Fujii, Yoshifumi Kitayama, and Kenji Takahashi, "Advanced Packaging Technologies on 3D Stacked LSI utilizing the Micro Interconnections and the Layered Microthin Encapsulation", Proceedings of the 51st Electronic Components and Technology Conference, 2001.

- [22] Katsuyuki Sakuma, Sayuri Kohara, Kuniaki Sueoka, Yasumitsu Orii, Mikio Kawakami, Kazuo Asai, Yoshikazu Hirayama, and John U Knickerbocker, "Development of vacuum underfill technology for a 3D chip stack", Journal of Micromechanics and Microengineering, Vol. 21, 035024, 2011.

- [23] K. Sakuma, K. Toriyama, H. Noma, K. Sueoka, N. Unami, J. Mizuno, S. Shoji, and Y. Orii, "Fluxless bonding for fine-pitch and low-volume solder 3-D interconnections", Proceedings of the 61<sup>st</sup> Electronic Components and Technology Conference, pp. 7-13, 2011.

- [24] Satomi Kawamoto, Osamu Suzuki, and Yukinari Abe, "The effect of filler on the solder connection for no-flow underfill", Proceedings of the 56<sup>th</sup> Electronic Components and Technology Conference, pp. 479-484, 2006.

- [25] Jae-Woong Nah, Michael A. Gaynes, and Claudius Feger, "Development of wafer level underfill materials and assembly processes for fine pitch Pb-free solder flip chip packaging", Proceedings of the 63<sup>th</sup> Electronic Components and Technology Conference, pp. 1015-1022, 2011.

- [26] Akihiro Horibe, and Fumiaki Yamada, "Advanced 3D Chip Stack Process for Thin Dies with Fine Pitch Bumps using Pre-applied Inter Chip Fill", Proceedings of 3D System Integration Conference, 2009.

- [27] Toshihisa Nonaka, Koichi Fujimaru, Akira Shimada, Noboru Asahi, Yoshiko Tatsuta, Hiroyuki Niwa, and Yasuko Tachibana, "Wafer and/or chip bonding adhesives for 3D package", Proceedings of IEEE CPMT Symposium, pp. 1-4, 2010.

- [28] Yu-Min Lin, Chau-Jie Zhan, Kuo-Shu Kao, Chia-Wen Fan, Su-Ching Chung, Yu-Wei Huang, Shin-Yi Huang, Jing-Yao Chang, Tsung-Fu Yang, John H. Lau, and Tai-Hung Chen, "Low Temperature Bonding using Non-conductive Adhesive for 3D Chip Stacking with 30 μm-Pitch Micro Solder Bump Interconnections", Proceedings of the 62<sup>nd</sup> Electronic

- Components and Technology Conference, pp. 1656-1661, 2012.

- [29] Akitsu Shigetou, Toshihiro Itoh, Kanako Sawada, and Tadatomo Suga, "Bumpless Interconnect of 6 μm-Pitch Cu Electrodes at Room Temperature", IEEE transactions on advanced packaging, Vol. 31, No. 3, pp. 473-478, 2008.

- [30] J. J. McMahon, E. Chan, S. H. Lee, R. J. Gutmann, and J.-Q. Lu, "Bonding interfaces in wafer-level metal/adhesive bonded 3D integration", Proceedings of the 58<sup>th</sup> Electronic Components and Technology Conference, pp. 871-878, 2008.

- [31] P. Enquist, G. Fountain, C. Petteway, A. Hollingsworth, and H. Grady, "Low Cost of Ownership Scalable Copper Direct Bond Interconnect 3D IC Technology for Three Dimensional Integrated Circuit Applications", Proceedings of 3D System Integration Conference, 2009.

- [32] Mayu Aoki, Kazuyuki Hozawa, and kenichi Takeda, "Wafer-Level Hybrid Bonding Technology with Copper/Polymer Co-planarization", Proceedings of 3D System Integration Conference, 2012.

- [33] Taiji Sakai, Sakuyama Seiki, and Masataka Mizukoshi, "A New Flip Chip Bonding Method Using Ultra-Precision Cutting of Metal/Adhesive Layers", Proceedings of International Conference on Electronics Packaging, pp. 99-104, 2007.

- [34] F. Iker, T. Funaya, R.C. Teixeira, and W. Ruythooren, "Diamond Bit Cutting as Alternative to Polymer Patterning for 3D Interconnections Technologies", Proceedings of the 59<sup>th</sup> Electronic Components and Technology Conference, pp. 1284-1288, 2009.

- [35] Toshihisa Nonaka, Shoichi Niizeki, Noboru Asahi, and Koichi Fujimaru, "Low Temperature Touch Down and Suppressing Filler Trapping Bonding Process with a Wafer Level Pre-applied Underfilling Film Adhesive", Proceedings of the 62<sup>nd</sup> Electronic Components and Technology Conference, pp. 444-449, 2012.

- [36] Zhi-Cheng Hsiao, Cheng-Ta Ko, Hsiang-Hung Chang, Huan-Chum Fu, Chia-Wei Chiang, Chao-Kai Hsu, Wen-Wei Shen, and Wei-Chung Lo, "Cu/BCB hybrid bonding with TSV for 3D integration by using fly cutting technology", Proceedings of International Conference on Electronic Packaging and iMAPS All Asia Conference, pp. 834-837, 2015.

- [37] F. Liu, et al., "A 300-mm wafer-level three-dimensional integration scheme using tungsten through-silicon via and hybrid Cu-adhesive bonding", Proceedings of International Electron Devices Meeting, pp. 1-4, 2008.

- [38] K. N. Chen, T. M. Shaw, C. Cabral, Jr., and G. Zuo, "Reliability and structural design of a wafer-level 3D integration scheme with W TSVs based on Cu-oxide hybrid wafer bonding", Proceedings of International Electron Devices Meeting, pp. 2.4.1-2.4.4, 2010.

- [39] Jason D. Reed, Matthew Lueck, Chris Gregory, Alan Huffman, John M. Lannon, Jr., and Dorota Temple, "High Density Interconnect at 10 μm Pitch with Mechanically Keyed Cu/Sn-Cu and Cu-Cu Bonding for 3-D Integration", Proceedings of the 60<sup>th</sup> Electronic Components and Technology Conference, pp. 846-852, 2010.

- [40] C. T. Ko, et al., "Structural Design, Process, and Reliability of a Wafer-Level 3D Integration Scheme with Cu TSVs Based on Micro-bump/Adhesive Hybrid Wafer Bonding", Proceedings of the 62<sup>nd</sup> Electronic Components and Technology Conference, pp. 444-449, 2012.

# 第 2 章 Lock and key 構造を用いた ハイブリッド接合

#### 2.1 緒言

本章では、Au バンプの塑性変形と未硬化樹脂の可塑性により Au バンプと樹脂の表面段差を吸収可能な Lock and key 構造を用いたハイブリッド接合技術を提案する[1, 2]。

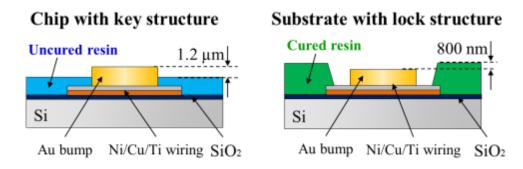

第1章で述べたハイブリッド接合の問題の1つである電極と絶縁膜の表面段差が原因で生じる電極間及び絶縁膜間の未接合の問題を解決することを目的として、Auバンプの塑性変形と未硬化樹脂の可塑性により段差を吸収可能なLock and key 構造を提案する。これらの構造は接合前のチップと基板に予め作製される。Key 構造はAuバンプと未硬化状態の接着性樹脂で構成され、Auバンプ表面が未硬化樹脂のそれよりも高い凸型の構造をとる。一方、Lock 構造はAuバンプと硬化樹脂で構成され、Auバンプ表面が硬化樹脂のそれよりも低い凹型の構造をとり、Key 構造との位置ずれ防止の役割も果たす[3-5]。未硬化樹脂は常温では固体で、加熱すると粘度が低下して可塑性を示す。この特性とAuバンプの塑性変形を利用することで、接合時にLock and key 構造のAuバンプと樹脂の表面段差が吸収される。

本章の研究を通して達成すべき課題は以下の通りである。第1に、Auバンプ上の未硬化樹脂または硬化樹脂を残渣なく除去可能なLock and key 構造の作製方法の構築である。第2に、Auバンプの接合界面への未硬化樹脂の流入を防ぐLock and key 構造の設計指針の確立である。

まず、Au バンプ上の樹脂を残渣なく除去する方法として、Key 構造の作製には、Au バンプ上の未硬化樹脂をフッ素樹脂フィルムで熱加圧した後に、樹脂を $O_2$  プラズマエッチング[6]する工法を提案する。Lock 構造の作製には、フォトリソグラフィーによるレジストマスク形成後に  $O_2$  と  $CHF_3$  の混合させた $O_2/CHF_3$  プラズマ[6]で樹脂をエッチングする工法を検討する。次に、Au バンプの接合界面への未硬化樹脂の流入防止のために、接合時の温度上昇前にチップと基板のAu バンプが接触する構造を設計し、この構造を用いたハイブリッド接合の有効性を検証する。

#### 2.2 実験内容

#### 2.2.1 Lock and key 構造の試作評価に用いたチップと基板

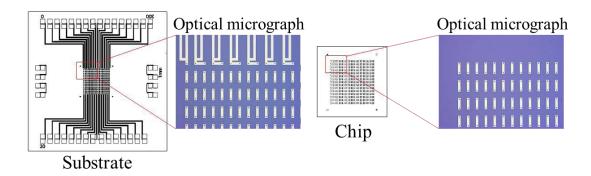

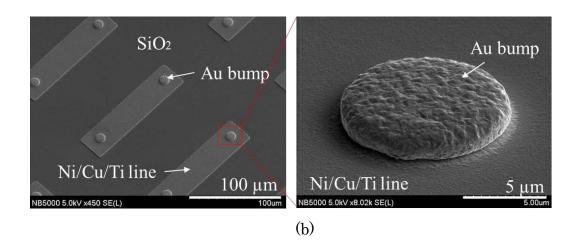

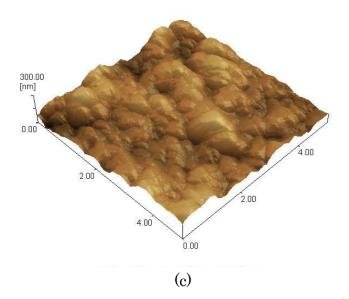

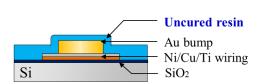

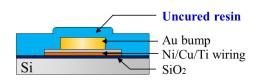

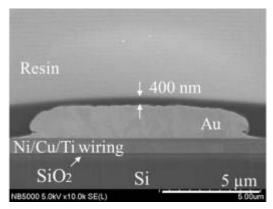

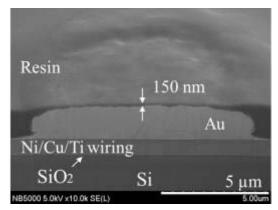

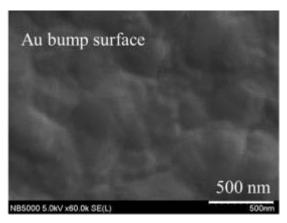

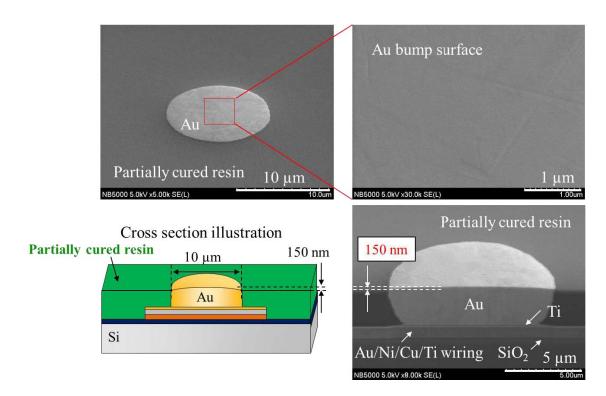

Lock and key 構造の試作評価用に作製したチップと基板の設計図と光学顕微鏡画像、SEM(Scanning electron microscope)(NB5000,株式会社日立ハイテクノロジーズ)画像、及び Au バンプ表面の AFM(Atomic force microscope) (SPM-9600、株式会社島津製作所)画像を図 2.1 に示す。チップと基板には、SiO2膜付きの Si 基板を用いた。Si 基板と SiO2膜の厚さは 525  $\mu$ m と 500 nm である。チップと基板には、電子ビーム蒸着で形成した Ni/Cu/Ti 配線の上に、電解めっきで Au バンプを形成した。Ni/Cu/Ti 配線の構成は、上から Ni、Cu、Ti であり、それぞれの膜厚は 200 nm、500 nm、30 nm である。Ni/Cu/Ti 配線はチップと基板を接合した際に Au バンプの全てが連結される配置とした。また、基板の周囲には電気抵抗測定用の四端子プローブを接触させるパッドを配置した。Au バンプの直径とピッチ、高さ、及び数は、10  $\mu$ m、100  $\mu$ m、2  $\mu$ m 、900 ピンである。AFM で測定した Au バンプ表面の表面粗さは、200 Rms (Root mean square)が 200 nm、200 Rz 200 Rz 200 Rz 200 Nm、200 Rz 200 Rz 200 Rz 200 Nm、200 Rz 200 Nm 200 Nm 200 Rz 200 Nm 200

(a)

図 2.1. Lock and key 構造の試作評価に用いたチップと基板の(a)設計図と光学 顕微鏡画像、(b)SEM 画像、(c)Au バンプ表面の AFM 画像

#### 2.2.2 チップへの Key 構造と基板への Lock 構造の作製方法

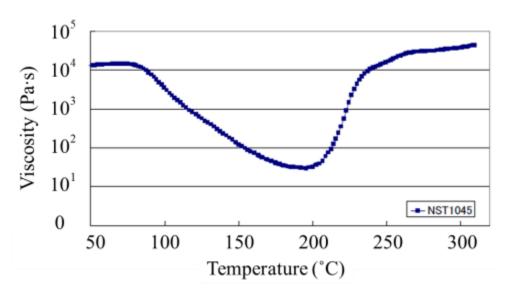

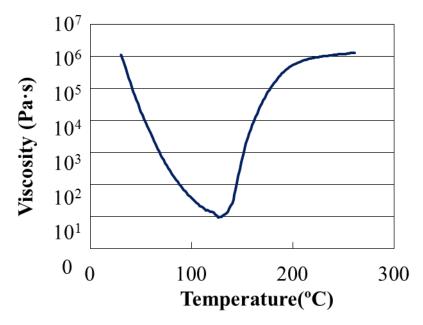

Lock and key 構造を作製するための樹脂には、熱硬化性樹脂(NST1045、日産化学工業株式会社)を使用した。この樹脂は、常温で固体であり、加熱すると粘度が低下して可塑性を示す。図 2.2 に樹脂の粘度と温度の関係のグラフを示す。この図より、常温から温度上昇につれて粘度が低下し、約 180°C で最低粘度となることが分かる。そして、約 180°C から樹脂の硬化が始まり粘度が上昇し、約 240°C で樹脂の硬化反応が進み粘度変化が小さくなることが分かる。

図 2.3 に Au バンプの接合界面への樹脂の流入を防止するために設計した Lock and key 構造を示す。Key 構造を作製したチップと Lock 構造を作製した 基板とを接合する際に、加熱で未硬化樹脂が溶融する前に Au バンプ間をあらか じめ接触させるために Key 構造の Au バンプと未硬化樹脂との表面段差を 1.2  $\mu m$ 、Lock 構造の Au バンプと硬化樹脂との表面段差を 800 nm とした。

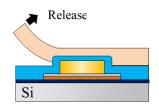

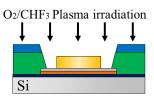

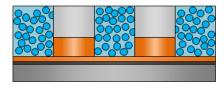

Key 構造の作製方法を図 2.4 に示す。まず、溶剤に溶かされた液体状の樹脂をチップにスピンコートし、100 °C、2 分間の条件で樹脂をベークした後、さらに 150 °C、2 分間の条件で樹脂をベークして溶剤を蒸発させた。樹脂の硬化開始温度は約 180°C であるため、このベーク後の樹脂は未硬化状態を維持する。次に、未硬化樹脂を塗布したチップ上にフッ素樹脂フィルムを載せて、真空下、150 °C、80 N、3 分間の条件で熱加圧を施した。この工程によって、Au バンプ上の樹脂を薄くすることができる。常温に戻して樹脂を固体にした後にフッ素樹脂フィルムを剥離した。最後に、CCP(Capacitive Coupled Plasma) (RIE-10NR、サムコ株式会社)で  $O_2$ プラズマを 3 分間照射し、バンプ上の樹脂を除去した。プラズマ照射時の真空度は 20 Pa、出力は 100 W、ガス流量は 20 sccm である。

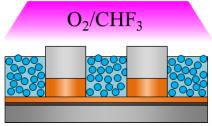

である。その後、アセトンでフォトレジストを除去した。最後に、Lock 構造の Au バンプと硬化樹脂の表面段差が 800 nm になるまで  $O_2$ プラズマで基板全面 の硬化樹脂をエッチバックした。Key 構造作製において未硬化樹脂はスピンコートで塗布されたため、チップ端の未硬化樹脂の膜厚は中央部のそれに比べて厚くなった。これによる接合時の片あたりの発生を防ぐため、Lock 構造の硬化 樹脂は基板中央部の 3 mm  $\times$  3 mm の範囲に作製した。

図 2.2 樹脂の粘度と温度の関係[1]

図 2.3. Lock and key 構造の設計値

#### 1. Spincoating of resin

3. Release of fluoropolymer film at room temperature

#### 2. Thermal compression of resin

4. O<sub>2</sub> plasma irradiation

図 2.4. チップへの Key 構造の作製工程

#### 1. Spincoating of resin

4. Etching of resin by O<sub>2</sub>/CHF<sub>3</sub> plasma irradiation

#### 2. Cure of adhesive

5. Removal of photoresist

#### 3. Photolithography

6. Etching of resin by O<sub>2</sub> plasma irradiation

図 2.5. 基板への Lock 構造の作製工程

### 2.2.3 Lock and key 構造を用いたハイブリッド接合方法

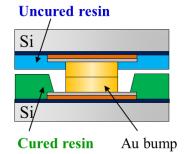

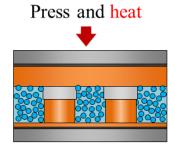

図 2.6 に Lock and key 構造を用いたハイブリッド接合方法を示す。フリップ チップボンダー(FC2000、東レエンジニアリング株式会社)を用いて、Lock and key 構造を作製したチップと基板を大気下で接合した。フリップチップボンダー のヘッドとステージの双方にはセラミックヒーターが付属している。チップと 基板は真空吸着によりそれぞれヘッドとステージに固定され、接合時にはヘッ ドが下降することによりチップと基板が加圧される。その際、接合前のチップ と基板には表面処理を施さなかった。まず、カメラの画像処理で Key 構造を作 製したチップと Lock 構造を作製した基板の双方のアライメントマークを検出 し、アライメントを行った。次に、ヘッドとステージの双方の温度を 30 °C、荷 重を 100 N、加圧時間を 5 秒間とする条件でチップと基板の Au バンプを接触 させた。次に、加圧を保持したままフリップチップボンダーのヘッドとステー ジの双方の温度を 150°C に昇温し、300 秒間保持した。この過程でチップの未 硬化樹脂は溶融して基板の硬化樹脂と接着し、Au バンプと樹脂の表面段差が吸 収される。最後に、ボンダーのヘッドとステージの双方の温度を 250°C に昇温 して、チップと基板の Au バンプの拡散接合[7-10]と樹脂の硬化を行った。その 後、接合された試料をホットプレート上で250 ℃、1 時間の条件でポストベー クし、樹脂を完全に硬化させた。

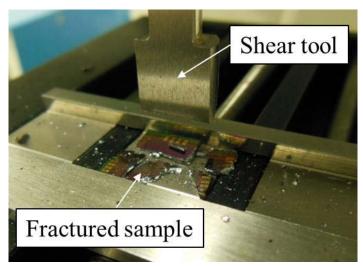

接合した試料を以下の計測方法により評価した。Au バンプ間の電気的な接続評価のために、Au バンプ及び Au バンプ間を連結する配線の電気抵抗を測定した。また、樹脂中に発生するボイドと接合強度の評価のために、超音波顕微鏡観察(SAM 300, PVA TePla Analytical Systems GmbH)とシェア強度測定(Dage 4000、ノードソン・アドバンスト・テクノロジー株式会社)を行った。シェア強度測定においてチップを側面から加圧するシェアツールの速度は  $50~\mu m/sec$  とした。シェアツール先端の基板表面からの高さは  $10~\mu m$  とした。さらに、Au バンプ、及び樹脂の接合界面を SEM で観察した。

#### 1. Contact of Au bump

### 2. Resin bonding

# 3. Au-Au bonding and resin cure

図 2.6. Lock and key 構造を用いたハイブリッド接合方法

### 2.3 結果と考察

#### 2.3.1 チップへの Key 構造と基板への Lock 構造の作製結果

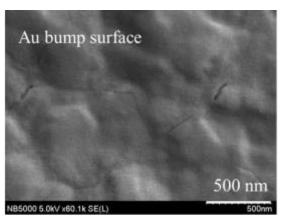

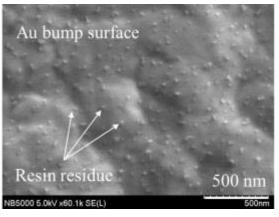

まず、チップへ Key 構造を作製した結果について述べる。図 2.7 に樹脂をチップにスピンコートした後の Au バンプ上の未硬化樹脂の断面 SEM 画像を示す。この SEM 画像より、Au バンプ上の未硬化樹脂の膜厚は 400 nm であったことが分かる。図 2.8 に、フッ素樹脂フィルムによってチップ上の未硬化樹脂を熱加圧した後の Au バンプ上の未硬化樹脂の断面 SEM 画像を示す。この SEM 画像は、Au バンプ上の未硬化樹脂の膜厚が、熱加圧前後で 400 nm から 150 nm へ減少したことを示している。図 2.9 に  $O_2$ プラズマ照射後の Au バンプと未硬化樹脂の SEM 画像、及び Au バンプ表面を拡大した SEM 画像を示す。Au バンプと樹脂の表面段差は  $1.2~\mu m$  であった。加えて、 $O_2$ プラズマ照射によって Au バンプ上の未硬化樹脂は Au バンプ表面に残渣なく除去されていたことが確認された。これらの観察結果は、Au バンプ上の樹脂の膜厚を薄くしたことで残渣の発生が抑えられたことを示している。

次に、基板へ Lock 構造を作製した結果について述べる。まず、 $O_2/CHF_3$ プラズマで硬化樹脂をエッチングしたときの結果を示す。図 2.10 に  $O_2/CHF_3$ プラズマ照射後の Au バンプと硬化樹脂の SEM 画像、及び Au バンプ表面を拡大した SEM 画像を示す。Au バンプと樹脂の表面段差は 800 nm であった。SEM による観察結果から、 $O_2/CHF_3$  プラズマ照射によって Au バンプ上の樹脂は残渣なく除去されたことが確認された。比較のため、図 2.11 に  $O_2$  プラズマ照射後の Au バンプと硬化樹脂の SEM 画像、及び Au バンプ表面を拡大した SEM 画像

図 2.7. Key 構造の作製工程における樹脂のスピンコート後の Au バンプ上の未硬化樹脂の断面 SEM 画像

図 2.8. Key 構造の作製工程における未硬化樹脂の熱加圧後の Au バンプと未硬化樹脂の断面 SEM 画像

図 2.9. Key 構造の作製工程における  $O_2$ プラズマ照射後の Au バンプと未硬化樹脂の SEM 画像、及び Au バンプ表面を拡大した SEM 画像

図 2.10. Lock 構造の作製工程における  $O_2/CHF_3$ プラズマ照射後の Au バンプと 硬化樹脂の SEM 画像、及び Au バンプ表面を拡大した SEM 画像

図 2.11. Lock 構造の作製工程における  $O_2$ プラズマ照射後の Au バンプと硬化樹脂の SEM 画像、及び Au バンプ表面を拡大した SEM 画像

を示す。プラズマ照射時の真空度は 20 Pa、出力は 100 W、 $O_2$ のガス流量は 20 sccm である。この SEM 画像は、 $O_2$ プラズマの場合、Au バンプの表面に無数の樹脂の残渣が発生したことを示している。これらの結果は、 $O_2$  のみのプラズマ照射では分解されなかった高結合エネルギーを持つ C-H や C=C などの分子が凝集して残渣になるのに対し、 $CHF_3$  を  $O_2$  に添加したプラズマ照射により、F の酸化力で高結合エネルギーの分子も分解することができたことを示している。

#### 2.3.2 Lock and key 構造を用いたハイブリッド接合結果

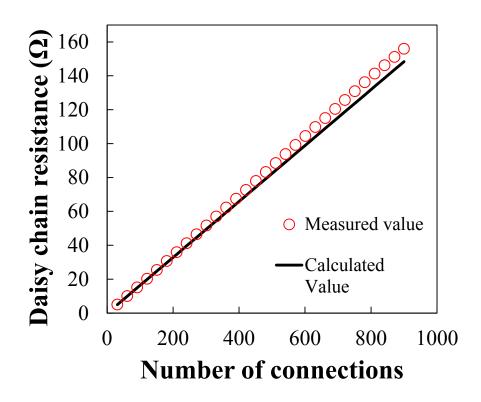

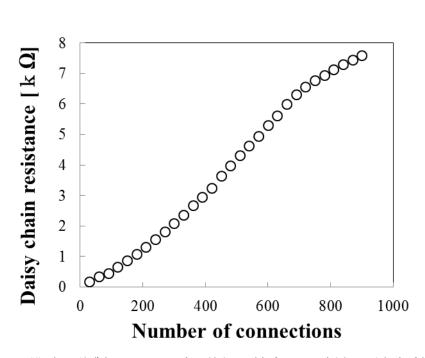

Key 構造を作製したチップと Lock 構造を作製した基板を接合した試料において、Au バンプの電気的な接続を評価するために、Au バンプ及びそれらを連結する配線の電気抵抗を四端子プローブで測定した。その電気抵抗の測定結果を図 2.12 に示す。チップと基板に形成した 900 ピンの Au バンプ全てが電気的に接続されていることを確認した。縦軸の抵抗値は Au バンプと Ni/Cu/Ti 配線の抵抗を全て含む。900 ピンの Au バンプと Ni/Cu/Ti 配線の全てを含む抵抗値の実測値と計算値はそれぞれ 154.8  $\Omega$  と 148.4  $\Omega$  であった。ここで、この抵抗値の誤差は Au バンプ接合界面の抵抗  $R_i$  であると仮定し、実測値と計算値の誤差値から接合試料のAu バンプの1個あたりの平均の接合面積率 P を式(2.1)と(2.2)で算出した。Au の比抵抗値  $\rho_a$  は 0.0221  $\Omega$ ・m を用いた。Au バンプの1個あたりの平均の接合所属でボイドが存在していることが示唆された。

$$R_{\rm m} = R_{\rm c} + R_{\rm i} = \rho_{\rm a} T_{\rm b} / S_{\rm m}$$

(2.1)

$$P = S_{m} / S_{c} = \rho_{a} T_{b} / S_{c} (R_{c} + R_{i})$$

(2.2)

P:接合面積率 [%]

S<sub>c</sub>: Au バンプの接合面積(計算値) [μm<sup>2</sup>]

S<sub>m</sub>: Au バンプの接合面積(実測値) [μm<sup>2</sup>]

$R_c$ :接合した Au バンプの抵抗値(計算値)  $[\Omega]$

$R_m$ :接合した Au バンプの抵抗値(実測値)  $[\Omega]$

$R_i: Au$  バンプの接合界面の抵抗値(実測値)  $[\Omega]$

$T_b: Au$  バンプの厚さ  $[\mu m]$   $\rho_a: Au$  の比抵抗値  $[\Omega \cdot m]$

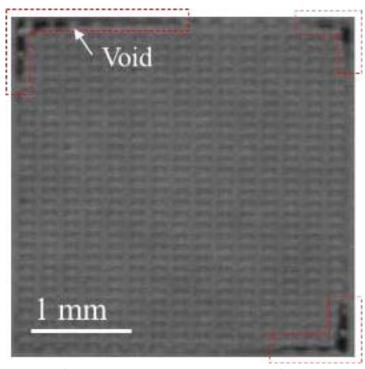

次に、Key 構造を作製したチップと Lock 構造を作製した基板を接合した試料における樹脂のボイド発生と接合強度の評価結果について述べる。まず、接合試料の樹脂接合層を超音波顕微鏡で撮影した C-SAM (Constant-depth mode Scanning Acoustic Microscope) 画像を図 2.13 に示す。300 MHz の超音波プローブを用いてチップ側から樹脂接合層を撮影した結果、樹脂接合部の周辺に欠陥が観察された。この欠陥が樹脂接合部の剥離の場合、その箇所では Au バンプの接合も破壊されるが、図 2.12 に示すようにチップと基板に形成した 900 ピン

の Au バンプ全てが電気的に接続されていた。したがって、その欠陥は樹脂接合部の剥離ではなく、樹脂不足で生じたボイドであると考えられる。また、接合試料のシェア強度は 38.6 MPa であった。図 2.14 にシェア強度の測定後のチップと基板の破断面を光学顕微鏡で観察した結果を示す。これは接合された未硬化樹脂と硬化樹脂は接合界面で剥離せず凝集破壊をしたため、それらの接合が強固であったことを示している。

次に、図 2.15 に接合試料の断面 SEM 画像を示す。Au バンプの接合界面では Au 原子の拡散が進行し、Au バンプ間で再結晶化[7, 11]した箇所が存在した。 ボイドが発生した原因には、Au バンプの表面粗さ[7]や Au 表面の有機物[9]が考えられる。また、未硬化樹脂と硬化樹脂の接合界面は観察されず、このことは 界面で架橋反応が生じて一体化したことを示している。

以上の接合結果は、Au バンプの接合界面への未硬化樹脂の流入防止のために、接合時の温度上昇前にチップと基板の Au バンプを接触させる構造設計が有効であることを示している。

図 2.12. Key 構造を作製したチップと Lock 構造を作製した基板を接合した試料の電気抵抗測定結果

図 2.13. Key 構造を作製したチップと Lock 構造を作製した基板を接合した試料の C-SAM 画像

図 2.14. Key 構造を作製したチップと Lock 構造を作製した基板を接合した試料のシェアテスト後の(a)チップと(a)基板の破断面の光学顕微鏡画像

図 2.15. Key 構造を作製したチップと Lock 構造を作製した基板を接合した試料の断面 SEM 画像

# 2.4 結言

本章では、Au バンプの塑性変形と未硬化樹脂の可塑性を利用することで Au バンプと樹脂の表面段差を吸収可能な Lock and key 構造を用いたハイブリッド接合技術について述べた。

まず、第1の課題である Au バンプ上の未硬化樹脂または硬化樹脂を残渣なく除去可能な Lock and key 構造の作製方法を構築した。Key 構造の作製には、Au バンプ上の未硬化樹脂をフッ素樹脂フィルムで熱加圧した後、未硬化樹脂を  $O_2$  プラズマエッチングする工法を提案した。Au バンプ上の未硬化樹脂を 150 nm まで薄くすることで  $O_2$  プラズマ照射により残渣なく除去することに成功した。また、Lock 構造の作製では、フォトリソグラフィーによるレジストマスク形成と  $O_2$ /CHF3 プラズマエッチングによって、Au バンプ上の硬化樹脂を残渣なく除去することに成功した。これらの結果は、膜厚が薄い場合には  $O_2$  プラズマ照射によって樹脂を残渣なく除去できることを示している。

次に、第2の課題である Au バンプの接合界面への未硬化樹脂の流入を防ぐ接

合構造の設計と試作評価で得られた結果について述べた。 ここでは、Key 構造の Au バンプと未硬化樹脂の表面段差は 1.2 μm とした。一方、Lock 構造の Au バンプと硬化樹脂の表面段差は 800 nm とし、接合時に Au バンプが樹脂よりも先に接触する構造を設計した。この Key 構造を作製したチップと Lock 構造を作製した基板を接合することで、900 ピン全ての Au バンプの電気的な接続が可能であることを実証した。また、接合試料の断面 SEM 観察結果から、Au バンプの接合界面では Au 原子の拡散が進行し、Au バンプ間で再結晶化した箇所が存在した。また、未硬化樹脂と硬化樹脂の接合界面は観察されず、それらの界面で架橋反応が生じ一体化したことと、ボイドのないことを確認した。これらの結果は、接合時の温度上昇前にチップと基板の Au バンプを接触させることで、Au バンプの接合界面への未硬化樹脂の流入を防止する構造設計が有効であることを示している。

以上の結果によって、 $O_2$ 及び  $O_2$ /CHF $_3$ プラズマエッチングによって Au バンプ上の未硬化樹脂及び硬化樹脂を除去できることを示し、加えて Au バンプの塑性変形と未硬化樹脂の可塑性により Au バンプと樹脂の表面段差を吸収する Lock and key 構造がハイブリッド接合に有効であることを示した。

### 2.5 参考文献

- [1] Masatsugu Nimura, Shigetou Akitsu, Katsuyuki Sakuma, Hiroshi Ogino, Tomoyuki Enomoto, Jun Mizuno and Shuichi Shoji, "Study on Hybrid Au-undefill resin Bonding Method with Lock-and-key structure for 3D Integration", IEEE transaction on Components, Packaging and Manufacturing Technology, Vol. 3, Issue. 4, pp. 558-565, 2013.

- [2] Masatsugu Nimura, Shigetou Akitsu, Katsuyuki Sakuma, Hiroshi Ogino, Tomoyuki Enomoto, Jun Mizuno and Shuichi Shoji, "Hybrid Au-Underfill Resin Bonding with Lock-and-Key Structure", Proceedings of the 62<sup>nd</sup> Electronic Components and Technology Conference, pp. 258-262, 2012.

- [3] F. Liu, et al., "A 300-mm wafer-level three-dimensional integration scheme using tungsten through-silicon via and hybrid Cu-adhesive bonding," Proceedings of International Electron Devices Meeting, 2008.

- [4] K. N. Chen, T. M. Shaw, C. Cabral, Jr., and G. Zuo, "Reliability and structural design of a wafer-level 3D integration scheme with W TSVs based on Cu-oxide hybrid wafer bonding", Proceedings of International

- Electron Devices Meeting, 2010.

- [5] Jason D. Reed, Matthew Lueck, Chris Gregory, Alan Huffman, John M. Lannon, Jr., and Dorota Temple, "High Density Interconnect at 10 μm Pitch with Mechanically Keyed Cu/Sn-Cu and Cu-Cu Bonding for 3-D Integration", Proceedings of the 60<sup>th</sup> Electronic Components and Technology Conference, pp. 846-852, 2010.

- [6] Haruhiko Abe, Masahiro Yoneda, and Nobuo Fujiwara, "Developments of Plasma Etching Technology for Fabricating Semiconductor Devices", Japanese Journal of Applied Physics, Vol. 47, No. 3, pp. 1435–1455, 2008.

- [7] 谷田一真, 秋山雪治, 山地泰弘, 高橋浩之, 川上崇, 高橋健司, "20 µm ピッチ 微細 Au バンプ接合に関する基礎検討", エレクトロニクス実装学会誌, Vol. 10, No. 7, pp. 546-556, 2007.

- [8] B.K.Furman, and S.G.Mita, "Gold-Gold (Au-Au) Thermocompression (TC) Bonding of Very Large Arrays", Proceedings of the 42<sup>nd</sup> Electronic Components and Technology Conference, pp. 883-889, 1992.

- [9] James L. jellison, "Effect of Surface Contamination on the Thermocompression Bondability of Gold", IEEE transaction on Parts, Hybrids, and Packaging, Vol. 11, Issue. 3, pp. 206-202, 1975.

- [10] L. Condra, J. Svitak, and A. Pense, "The High Temperature Deformation Properties of Gold and Thermocompression Bonding", IEEE transaction on Parts, Hybrids, and Packaging, Vol. 11, Issue. 4, pp. 290-296, 1975.

- [11] J. E. Burke and D. Turnbull, "Recrystallization and Grain Growth", Progress in Metal Physics, Vol. 3, pp. 220, 1952.

# 第3章 Planar 構造を用いたハイブリッド接合

#### 3.1 緒言

本章では、CMP(Chemical mechanical polishing)で樹脂を平坦化して得られる Planar 構造を用いたハイブリッド接合技術を提案する[1, 2]。 Planar 構造はチップと基板に樹脂をスピンコートした後に、CMPで樹脂を研磨すること[3-6]で作製される。この作製方法は工程数が少なく、汎用性の高い CMP 技術を応用できるため量産化に向いている。 Planar 構造は Au バンプの塑性変形と未硬化樹脂の可塑性を利用して Au バンプと樹脂の表面段差を吸収する点において、第2章で論じた Lock and key 構造と類似するが、接合部が平坦な Planar 構造である点が大きく異なり、ファインピッチのバンプの接合構造にも対応できる特徴を有する。

本章の研究を通して達成すべき課題は次の通りである。第 1 に、樹脂の充填不足なくハイブリッド接合可能な Planar 構造の開発とその試作評価である。第 2 に、樹脂の硬化条件と CMP による樹脂の研磨速度の最適化である。

まず、未硬化樹脂の研磨速度は Au のそれよりも早いため Au バンプと樹脂表面の段差は増大すると考えられる。仮に、チップと基板の双方に未硬化樹脂を用いたとすると、接合時に樹脂の充填不良を生じる可能性がある。そこで、チップには未硬化樹脂を用い、他方の基板には未硬化樹脂よりも研磨速度が遅い硬化樹脂を用いることで Au バンプと硬化樹脂の段差の減少を試みた。次に、硬化樹脂を CMP で研磨するために樹脂の硬化条件と研磨速度の関係を評価する。最後に、CMP で作製した Planar 構造によるハイブリッド接合の有効性を検証する。

# 3.2 実験内容

#### 3.2.1 Planar 構造の試作評価に用いたチップと基板

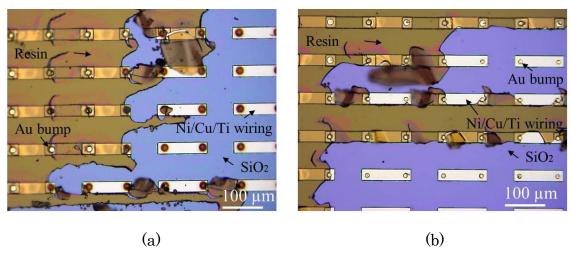

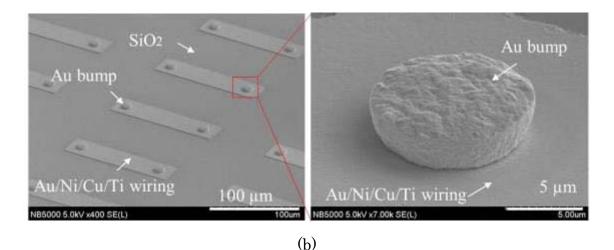

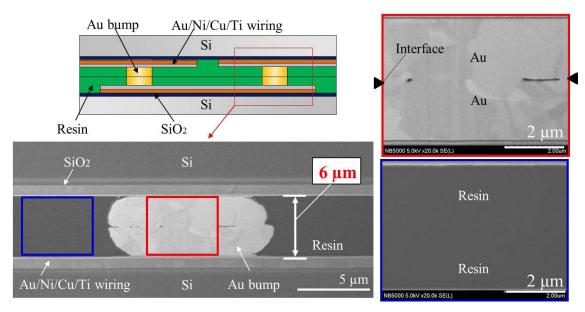

Planar 構造の試作評価用に作製したチップと基板の設計図、光学顕微鏡画像、 SEM 画像、及び Au バンプ表面の AFM 画像を図 3.1 に示す。チップと基板に は、 $SiO_2$  膜付きの Si 基板を用いた。Si 基板と  $SiO_2$  膜の厚さは  $525~\mu m$ 、500~n m である。チップと基板のサイズは、 $6~m m \times 6~m m$ 、 $15~m m \times 15~m m$  である。チップと基板には、電子ビーム蒸着で形成した Au/Ni/Cu/Ti 配線の上に、電解 めっきで Au バンプを形成した。Au/Ni/Cu/Ti 配線の構成は、上から Au、Ni、Cu、Ti であり、それぞれの膜厚は 200~n m、200~n m、500~n m、30~n m である。Au/Ni/Cu/Ti 配線はチップと基板を接合した際にAu バンプの全てが連結される配置とした。また、基板の周囲には電気抵抗測定用の四端子プローブを接触させるパッドを配置した。Au バンプの直径、ピッチ、高さ、及び数は  $10~\mu m$  と  $100~\mu m$ 、 $3.5~\mu m$ 、900~u ピンである。

図 3.1. Planar 構造の試作評価に用いたチップと基板の(a)設計図と(b)SEM 画像

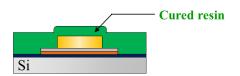

#### 3.2.2 チップと基板への Planar 構造の作製方法

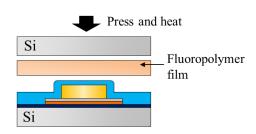

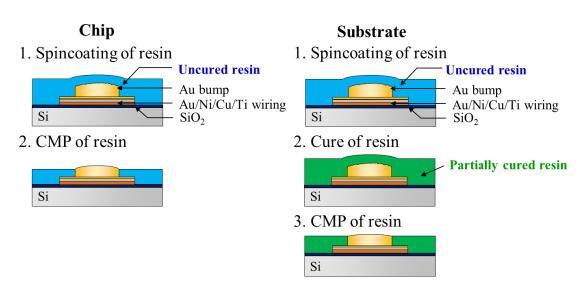

図 3.2 にチップと基板への Planar 構造の作製方法を示す。チップ全面に未硬化樹脂を、基板全面に半硬化樹脂をそれぞれ形成した。 Planar 構造の作製に使用した樹脂は第 2 章で述べた熱硬化性樹脂(NST1045、日産化学工業株式会社)と同一のものとした。

まず、溶剤に溶かした液体状の樹脂をチップと基板にスピンコートし、100 °C、2 分間の条件で樹脂をベークした後、さらに 150 °C、2 分間の条件で樹脂をベークして溶剤を蒸発させた。このベーク温度は樹脂の硬化開始温度の 180°C 以下であるため、樹脂は未硬化状態を維持する。基板に塗布した未硬化樹脂は、さらに 180 °C、1 時間の条件でベークして半硬化された。次に、樹脂用の CMP スラリー(株式会社 D-process)を使用して、チップと基板の双方の表面を研磨した。未硬化樹脂の CMP 時のヘッドとステージの回転数は 10 rpm と 10 rpm で研磨時間は 1 分 30 秒間とした。半硬化樹脂の CMP 時のヘッドとステージの回転数は 20 rpm と 60 rpm で研磨時間は 8 分間とした。この研磨条件により、チップ及び基板上の樹脂が薄化され、樹脂で覆われていた Au バンプの表面が露出されると同時に、Au バンプと樹脂を含めてチップ及び基板の全面が平坦化された。

図 3.2. チップと基板への Planar 構造の作製方法

#### 3.2.3 Planar 構造を用いたハイブリッド接合方法

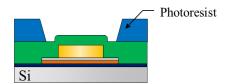

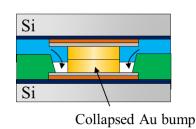

図 3.3 に Planar 構造によるハイブリッド接合方法を示す。第 2 章で述べたフリップチップボンダーと同一の装置を用いて、Planar 構造を作製したチップと基板を大気下で接合した。その際、接合前のチップと基板には表面処理を施さなかった。まず、カメラの画像処理で Planar 構造を作製したチップと基板の双方のアライメントマークを検出し、チップと基板の位置のアライメントを行った。次に、ヘッドとステージの双方の温度を 30 °C とし、100 N、5 秒間の条件でチップと基板の Au バンプを接触させた。次に、加圧を保持したままフリップチップボンダーのヘッドとステージの双方の温度を 150 °C に昇温し、300 秒間保持した。この過程でチップの未硬化樹脂は溶融して基板の半硬化樹脂と接着し、Au バンプと樹脂の表面段差を吸収した。最後に、ボンダーのヘッドとステージの双方の温度を 250 °C に昇温して、チップと基板の Au バンプの拡散接合 [7-11]と樹脂の硬化を行った。その後、接合された試料をホットプレート上で 250 °C、1 時間の条件でポストベークし、樹脂を完全に硬化させた。

接合した試料を以下の計測方法により評価した。樹脂中に発生するボイドと接合強度の評価のために、超音波顕微鏡観察とシェア強度測定を行った。シェア強度測定においてチップを側面から加圧するシェアツールの速度は 50 μm/secとした。シェアツール先端の基板表面からの高さは10 μm とした。また、Au バンプ、及び樹脂の接合界面を SEM で観察した。さらに、Au バンプの電気的な接続評価のために、Au バンプ及び Au バンプ間を連結する配線の電気抵抗を測定した。

# 1. Contact of Au bump 2. Resin bonding Uncured resin Si Si Si Partially cured resin Au bump 2. Resin bonding 3. Au-Au bonding and resin cure Si Collapsed Au bump

図 3.3. Planar 構造を用いたハイブリッド接合方法

#### 3.3 結果と考察

#### 3.3.1 チップと基板への Planar 構造の作製結果

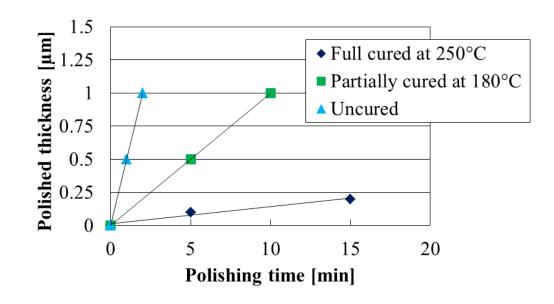

CMPによる樹脂の研磨時間と研磨量の関係を図 3.4 に示す。試料は、溶剤を蒸発したのみの未硬化樹脂、180°C、1時間の条件でベークした半硬化樹脂、及び250°C、1時間の条件でベークした完全硬化樹脂の3種類である。未硬化樹脂、半硬化樹脂、及び完全硬化樹脂のそれぞれの研磨レートは、約500 nm/min、約100 nm/min、約20 nm/minであった。この結果は、CMPによる完全硬化樹脂の研磨は困難であることを示している。これに対して半硬化樹脂の研磨レートは完全硬化樹脂のそれに比べて5倍に増加したため、基板に作製したPlanar構造には半硬化樹脂を採用した。

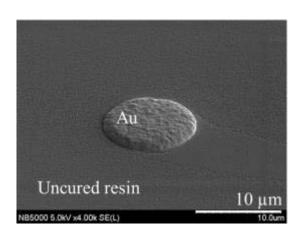

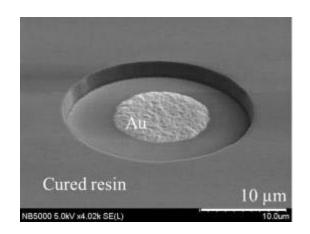

チップに作製した Planar 構造の Au バンプと未硬化樹脂の SEM 画像を図 3.5 に示す。Au バンプ上の未硬化樹脂を CMP で除去した結果、Au バンプと未硬化樹脂との表面段差は  $1~\mu m$  であった。一方、図 3.6 に示されるように、Au バンプと半硬化樹脂との表面段差は 150~nm とわずかであった。これは半硬化樹脂が Au の研磨速度と同程度であるがゆえ、Au バンプと半硬化樹脂が同じように研磨された結果である。

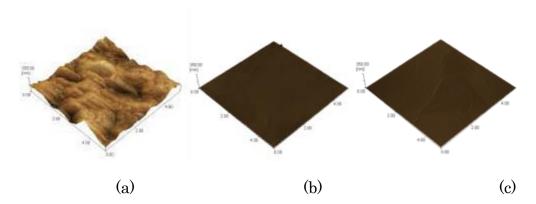

Planar 構造を作製したチップと基板のそれぞれの Au バンプの表面粗さを AFM で測定し、CMP 後の Au バンプ表面の平坦性を評価した。図 3.7 に CMP 前の Au バンプ表面、CMP 後のチップ側の Au バンプ表面、及び CMP 後の基板側の Au バンプ表面の AFM 画像を示す。なお、表面粗さの測定範囲を  $5~\mu m \times 5~\mu m$  とした。CMP 前の Au バンプ、CMP 後のチップの Au バンプ、及び CMP 後の基板の Au バンプの Rms は、それぞれ 49.75~n m、2.23~n m、2.29~n m であった。この結果は、CMP により Au バンプの表面が平坦化されたことを示している。加えて、Au バンプの表面粗さの低下は、接合時に発生する Au バンプ接合界面のボイドの低減[11]に寄与すると考えられる。

図 3.4. 樹脂の各硬化状態をパラメータとした CMP の研磨量と時間の関係

図 3.5. チップへの Planar 構造の作製工程における CMP 後の未硬化樹脂と Au バンプの SEM 画像

図 3.6. 基板への Planar 構造の作製工程における CMP 後の半硬化樹脂と Au バンプの SEM 画像

図 3.7. (a)CMP 前の Au バンプ表面、(b)CMP 後のチップ側の Au バンプ表面、及び(c)CMP 後の基板側の Au バンプ表面の AFM 画像

#### 3.3.2 Planar 構造を用いたハイブリッド接合結果

Planar 構造が作製されたチップと基板を接合した試料における樹脂のボイド発生と接合強度の評価結果について述べる。図 3.9 に接合試料の樹脂接合層を超音波顕微鏡で撮影した C-SAM 画像を示す。300 MHz の超音波プローブを用いてチップ側から樹脂接合層を撮影した結果、未硬化樹脂と半硬化樹脂の接合部にボイドの発生は確認されなかった。また、接合試料のシェア強度は 13 MPa以上であった。図 3.10 に示すように接合試料の Si 基板はシェア強度測定中にバルク破壊され、このことは未硬化樹脂と半硬化樹脂の接合が強固であることを示している。

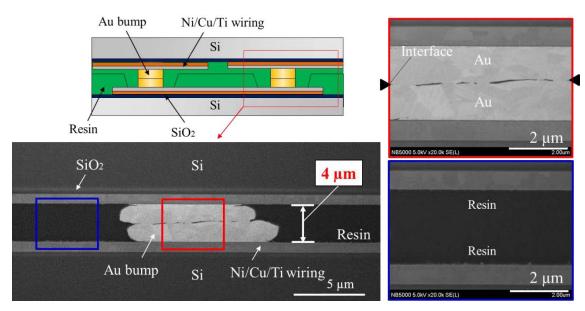

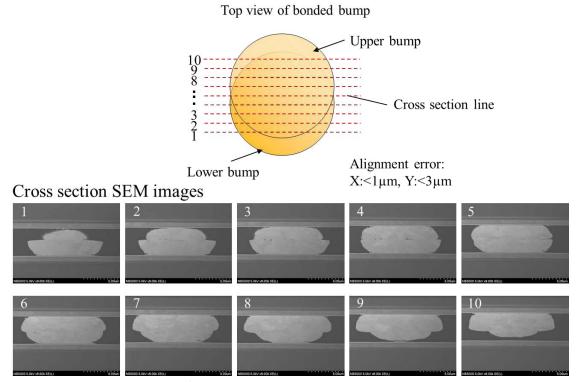

図 3.11 に接合試料の断面 SEM 画像を示す。Au バンプの接合界面では Au 原子の拡散が進行し、Au バンプ間で再結晶化[7,12]していた。また、未硬化樹脂と半硬化樹脂の間に接合界面は観察されず、このことは界面で架橋反応が生じ一体化したことを示している。図 3.12 に Au バンプの接合界面の観察結果を示す。FIB(Focused ion beam) (NB5000,株式会社日立ハイテクノロジーズ)によって Au バンプの接合部の断面を端から 1  $\mu$ m 間隔で露出させ、その断面を SEM で観察した。この結果から、Au バンプの接合界面のボイドの大きさと発生量は、第 2 章で述べた Lock and key 構造で接合した試料のそれより減少していたことが分かる。このことは、CMP による Au バンプ表面の平坦化が Au バンプの接合界面でのボイドの発生を低減したことを示している。

Planar 構造を作製したチップと基板を接合した試料において、Au バンプ間の電気的な接続を評価するために、Au バンプ及び Au バンプ間を連結する配線の電気抵抗を四端子プローブで測定した結果を図 3.8 に示す。縦軸の抵抗値はAu バンプと Au/Ni/Cu/Ti 配線の抵抗を全て含む。この結果からチップと基板に形成した 900 ピンの Au バンプ全てが電気的に接続されていることが分かる。

図3.8. Planar 構造を作製したチップと基板を接合した試料の電気抵抗測定結果

図 3.9. Planar 構造を作製したチップと基板を接合した試料の C-SAM 画像

図 3.10. シェア強度測定で破壊されたチップと基板の画像

図 3.11. Planar 構造を作製したチップと基板を接合した試料の断面 SEM 画像

図 3.12. Planar 構造を作製したチップと基板を接合した試料の Au バンプ接合界面の SEM 観察結果

## 3.4 結言

本章では、CMP で樹脂を平坦化して得られる Planar 構造を用いたハイブリッド接合技術を述べた。

まず、第 1 の課題である樹脂の充填不足なしにハイブリッド接合を可能にする Planar 構造の設計と試作評価の結果について述べた。未硬化樹脂の研磨速度は Au のそれよりも早いため Au バンプと樹脂表面の段差は増大すると考えられた。仮にチップと基板の双方に未硬化樹脂を用いたとすると、接合時に樹脂の充填不良を生じる可能性があった。そこで、チップには未硬化樹脂を用い、他方の基板には未硬化樹脂よりも研磨速度が遅い硬化樹脂を用いることを提案した。

次に、第2の課題である樹脂の硬化条件とCMPによる樹脂の研磨速度の最適化について述べた。基板へのPlanar構造の作製に用いた硬化樹脂をCMPで研磨するために、180°Cでベークした半硬化樹脂と250°Cでベークした完全硬化樹脂の研磨レートを比較した。その結果、CMPによる完全硬化樹脂の研磨は困

難であったが、半硬化樹脂の研磨レートは完全硬化樹脂のそれに比べて 5 倍に増加することを見出した。すなわち、半硬化樹脂を採用すれば CMP による研磨が可能であることを確認した。この結果に基づいて、基板に作製した Planar 構造には半硬化樹脂を採用した。

チップに作製した Planar 構造の Au バンプと未硬化樹脂との表面段差は 1 μm であった。一方、基板に作製した Planar 構造の Au バンプと半硬化樹脂との表面段差は 150 nm であった。すなわち、半硬化樹脂を用いることによって、Planar 構造の Au バンプと樹脂の表面段差を低減可能であることを明らかにした。

接合試料の断面 SEM 観察結果から、Au バンプの接合界面で Au 原子の拡散が進行し、Au バンプ間で再結晶化したことが分かった。そして、未硬化樹脂と半硬化樹脂の接合界面は観察されず、それらの界面で架橋反応が生じ一体化したことと、ボイドのないことが確認できた。また、CMP による Au バンプ表面の平坦化が Au バンプの接合界面でのボイド低減に効果的であることも示した。さらに、チップと基板に形成した 900 ピンの Au バンプ全てが電気的に接続が可能であることを確認した。

以上の結果によって、CMP で樹脂を平坦化して得られる Planar 構造がハイブリッド接合に有効であることを示した。CMP 技術を用いた作製方法は工程数が少なく、加えてバンプの表面粗さを低減でき、それらの高さを揃えることができる点において汎用性が高いため量産化に適している。

# 3.5 参考文献

- [1] Masatsugu Nimura, Jun Mizuno, Shuichi Shoji, Katsuyuki Sakuma, Hiroshi Ogino, Tomoyuki Enomoto, and Akitsu Shigetou, "Hybrid Au-Adhesive Bonding Technology Using Planar Adhesive Structure for 3D LSI", IEEE transaction on Components, Packaging and Manufacturing Technology, Vol. 4, Issue. 5, pp. 762-768, 2014.

- [2] Masatsugu Nimura, Jun Mizuno, Akitsu Shigetou, Katsuyuki Sakuma, and Shuichi Shoji, "Hybrid Au-Au Bonding using Planar Adhesive Structure for 3D Integration", Proceedings of the 63<sup>rd</sup> Electronic Components and Technology Conference, pp. 1153-1157, 2013.

- [3] Z.W. Zhong, Z.F. Wang, Zirajutheen B.M.P., Y.S. Tan, and Y.H. Tan, "CMP of PC, PMMA and SU-8 Polymers", Proceedings of the 5th International Conference on Polymers and Adhesives in Microelectronics

- and Photonics, pp. 58-62, 2005.

- [4] N. Motohashi, Y. Kurita, K. Soejima, Y. Tsuchiya, and M. Kawano, "SMAFTI Package with Planarized Multilayer Interconnects", Proceedings of the 59<sup>th</sup> Electronic Components and Technology Conference, pp. 599-606, 2009.

- [5] 重藤暁津, 伊藤寿浩, 須賀唯知, "Cu 超微細電極の常温直接接合を用いたバンプレスインタコネクト", 電子情報通信学会論文誌C, Vol. J88 C, No. 11, pp. 889-896, 2005.

- [6] Mayu Aoki, Kazuyuki Hozawa, and kenichi Takeda, "Wafer-Level Hybrid Bonding Technology with Copper/Polymer Co-planarization", 3D System Integration Conference, 2012.

- [7] 谷田一真, 秋山雪治, 山地泰弘, 高橋浩之, 川上崇, 高橋健司, "20 µm ピッチ 微細 Au バンプ接合に関する基礎検討", エレクトロニクス実装学会誌, Vol. 10, No. 7, pp. 546-556, 2007.

- [8] B.K.Furman, and S.G.Mita, "Gold-Gold (Au-Au) Thermocompression (TC) Bonding of Very Large Arrays", Proceedings of the 42<sup>nd</sup> Electronic Components and Technology Conference, pp. 883-889, 1992.

- [9] James L. jellison, "Effect of Surface Contamination on the Thermocompression Bondability of Gold", IEEE transaction on Parts, Hybrids, and Packaging, Vol. 11, Issue. 3, pp. 206-202, 1975.

- [10] L. Condra, J. Svitak, and A. Pense, "The High Temperature Deformation Properties of Gold and Thermocompression Bonding", IEEE transaction on Parts, Hybrids, and Packaging, Vol. 11, Issue. 4, pp. 290-296, 1975.

- [11] Taiji Sakai, et al., "A New Flip Chip Bonding Method Using Ultra-Precision Cutting of Metal/Adhesive Layers", Proceedings of International Conference on Electronics Packaging, pp. 99-104, 2007.

- [12] J. E. Burke and D. Turnbull, "Recrystallization and Grain Growth", Progress in Metal Physics, Vol. 3, pp. 220, 1952.

# 第4章

# シングルミクロンピッチのバンプと樹脂で構成 される Planar 構造を用いたハイブリッド接合

#### 4.1 緒言

本章では、シングルミクロンピッチのバンプと樹脂で構成される Planar 構造を用いたハイブリッド接合技術を提案する[1-3]。

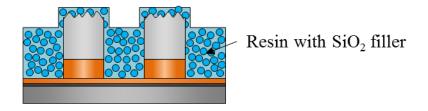

第2章と第3章で確立した接合構造とその作製方法を要素技術として本章の研究に応用し、さらに接合構造を構成する材料の視点も取り入れて、これらを一体で設計、試作評価する。まず、接合構造は8μm ピッチのバンプを有するため Planar 構造を採用することにした。8μm ピッチのバンプと樹脂で構成される Planar 構造の作製には、樹脂の CMP とプラズマエッチングを組み合わせた工法を検討する。CMP で樹脂を平坦化すると同時にバンプの表面粗さが低減され、バンプの高さも揃えられる。次に、プラズマ照射で樹脂をエッチバックしてバンプと樹脂の表面に段差を設けることによって、接合時に未硬化樹脂がバンプの接合界面へ流入することを防止できる。本章の研究で使用する樹脂には、バンプの接合部に生じる応力の緩和のために低熱膨張係数の SiO<sub>2</sub>フィラー含有樹脂[4,5][4]を用いる。

本章の研究を通して達成すべき課題は次の通りである。第1に、超高密度(8  $\mu$ m ピッチ)バンプの接合荷重を低減可能なバンプ材料の検討である。第2に、8  $\mu$ m ピッチのバンプ間に充填可能な  $SiO_2$  フィラー含有樹脂の検討である。第3に、8  $\mu$ m ピッチのバンプと  $SiO_2$  フィラー含有樹脂で構成される Planar 構造の作製方法の構築である。第4に、バンプと  $SiO_2$  フィラー含有樹脂の表面段差構造の設計と試作評価である。第5に、接合基材に最適なプラズマ表面処理の検討である。

超高密度(8 μm ピッチ)バンプの接合荷重を低減可能なバンプ材料には、低圧力で塑性変形する Sn を先端に用いる Sn/Cu バンプを検討する。

8  $\mu$ m ピッチの Sn/Cu バンプ間に充填可能な  $SiO_2$  フィラー含有樹脂には、 Sn/Cu バンプ間の  $4 \mu$ m の隙間に樹脂を充填するために直径 80 nm の  $SiO_2$  フィ

ラーを含有した樹脂を検討する。

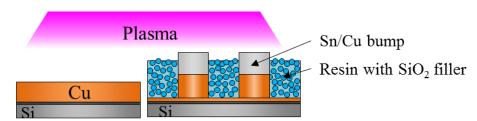

8  $\mu$ m ピッチの Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂から成る Planar 構造 の作製方法には、樹脂の CMP と  $O_2/CHF_3$  プラズマエッチングを組み合わせた 工法について検討する。 $SiO_2$  フィラー含有樹脂の CMP では、スループットを 上げるために、Sn/Cu バンプの高さ、樹脂の粘度、及びスピンコート条件を最 適化して、CMP の前に予め Sn/Cu バンプの先端部が樹脂から突出している構造を試作評価することとした。プラズマエッチングには、第 1 章でその効果が 実証され、 $SiO_2$  フィラーと樹脂の両方を同時にエッチング可能な  $O_2$  と  $CHF_3$  の混合プラズマ[6,7]を用いることとした。

Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂の表面段差構造の設計と試作評価では、Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂の表面段差値と、Sn/Cu バンプと Cu 膜の接合界面への樹脂噛み込みの発生の関係を定量評価する。Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂の表面段差値は  $O_2/CHF_3$  プラズマ照射の時間で制御する。接合基材に最適なプラズマ表面処理の検討では、未処理、Ar ガス及び  $Ar/H_2(H_2$  濃度 4 %) フォーミングガスのプラズマ処理[8-10] をしたチップと基板を接合した試料の接合強度を比較することとした。加えて、それぞれの試料において  $SiO_2$  フィラー含有樹脂と Cu 膜の接合部状態、及び Sn/Cu バンプと Cu 膜の接合状態を断面観察で比較評価する。

# 4.2 実験内容

## 4.2.1 Planar 構造の試作評価に用いたシングルミクロンピッチの バンプを有するチップ

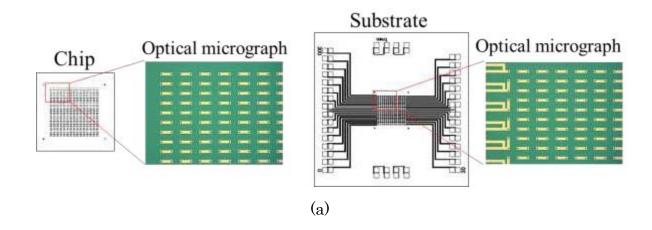

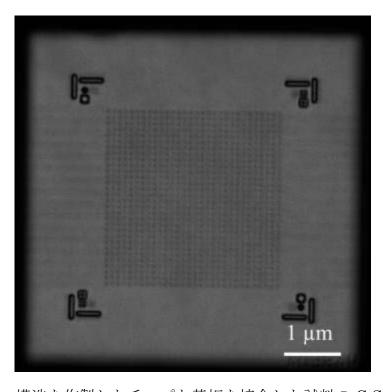

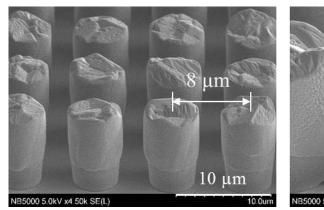

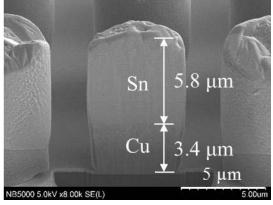

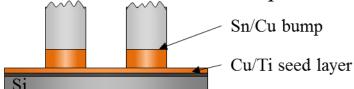

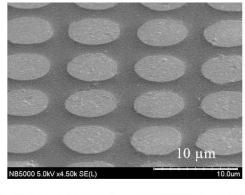

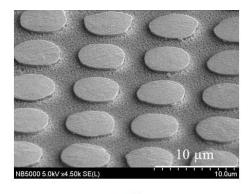

シングルミクロンピッチのバンプと樹脂から成る Planar 構造の試作評価用に、Sn/Cu バンプ[6]を電解めっきで形成したチップを作製した。また、チップを接合する基板には Cu/Ti 膜を電解めっきで形成した。チップと基板には、厚さが $525~\mu m$  である Si 基板を用いた。チップと基板のサイズは、 $6~mm \times 6~mm$ 、 $3~mm \times 3~mm$  である。チップに形成した Su/Cu バンプの直径、ピッチ、及び数は、 $4~\mu m$ 、 $8~\mu m$ 、 $140625~ ピン(3mm \times 3mm$  の範囲)とし、Sn/Cu バンプは $8~\mu m$  ピッチでチップ全面に形成した。Sn/Cu バンプの下には電解めっきのためのシード層として Cu/Ti 膜が存在し、その構成は上から Cu と Ti であり、それぞれの膜厚は 100~nm と 30~nm である。Sn/Cu バンプの Sn と Cu の厚さの設

計値は  $6 \, \mu m$  と  $3 \, \mu m$  とし、Sn/Cu バンプの高さばらつきと CMP の研磨量を考慮して Sn の厚さは Cu の 2 倍とした。チップに作製した Sn/Cu バンプの SEM 画像を図 4.1 に示す。SEM による測長の結果、Sn と Cu の膜厚の実測値は 5.8  $\mu m$  と 3.4  $\mu m$  であった。一方、基板に形成した Cu/Ti 膜の構成は上から Cu と Ti であり、それぞれの膜厚は  $3 \, \mu m$  と  $30 \, nm$  とした。

図 4.1. 8 μm ピッチの Sn/Cu バンプの SEM 画像

# 4.2.2 シングルミクロンピッチのバンプを有するチップへの Planar 構造の作製方法

樹脂にはナノサイズの  $SiO_2$  フィラーを含有した熱硬化性樹脂(NST1147、日産化学工業株式会社)を使用した。バンプの接合部に生じる応力を緩和するために低熱膨張係数の  $SiO_2$  フィラー含有樹脂を使用した。この樹脂の  $SiO_2$  フィラーの充填率は製品仕様より 50 wt%である。この樹脂は常温で固体であり、加熱すると粘度が低下して可塑性を示す。図 4.2 に樹脂の粘度と温度の関係のグラフを示す。この図に示されるように、常温から温度上昇につれて粘度が低下し、約 140 °C で最低粘度となる。そして、約 140 °C から樹脂の硬化が始まり粘度が上昇し、約 200 °C で樹脂の硬化反応が進み粘度変化が減少する。

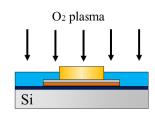

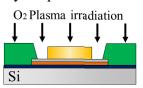

図 4.3 にシングルミクロンピッチの Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂で構成される Planar 構造の作製方法を示す。まず、溶剤に溶かされた液体状の  $SiO_2$  フィラー含有樹脂を Sn/Cu バンプを形成したチップにスピンコートし、 100 °C、5 分間の条件でそれをベークした後、さらに 130 °C、5 分間の条件で それをベークして溶剤を蒸発させた。 $SiO_2$  フィラー含有樹脂の硬化開始温度は 約 140 °C であるため、このベーク後の樹脂は未硬化状態を維持する。次に、こ

の樹脂用の CMP スラリー(株式会社 D-process)を使用して Sn/Cu バンプの Sn と SiO<sub>2</sub> フィラー含有樹脂を研磨した。CMP 時のヘッドとステージの回転数は 40 rpm と 80 rpm とし、研磨時間を 8 分間とした。最後に、CCP による O<sub>2</sub>/CHF<sub>3</sub> プラズマで SiO<sub>2</sub> フィラー含有樹脂をエッチバックし、Sn/Cu バンプと SiO<sub>2</sub> フィラー含有樹脂の表面間に段差を作製した。 $O_2$ /CHF<sub>3</sub> プラズマ照射時の真空度を 20 Pa、出力を 100 W、 $O_2$  と CHF<sub>3</sub> のガス流量を各々 10 sccm とした。

図 4.2. SiO<sub>2</sub>フィラー含有樹脂の粘度と温度の関係[2]

第4章

# 1. Formation of Sn/Cu microbumps

# 2. Spincoating of resin

# 3. Planarization by CMP

# 4. Etch back by O<sub>2</sub>/CHF<sub>3</sub> plasma

図 4.3. Sn/Cu バンプと SiO2 フィラー含有樹脂で構成される Planar 構造の作製 方法

# 4.2.3 シングルミクロンピッチのバンプと樹脂で構成される Planar 構造を用いたハイブリッド接合方法とその評価内容

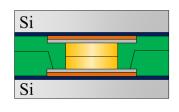

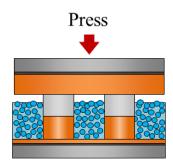

図 4.4 に Sn/Cu バンプと SiO<sub>2</sub> フィラー含有樹脂で構成される Planar 構造を 作製したチップと Cu 膜を形成した基板のハイブリッド接合方法を示す。まず、 プラズマ表面処理装置(PL8、SUSS MicroTEC KK)で、Planar 構造を作製した チップの Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂表面、及び基板の Cu 膜表面に プラズマ照射した。プラズマ表面処理のガスには、Ar ガス、及び  $Ar/H_2$ のフォ ーミングガスを用いた。 $Ar/H_2$ のフォーミングガスの  $H_2$ 濃度は安全性の観点か ら爆発限界以下である 4%とした。プラズマ表面処理時の真空度を 50 Pa、出力 を  $100~\mathrm{W}$ 、 $\mathrm{Ar}$  ガス及び  $\mathrm{Ar}/\mathrm{H}_2$ のフォーミングガスの流量を  $35~\mathrm{secm}$ 、照射時間 を 3 分間とした。Ar ガスを用いたプラズマを Ar プラズマ、 $Ar/H_2$ フォーミン グガスを用いたプラズマを Ar/H2 プラズマと以下表記する。次に、チャンバー 付きフリップチップボンダーを用いて、Planar 構造を作製したチップと Cu 膜 を形成した基板を大気圧 N<sub>2</sub>下で接合した。フリップチップボンダーのヘッドと ステージの双方にはセラミックヒーターが付属している。接合前に予めチップ と基板の接合面をアライメントした状態でステージに設置した。接合時にはへ ッドに重りを載せてチップと基板を加圧した。チャンバー内の雰囲気は Sn/Cu バンプと Cu 膜の接合界面の酸化を防止するために大気を  $N_2$  で置換し、チャン バー内の O2 濃度を 100 ppm 以下にした。次に、ヘッドとステージの双方の温 度を 30 °C、荷重を 100 N、加圧時間を 5 秒間とした条件でチップの Sn/Cu バ ンプのSn と基板のCu 膜を接触させた。加圧を保持したままフリップチップボ ンダーのヘッドとステージの双方の温度を 260  $^{\circ}$ C に昇温し、1 秒間保持した後 に常温まで冷却した。昇温時にチップの未硬化状態の SiO<sub>2</sub> フィラー含有樹脂が 溶融して基板の Cu 膜と接着するため、Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂 の表面段差が吸収される。また、 $260\,^{\circ}$ C へ昇温することで、Sn と Cu 間の拡散 が促進され[11-17]、 $SiO_2$ フィラー含有樹脂が硬化する。

次に、Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂で構成される Planar 構造を作製したチップと Cu 膜を形成した基板のハイブリッド接合を行うために、接合構造と接合前のプラズマ表面処理の 2 つの視点から接合を評価した内容を以下に示す。接合構造に関しては、Planar 構造を作製したチップにおける Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂の表面段差値と、Sn/Cu バンプと Cu 膜の接合界面への  $SiO_2$  フィラー含有樹脂の噛み込み発生の関係を定量評価した。接合前のプラズマ表面処理に関しては、未処理、Ar 及び  $Ar/H_2$ プラズマ表面処理をしたチ

ップと基板を接合した試料の接合強度を比較した。加えて、それぞれの試料において $SiO_2$ フィラー含有樹脂とCu膜の接合部状態、及びSn/CuバンプとCu膜の接合状態を断面観察で比較評価した。

#### 1. Surface treatment

# 2. Contact of bump

# 3. Resin bonding

# 4. Solder bonding and resin cure

図 4.4. Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂で構成される Planar 構造を作製したチップと Cu 膜を形成した基板のハイブリッド接合方法

#### 4.3 結果と考察

## 4.3.1 シングルミクロンピッチのバンプを有するチップへの Planar 構造の作製結果

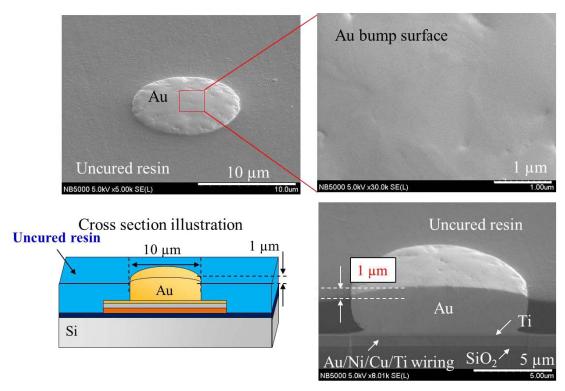

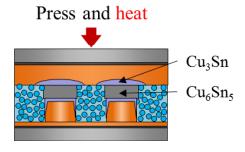

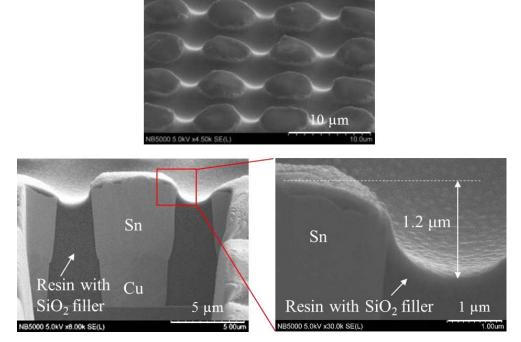

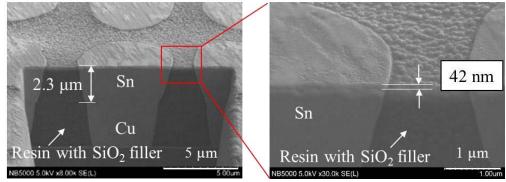

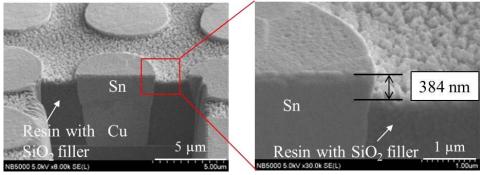

$SiO_2$ フィラー含有樹脂をスピンコートしたチップの Sn/Cu バンプと  $SiO_2$ フィラー含有樹脂の SEM 画像を図 4.5 に示す。この SEM 画像から、Sn/Cu バンプ間の 4  $\mu m$  の隙間に  $SiO_2$ フィラー含有樹脂が充填されたことが確認できる。 Sn/Cu バンプ上に残る  $SiO_2$ フィラー含有樹脂の膜厚は 100 nm 以下で、Sn/Cu バンプの表面は  $SiO_2$ フィラー含有樹脂のそれよりも 1.2  $\mu m$  高い構造であった。  $SiO_2$  フィラー含有樹脂をスピンコートしたチップを CMP で研磨した後の Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂の SEM 画像を図 4.6 に示す。Sn/Cu バンプ上の  $SiO_2$  フィラー含有樹脂は除去され、Sn/Cu バンプの Sn 表面も  $SiO_2$  フィラー含有樹脂の研磨と同時に平坦化されたことが分かる。CMP 後の Sn/Cu バンプの Sn の厚さは 2.3  $\mu m$  であった。Sn/Cu バンプと  $SiO_2$ フィラー含有樹脂の表面段差は 42 nm であり、Sn/Cu バンプと  $SiO_2$ フィラー含有樹脂の研磨 速度が同程度であったことが分かった。

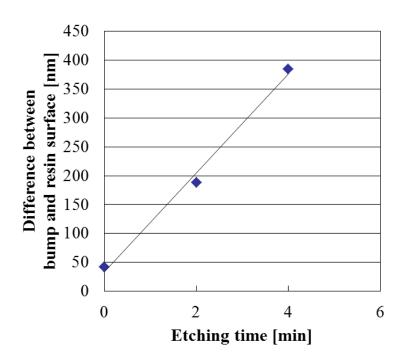

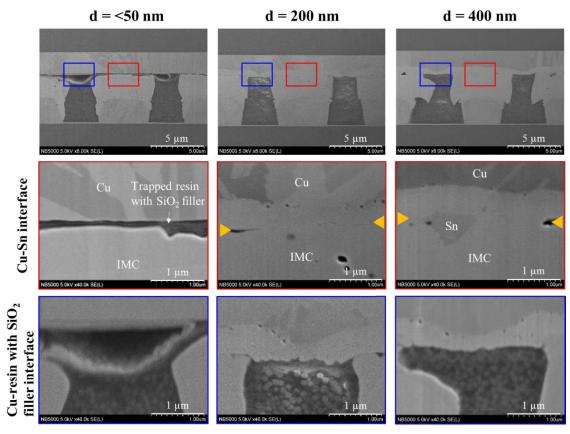

次に、 $O_2/CHF_3$ プラズマ照射時の  $O_2$ と  $CHF_3$ のガス流量と  $SiO_2$ フィラー含有樹脂のエッチングの関係を評価した。樹脂と  $SiO_2$  はそれぞれ  $O_2$ と  $CHF_3$ によってエッチングされる。その反応式は次式の通りである。

$$C_x H_y O_z + O_2 \rightarrow CO_x + H_2 O \tag{4.1}$$

$$SiO_2 + CHF_3 \rightarrow SiF_x + CO_x + HF$$

(4.2)

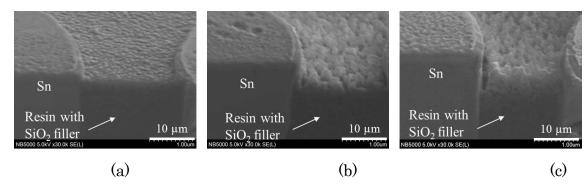

図 4.7 に CMP 後に  $O_2$ /CHF $_3$ プラズマ照射をしたチップの  $S_1$ /Cu バンプと  $S_1O_2$  フィラー含有樹脂の SEM 画像を示す。また、そのチップにおける  $S_1$ /Cu バンプと  $S_1O_2$  フィラー含有樹脂の表面段差値を図 4.8 に示す。 $O_2$ /CHF $_3$ プラズマ照射時の  $O_2$  と CHF $_3$ のガス流量は 5 sccm と 20 sccm、10 sccm と 10 sccm、及び 20 sccm と 5 sccm とした。 $O_2$  と CHF $_3$ のガス流量が 5 sccm と 20 sccm の場合では、20 sccm と 20 sccm の場合では、20 sccm と 20 sccm の場合では、20 sccm の場合では、付脂と20 sccm の場合では、20 sccm の場合では、付脂と20 sccm の場合では、付脂と20 sccm の場合では、付脂と20 sccm の場合では、20 sccm のるのでは、20 sccm のるのでは、20

樹脂と  $SiO_2$  のエッチングレートの差により、樹脂よりもレートが低い  $SiO_2$  が 残存したと考えられる。 $O_2$  と  $CHF_3$  のガス流量が 20 sccm と 5 sccm の場合では、他の条件よりエッチング量が増加した。しかし、 $O_2$  と  $CHF_3$  のガス流量が 10 sccm と 10 sccm である場合に比べて、樹脂のエッチングレートが増加し、 $SiO_2$  のエッチングレートが低下した結果、 $SiO_2$  フィラー含有樹脂の表面における  $SiO_2$  フィラーのみの層の厚さが増加した。そのため、 $SiO_2$  フィラー含有樹脂の接合部の接着不良の可能性が認められた。以上の結果から、 $O_2$ / $CHF_3$  プラズマの  $O_2$  と  $CHF_3$  のガス流量条件は各々 10 sccm とした。

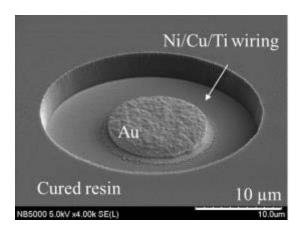

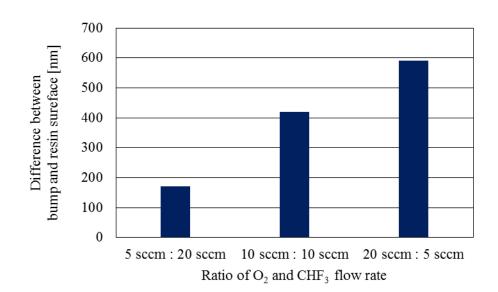

$O_2/CHF_3$ プラズマの照射時間に対する Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂の表面段差値 d の関係を図 4.9 に示す。 $O_2/CHF_3$ プラズマ照射前の初期の表面段差値  $d_0$  は 42 nm であり、照射時間を 2 分間と 4 分間とした場合の表面段差値 d は 188 nm、384 nm であった。この結果から、 $O_2/CHF_3$ プラズマの照射によって  $SiO_2$  フィラー含有樹脂のエッチングを時間で制御可能であることが分かる。図 4.10 に照射時間を 4 分間とした場合の  $O_2/CHF_3$ プラズマを照射したチップの Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂の SEM 画像を示す。チップ全面において  $SiO_2$  フィラー含有樹脂がエッチバックされ、Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂の表面間に段差が形成されたことが分かる。

図 4.5.  $SiO_2$  フィラー含有樹脂をスピンコートしたチップの Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂の SEM 画像

図 4.6.  $SiO_2$ フィラー含有樹脂をスピンコートしたチップを CMP で研磨した後の Sn/Cu バンプと  $SiO_2$ フィラー含有樹脂の SEM 画像

図 4.7. CMP で研磨した後に  $O_2/CHF_3$ プラズマを照射したチップの Sn/Cu バンプと  $SiO_2$ フィラー含有樹脂の SEM 画像  $(O_2/CHF_3$ プラズマ照射時の  $O_2$ と  $CHF_3$ のガス流量は (a)5 sccm と 20 sccm、(b)10 sccm と 10 sccm、及び (c)20 sccm と 5 sccm)

図 4.8. CMP で研磨した後に  $O_2/CHF_3$ プラズマを照射したチップの Sn/Cu バンプと  $SiO_2$ フィラー含有樹脂の表面段差値の関係 $(O_2/CHF_3$ プラズマ照射時の  $O_2$ と  $CHF_3$ のガス流量は 5 sccm と 20 sccm、10 sccm と 10 sccm、及び 20 sccm と 5 sccm)

図 4.9.  $O_2/CHF_3$ プラズマの照射時間に対する Sn/Cu バンプと  $SiO_2$ フィラー含有樹脂の表面段差値の関係 $(O_2/CHF_3$ プラズマ照射時の  $O_2$ と  $CHF_3$ のガス流量は 10 sccm と 10 sccm)

図 4.10.  $O_2$ /CHF $_3$ プラズマを照射した後の  $S_n$ /Cu バンプと  $SiO_2$ フィラー含有樹脂の SEM 画像

#### 4.3.2 バンプと樹脂の表面段差構造のハイブリッド接合への影響

Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂の表面段差値と、Sn/Cu バンプと Cu 膜の接合界面への  $SiO_2$  フィラー含有樹脂の噛み込みの発生の関係を定量評価した結果について述べる。

Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂の表面段差値 d が 50 nm 以下、200 nm、及び 400 nm である 3 種類のチップと Cu 膜を形成した基板を接合した。なお、表面段差値 d が 50 nm 以下のチップは  $O_2/CHF_3$ プラズマによる  $SiO_2$  フィラー含有樹脂のエッチバックを施していないものである。接合前のチップと基板のプラズマ表面処理には、 $Ar/H_2$ プラズマを用いた。図 4.11 にそれらの接合試料の断面 SEM 画像を示す。表面段差値 d が 50 nm 以下の場合では、Sn/Cu バンプと Cu 膜の接合界面に  $SiO_2$  フィラー含有樹脂の噛み込みが確認された。フリップチップボンダーのヘッドとステージの平行不良やチップと基板表面の歪みの影響で、常温での加圧時に Sn/Cu バンプと Cu 膜が接触しなかったことが原

図  $4.11. \, \text{Sn/Cu}$  バンプと  $\text{SiO}_2$  フィラー含有樹脂の表面段差構造を作製したチップを基板へ接合した試料の断面 SEM 画像(接合したチップの表面段差値 d は 50 nm 以下、 $200 \, \text{nm}$ 、及び  $400 \, \text{nm}$ )

因として考えられる。一方、表面段差値 d が 200 nm と 400 nm の場合では、いずれも Sn/Cu バンプと Cu 膜の接合界面に  $SiO_2$  フィラー含有樹脂の噛み込みは発生しなかった。段差値 d を増加したことで常温での加圧時に Sn/Cu バンプと Cu 膜が接触し、それらの接合界面への  $SiO_2$  フィラー含有樹脂の流入が防止されたためと考えられる。また、 $SiO_2$  フィラー含有樹脂と Cu 膜の接合界面では、 $SiO_2$  フィラー含有樹脂はボイドなく充填され接合されている。

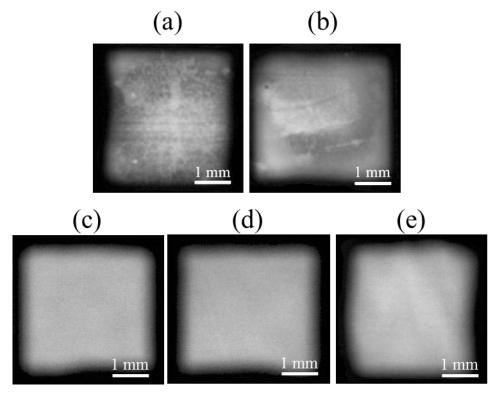

次に、Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂の表面段差の吸収過程の評価結果を示す。接合時のヘッドとステージの最終到達温度は 80 °C、100 °C、130 °C、200 °C、260 °C とした。各温度で接合した試料の  $SiO_2$  フィラー含有樹脂と  $SiO_2$  フィラー含有樹脂と  $SiO_2$  フィラー含有樹脂の表面段差値  $SiO_2$  フィラー含有樹脂の表面段差値  $SiO_2$  フィラー含有樹脂の表面段差値  $SiO_2$  である  $SiO_3$  アイラー含有樹脂の表面段差値  $SiO_4$  が  $SiO_4$  である  $SiO_4$  アイラーで表面のチップを用いた。また、接合前のチップと基板のプラズマ表面処理には、 $SiO_4$  アラズマを用いた。各温度条件で接合した試料の  $SiO_4$  でいた。 $SiO_4$  では、 $SiO_4$  では、 $SiO_4$  では、 $SiO_4$  である  $SiO_4$  では、 $SiO_4$

図 4.12. 接合時の最終到達温度を(a) 80 °C、(b) 100 °C、(c) 130 °C、(d) 200 °C、(e) 260 °C で接合した試料の C-SAM 画像

ジの接合時の温度が 130 °C のときに、 $SiO_2$ フィラー含有樹脂と Cu 膜の接合界面のボイドが消失したと分かる。すなわち、 $SiO_2$  フィラー含有樹脂の粘度が最も低くなった 130 °C の時点で Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂の表面段差が吸収されたことを示している。

#### 4.3.3 プラズマ表面処理の接合強度と接合界面への影響

Planar 構造を作製したチップと Cu 膜を形成した基板への接合前のプラズマ表面処理の効果を評価するために、接合試料の接合強度測定、 $SiO_2$  フィラー含有樹脂と Cu 膜の接合部、及び Sn/Cu バンプと Cu 膜の接合部を観察した結果について述べる。この評価に用いたチップの Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂の表面段差値 d は d00 nm とした。

まず、Ar プラズマ表面処理及び Ar/H2プラズマ表面処理をしたチップと基板 接合強度測定の結果を示す。接合強度評価にはチップと基板の接合部のシェア 強度を測定した。チップを側面から加圧するときのシェアツールの速度は 100 μm/sec とした。シェアツール先端の基板表面からの高さは 100 μm とした。図 4.13 に未処理、Ar プラズマ表面処理、及び  $Ar/H_2$  プラズマ表面処理をしたチッ プと基板を接合した試料のシェア強度の測定結果を示す。シェア強度は各表面 処理条件において2つの接合試料の平均値とした。まず、未処理の SiO2フィラ 一含有樹脂を形成したチップを基板に接合した試料の接合強度は、SiO<sub>2</sub>フィラ 一含有樹脂を形成しなかったチップを基板に接合した試料のそれに比べて 2.9 倍に増加した。これは、SiO2フィラー含有樹脂が Cu 膜と接合したことを示し ている。Ar プラズマ表面処理をしたチップと基板を接合した試料の接合強度は 未処理のそれに比べて 2.3 倍に増加した。 $Ar/H_2$ プラズマ表面処理したチップと 基板を接合した試料の接合強度は未処理のそれに比べて 1.6 倍に増加した。これ らの結果は、Ar プラズマ表面処理と Ar/H₂ プラズマ表面処理が Sn/Cu バンプと SiO<sub>2</sub>フィラー含有樹脂を形成したチップと Cu 膜を形成した基板の接合強度を 増加させるのにがあったことを示している。

次に、図 4.14 に未処理、Ar プラズマ表面処理、及び  $Ar/H_2$  プラズマ表面処理をしたチップと基板を接合した試料における  $SiO_2$  フィラー含有樹脂と Cu 膜の接合部の観察結果を示す。この接合部は超音波顕微鏡、及び接合強度試験後に光学顕微鏡で観察した。超音波顕微鏡観察では 210 MHz の超音波プローブを用いて基板側から  $SiO_2$  フィラー含有樹脂と Cu 膜の接合部を撮影した。未処理の

図 4.13. 未処理、Ar プラズマ表面処理、及び  $Ar/H_2$  プラズマ表面処理をしたチップと基板を接合した試料のシェア強度の測定結果

場合にはその接合部の樹脂内に縦横にボイドが発生したが、Ar プラズマ表面処理と  $Ar/H_2$  プラズマ表面処理の場合にはいずれもボイドは発生しなかった。このことは、Ar 及び  $Ar/H_2$  プラズマ表面処理により Cu 表面の有機膜と酸化膜が減少し、Cu 膜への  $SiO_2$  フィラー含有樹脂の濡れ性が向上したことを示している。

図 4.15 に未処理、Ar プラズマ表面処理、及び  $Ar/H_2$  プラズマ表面処理をしたチップと基板を接合した試料の断面 SEM 画像と断面 SIM 画像を示す。断面 SEM 画像から、未処理と Ar プラズマ表面処理の場合には、Sn/Cu バンプの Sn と Cu 膜の接合部に界面が存在していたことが分かる。Sn が Cu 膜へ拡散していたことから、この界面は樹脂ではなく、Sn/Cu バンプの Sn 表面と Cu 膜表面に存在した有機膜と酸化膜、または Sn/Cu バンプと Cu 膜の表面粗さに起因して発生した空隙である。Ar プラズマ表面処理の場合には、シェア強度が増加した結果から物理的なスパッタリング作用で有機膜と酸化膜は一定量除去されたが、Sn と Cu の接合においてはそれらの除去が不十分であったと考えられる。一方、 $Ar/H_2$  プラズマ表面処理の場合には、Sn/Cu バンプと Cu 膜の接合界面が消失した。これは、Cu のスパッタリング作用に Cu の還元作用が付加されたため、Cu が Cu 膜へ十分に拡散可能な程に有機膜と酸化膜が除去されたことを示

第4章

図 4.14. 未処理、Ar プラズマ表面処理、及び  $Ar/H_2$  プラズマ表面処理をしたチップと基板を接合した試料における  $SiO_2$  フィラー含有樹脂と Cu 膜の接合部の観察結果

している。また、図 4.16 に示す断面 SIM 画像から、Sn/Cu バンプの Sn と Cu 膜の界面には、 $Cu_3Sn$  と  $Cu_6Sn_5$  [18]が生成されたことが分かる。各接合試料の Sn/Cu バンプの Sn と Cu 膜の接合界面に生成された IMC(Intermetallic compound)の膜厚 X を測定し、Sn と Cu 間の拡散を定量評価した。その測定結果を図 4.15 に示す。 $Ar/H_2$ プラズマ表面処理の場合での IMC 膜厚は、未処理の それに比べて 1.9 倍に増加しており、Sn と Cu の間での原子拡散が促進された ことが分かる。これらの結果は、 $Ar/H_2$ プラズマ表面処理が接合前の表面処理に 有効であることを示している。

第4章

図 4.15. 未処理、Ar プラズマ表面処理、及び  $Ar/H_2$  プラズマ表面処理をしたチップと基板を接合した試料の断面 SEM 画像と断面 SIM 画像

図 4.16. 未処理、Ar プラズマ表面処理、及び  $Ar/H_2$  プラズマ表面処理をしたチップと基板を接合した試料の Sn/Cu バンプと Cu 膜の接合界面に生成した IMC 膜厚の測定結果

#### 4.4 結言

本章では、シングルミクロンピッチのバンプと樹脂で構成される Planar 構造を用いたハイブリッド接合技術について述べた。

まず、第1の課題である超高密度(8  $\mu$ m ピッチ)バンプの接合荷重を低減可能な材料の検討では、低圧力で塑性変形する Sn をバンプ先端の材料に採用し、Sn/Cu バンプを作製した。ハイブリッド接合の結果から、Sn を用いたことでSn/Cu バンプと  $SiO_2$  フィラー含有樹脂の表面段差の吸収に成功した。

第2の課題である  $8 \mu m$  ピッチの Sn/Cu バンプ間に充填可能な  $SiO_2$  フィラー含有樹脂の検討では、ナノサイズの  $SiO_2$  フィラーを含有した樹脂を採用して、Sn/Cu バンプ間の  $4 \mu m$  の隙間に  $SiO_2$  フィラー含有樹脂をボイドなく、フィラーも均一に充填することに成功した。

第3の課題である8  $\mu$ m ピッチの Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂から成る Planar 構造の作製方法の構築を目的として、 $SiO_2$  フィラー含有樹脂の CMP と  $O_2/CHF_3$  プラズマエッチングを組み合わせた工法を提案した。 $SiO_2$  フィラー含有樹脂の CMP のスループットを上げるために、Sn/Cu バンプの高さ、 $SiO_2$  フィラー含有樹脂の粘度、及びスピンコート条件を最適化して CMP の前に予め Sn/Cu バンプの先端部が  $SiO_2$  フィラー含有樹脂の研磨量を減少することができ、CMP 時間の短縮に成功した。また、CMP による研磨で  $SiO_2$  フィラー含有樹脂を平坦化すると同時に Sn/Cu バンプの Sn 表面も平坦化され、それらの高さを揃えることに成功した。Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂の表面段差を作製するための  $O_2/CHF_3$  プラズマ照射において、 $O_2$  と  $CHF_3$  のガス流量を最適化することで  $SiO_2$  フィラー含有樹脂を均一にエッチングすることが可能であることを実証した。

第4の課題であるハイブリッド接合可能なSn/Cuバンプと $SiO_2$ フィラー含有樹脂の表面段差構造の設計と試作評価では、その表面段差値とSn/CuバンプとCu膜の接合界面への $SiO_2$ フィラー含有樹脂の噛み込みの発生を定量評価した。その結果、 $200\sim400$  nm の表面段差を設けることで、 $SiO_2$ フィラー含有樹脂の噛み込みなくSn/CuバンプとCu 膜を接合できることを実証した。

第 5 の課題である接合基材に最適なプラズマ表面処理の検討では、未処理、Ar プラズマ表面処理、及び  $Ar/H_2(H_2$  濃度 4%)プラズマ表面処理をしたチップと基板を接合した試料のシェア強度、 $SiO_2$  フィラー含有樹脂と Cu 膜の接合部状態、及び Sn/Cu バンプと Cu 膜の接合状態を比較評価した。Ar と  $Ar/H_2$ プラ

ズマ表面処理をしたチップと基板の接合試料はいずれも未処理のそれに比べて、シェア強度は増加し、ボイドも発生しなかったが、Ar と  $Ar/H_2$ プラズマ表面処理との間には明確な差は確認されなかった。しかし、Sn/Cu バンプと Cu 膜の接合界面の断面 SEM/SIM 観察結果から、 $Ar/H_2$ プラズマ表面処理をしたチップと基板を接合した試料において、Sn と Cu の接合界面が消失し、IMC の形成が最も大きいことが分かった。この結果は、Ar のスパッタリング作用と  $H_2$  の還元作用が働く  $Ar/H_2$ ( $H_2$  濃度 4%)プラズマ表面処理が Sn/Cu バンプの Sn 表面と Cu 膜表面に存在する有機膜と酸化膜の除去に効果的であることを示している。

以上の結果から、シングルミクロンピッチのバンプと樹脂を同時に接合するハイブリッド接合に、Sn/Cu バンプの Sn の塑性変形と未硬化状態の  $SiO_2$  フィラー含有樹脂の可塑性により Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂の表面段差を吸収する Planar 構造が有効であることを示した。さらに、その接合構造の作製に関して、 $SiO_2$  フィラー含有樹脂の CMP と  $O_2/CHF_3$  プラズマエッチングを組み合わせた工法を構築した。また、接合構造を構成する Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂の材料の適正化を図った。これらを総合的に行うことにより、 $8 \mu m$  ピッチの Sn/Cu バンプと  $SiO_2$  フィラー含有樹脂を同時に接合するハイブリッド接合を最終的に実現した。

# 4.5 参考文献

- [1] Masatsugu Nimura, Masaki Ohyama, Shuichi Shoji, Mamoru Tamura, Tomoyuki Enomoto, and Akitsu Shigetou, Jun Mizuno, "3D Interconnection of Single Micron Pitch by Hybrid Bonding Technology", Extended Abstracts of the 2015 International Conference on Solid State Devices and Materials, pp. 788-789, 2015.

- [2] Masaki Ohyama, Masatsugu Nimura, Jun Mizuno, Shuichi Shoji, Mamoru Tamura, Tomoyuki Enomoto, and Akitsu Shigetou, "Hybrid Bonding of Sn/Cu Microbump and Adhesive with Silica Filler for 3D Interconnection of Single Micron Pitch", Proceedings of the 65<sup>th</sup> Electronic Components and Technology Conference, pp. 325-330, 2015.

- [3] 大山真輝, 仁村将次, 水野潤, 庄子習一, 田村護, 榎本智之, 重藤暁津, "高密度3次元実装に向けたフィラー含有樹脂とバンプのハイブリッド接合技術",

- 「エレクトロニクスにおけるマイクロ接合・実装技術」シンポジウム予稿集, 2016.

- [4] 冨田 至洋, 安藤 達也, 田中 直敬, 佐藤 知稔, 高橋 健司, "20 µm ピッチフリップチップにおける 10 µm 以下の微細間隙アンダーフィルに関する基礎検証", エレクトロニクス実装学会誌, Vol. 4, No. 7, pp.607-614, 2001.

- [5] Zhuqing Zhang and C. P. Wong, "Recent Advances in Flip-Chip Underfill: Materials, Process, and Reliability", IEEE Transactions on Advanced Packaging, Vol. 27, No. 3, 2004.

- [6] M. H. Jeon, S-K. Kang, and J. Y. Park, "Characteristics of SiO2 Etching with a C<sub>4</sub>F<sub>8</sub>/Ar/CHF<sub>3</sub>/O<sub>2</sub> Gas Mixture in 60-MHz/2-MHz Dual-frequency Capacitively Coupled Plasmas", Journal of the Korean Physical Society, Vol. 59, No. 5, pp. 3024-3030, 2011.

- [7] Pauline Ho, Justine E. Johannes, Richard J. Buss, and Ellen Meeks, "Modeling the plasma chemistry of C<sub>2</sub>F<sub>6</sub> and CHF<sub>3</sub> etching of silicon dioxide, with comparisons to etch rate and diagnostic data", Journal of Vacuum Science & Technology A, Vol. 19, No. 5, pp. 2344-2367, 2001.

- [8] Ying-Hui Wang, and Tadatomo Suga, "Effect of Low-Pressure Ar Plasma Treatment on Micro-Bump Bonding", 精密工学会春季大会学術講演会講演 論文集, pp. 381-382, 2009.

- [9] Ran He, and Tadatomo Suga, "Effects of Ar Plasma and Ar Fast Atom Bombardment (FAB) Treatments on Cu/Polymer Hybrid Surface for Wafer Bonding", Proceedings of the International Conference on Electronics Packaging, pp. 78-81, 2014.

- [10] 青柳哲理, 海老塚守之, 佐藤充弘, "プラズマ照射による大気中での Flux-less フリップチップ接合技術の開発", 第 15 回マイクロエレクトロニ クスシンポジウム予稿集, pp. 201-204, 2005.

- [11] 谷田一真, 梅本光雄, 小嶋一三, 高橋健司, "20 µm ピッチ微細 Cu バンプ接合による 3 次元チップ積層", エレクトロニクス実装学会誌, Vol. 8, No. 4, 2005.

- [12] K Sakuma, P.S. Andry, B. Dang, J. Maria, C.K. Tsang, C. Patel, S.L. Wright, B. Webb, E. Sprogis, S.K. Kang, R. Polastre, R. Horton, and J.U. Knickerbocker, "3D Chip Stacking Technology with Low-Volume Lead-Free Interconnections", Proceedings of the 57th Electronic Components and Technology Conference, pp. 627-632, 2007.

- [13] Ching-Kuan Lee, et al., "Characterization and Reliability Assessment of Solder Microbumps and Assembly for 3D IC Integration", Proceedings of the 61<sup>st</sup> Electronic Components and Technology Conference, pp.1468-1474, 2011.

- [14] Kuniaki Sueoka, et al., "Fine-pitch Solder Joining for High Density Interconnection", Proceedings of International Conference on Electronics Packaging, pp. 600-603, 2014.

- [15] 仁村将次, 佐久間克幸, 庄子習一, 水野潤, "三次元 LSI に向けたはんだと樹脂の混載接合技術と表面処理技術", 電子情報通信学会論文誌 C, Vol. J95-C, No. 11, pp. 296-303, 2012.

- [16] C. T. Ko, et al., "Structural Design, Process, and Reliability of a Wafer-Level 3D Integration Scheme with Cu TSVs Based on Micro-bump/Adhesive Hybrid Wafer Bonding", Proceedings of the 62<sup>nd</sup> Electronic Components and Technology Conference, pp. 444-449, 2012.

- [17] Jason D. Reed, et al., "High Density Interconnect at 10 μm Pitch with Mechanically Keyed Cu/Sn-Cu and Cu-Cu Bonding for 3-D Integration", Proceedings of the 60<sup>th</sup> Electronic Components and Technology Conference, pp. 846-852, 2010.

- [18] Shim J. H., Oh C. S., Lee B. J., and Lee D. N. "Thermodynamic assessment of the Sn/Cu system", Z. Metallkd. 87, pp. 205–212, 1996.

# 第5章 結論と今後の展望

#### 5.1 結論

本論文は、次世代の積層型機能性デバイスを実現するための要素技術として 必須となるシングルミクロンピッチのバンプの接合とチップ間を封止する樹脂 接合を同時に行うハイブリッド接合技術に関する研究について述べた。

次世代の積層型機能性デバイスでは、シングルミクロンピッチのバンプの接 合とチップ間の樹脂封止技術が必要とされている。しかしながら、従来の樹脂 封止技術では、10 μm 以下のピッチのバンプ間、及びチップ間の隙間に樹脂を ボイドなく充填することが困難であり、この問題を解決する新たな技術の確立 が期待されている。その 1 つの方法として、電極の周囲に有機または無機の絶 縁膜が形成された構造を用いて電極と電極、及び絶縁膜と絶縁膜を同時に接合 するハイブリッド接合技術が提案されている。これまでに電極と絶縁膜の表面 高さを揃えた平坦構造によるハイブリッド接合が報告されているが、Si 基板の 歪みや接合装置のヘッドとステージの平行不良によって接合時の荷重の不均一 が生じるため、電極と絶縁膜の各接合部において未接合部が発生する問題があ る。そこで、この問題を解決する方法として、バンプの塑性変形と未硬化樹脂 の可塑性によって接合時にバンプと樹脂の表面段差を吸収可能な接合構造を新 たに提案した。加えて、この構造を作製するために、未硬化樹脂をバンプ周囲 に形成する工法も新たに提案した。そして、この接合構造と作製方法を確立し、 シングルミクロンピッチのバンプと樹脂を同時に接合するハイブリッド接合の 実現を本研究の最終目的とした。

第2章では、Au バンプの塑性変形と未硬化樹脂の可塑性によって Au バンプと樹脂の表面段差を吸収可能な Lock and key 構造を用いたハイブリッド接合を提案した。また、この構造を用いるときに課題となる Au バンプの接合界面への未硬化樹脂の流入を防止するために、Au バンプが樹脂よりも先に接触する構造を設計、試作評価し、この構造がハイブリッド接合に有効であることを示した。しかしながら、 $O_2$ 、及び  $O_2$ /CHF $_3$  プラズマ照射による樹脂のエッチングでは、バンプの表面粗さや高さバラつき、バンプの配置による樹脂の膜厚ムラが原因で全てのバンプ上の樹脂を完全に除去することが困難になる課題が残された。

第3章では CMP(Chemical mechanical polishing)で樹脂を平坦化して得られ

る Planar 構造を用いたハイブリッド接合技術を提案した。Planar 構造は、Au バンプの塑性変形と未硬化樹脂の可塑性を利用して Au バンプと樹脂の表面段差を吸収する点において、第2章で述べた Lock and key 構造と類似するが、接合部が平坦な Planar 構造である点が大きく異なり、ファインピッチのバンプの接合構造にも対応できる特徴を有する。Planar 構造は、チップと基板に樹脂をスピンコート、ベークした後、CMP でそれぞれの樹脂を研磨することで作製され、ハイブリッド接合に有効であることを示した。この CMP 技術を用いた作製方法は工程数が少なく、バンプの表面粗さを低減し、バンプの高さを揃えることができる点において汎用性が高いため量産化に適している。

第4章では、8  $\mu$ m ピッチの Sn/Cu バンプと SiO2 フィラー含有樹脂で構成される Planar 構造を用いたハイブリッド接合を提案した。第2章と第3章で確立した接合構造の設計とその作製方法を要素技術として本章の研究に応用し、加えて接合構造を構成する材料特性の視点も取り入れてこれらを一体で設計、試作評価した。シングルミクロンピッチのバンプと樹脂を同時に接合するハイブリッド接合に、Sn/Cu バンプの Sn の塑性変形と未硬化状態の SiO2 フィラー含有樹脂の可塑性によって Sn/Cu バンプと SiO2 フィラー含有樹脂の表面段差を吸収する Planar 構造が有効であることを示した。さらに、その接合構造の作製に関して、SiO2 フィラー含有樹脂の CMP と O2/CHF3 プラズマエッチングを組み合わせた工法を構築した。また、接合構造を構成する Sn/Cu バンプと SiO2 フィラー含有樹脂の材料の適正化を図った。これらを総合的に行ったことにより、8  $\mu$ m ピッチの Sn/Cu バンプと SiO2 フィラー含有樹脂を同時に接合するハイブリッド接合を実現できた。

以上より、次世代の積層型機能性デバイスの実現の要素技術として必須であるシングルミクロンピッチのバンプの接合とチップ間を封止する樹脂接合を同時に行うハイブリッド接合を実現できることを世界に先駆けて示した。本研究で構築したハイブリッド接合技術は、半導体実装分野における高機能 3 次元積層デバイスを始め、エレクトロニクスやフォトニクスに関する多くの分野でのデバイス作製に広く応用が期待される。

# 5.2 今後の展望

今後は本研究で提案したハイブリッド接合技術の実用性を示し、実際の積層 デバイスの作製方法への応用を検討する。デバイスを製品として実用化するためには信頼性試験の通過が必須であり、バンプ及び樹脂の特性の最適化が必要 となる。また、量産レベルで接合構造の作製方法及び接合方法を確立するには、 新たな製造装置の開発も不可欠である。すなわち、デバイス(構造や材料)、工法、 及び製造装置の全てを総合的に開発することが重要となる。

信頼性試験を通過するために、達成しなければならない課題とその解決方法について述べる。信頼性試験ではバンプの接合部でのクラックやマイグレーション、樹脂の接合部での剥離の発生等が評価される。シングルミクロンサイズのバンプの接合部の信頼性に関しては研究報告例が少なく、接合部の金属組成と信頼性試験結果の定量的な評価が必要である。接合部の金属材料には、信頼性試験中のバンプの接合部に生じる応力に耐える機械特性に加えて、サーマル及びエレクトロマイグレーション[1]耐性も必要である。これらの課題を達成するために、バンプの接合部に Cu/Sn 合金[2]、Cu/Ni/In 合金[3]、Cu/In/Sn 合金[4]等を用いる接合方法がこれまでに提案されている。Cu/Sn 合金は第 4 章のバンプの接合部の構成と同じであるが、Cu<sub>6</sub>Sn<sub>5</sub> は機械的に脆いためその層をすべて Cu<sub>3</sub>Sn にすることで機械特性とマイグレーション耐性が向上すると報告されている。その実現には、接合時の温度、及び Cu と Sn の膜厚の最適化が必要となる。また、このことと同時に樹脂の機械特性の最適化も同時に進める必要がある[5]。

次に、接合構造の作製方法及び製造装置の課題とその解決方法について述べる。第3章と第4章で述べた樹脂の CMP はチップレベルで行なわれたが、この作製方法の実用化にはウェハレベルで均一に樹脂を研磨することが要求される。また、樹脂のエッチングにも同様にエッチングの均一性が要求される。したがって、研磨量とエッチング量のウェハ面内及びロットばらつきも考慮した接合構造の設計が必須となる。このことについては、第4章で述べたバンプと樹脂の表面段差とバンプ接合界面への樹脂の噛み込みの定量評価結果から、仮にバンプと樹脂の表面段差にばらつきがあっても、ハイブリッド接合を実現できることが示唆されている。製造装置に関しては、ウェハレベルで樹脂を均一に研磨できる CMP 装置開発、及び超高位置精度のフリップチップボンダー開発が必要になる。フリップチップボンダーはチップを1枚ずつ実装するためにスループットがボトルネックであるが、これを解決するために複数チップを一括

で接合するギャングボンダー及び一括接合方法の開発も進められている[6]。一方で、実装の高スループット化には真空チャンバー付きウェハボンダーを用いてウェハを積層する工法も開発が進められている[7]。真空チャンバー内で接合を行うことができるため、樹脂の接合部での空気の巻込みによるボイドの発生とバンプの接合部の酸化を防ぐことができる。表 5.1 にチップ積層方法とウェハ積層方法の比較表を示す[8]。チップ積層において、チップ上にチップを積層する場合は Chip on Wafer と呼ばれる。ウェハ積層は Wafer on Wafer と呼ばれる。チップ積層方法は、ウェハ積層方法より歩留まりが高いがスループットは低い。一方、ウェハ積層方法はスループットが高いが、良品デバイスと不良品デバイスが混在して積層されるため歩留まりは低くなる。加えて、同一サイズのデバイスの積層に限られる。以上からデバイスの設計、スループット、歩留まり、製造コスト等を総合的に判断して、作製する積層デバイスに適した接合装置を開発する必要がある。

本研究で構築したシングルミクロンピッチのバンプの接合とチップ間を封止する樹脂接合を同時に行うハイブリッド接合技術が将来の情報社会を支える高機能積層デバイスの実現に貢献することを期待している。

|         | Chip on Chip | Chip on Wafer | Wafer on Wafer |

|---------|--------------|---------------|----------------|

| スループット  | 低            | 中             | 哥              |

| 歩留まり    | 高            | 高             | 低              |

| 異なるサイズの | 可            | H             | 不可             |

| デバイスの積層 | ΗJ           | 印             | 个円             |

表 5.1. チップ積層方法とウェハ積層方法の比較[8]

## 5.3 参考文献

- [1] Yasumitsu Orii, Kazushige Toriyama, Sayuri Kohara, Hirokazu Noma, Keishi Okamoto, Keisuke Uenishi, "Effect of preformed Cu-Sn IMC Layer on Electromigration Reliability of Solder Capped Cu Pillar Bump Interconnection on an organic substrate", Proceedings of IEEE CPMT Symposium, pp. 1-4, 2012.

- [2] 谷田一真, 梅本光雄, 小嶋一三, 高橋健司, "20 µm ピッチ微細 Cu バンプ接合による 3 次元チップ積層", エレクトロニクス実装学会誌, Vol. 8, No. 4,

2005.

- [3] K. Sakuma, K. Sueoka, S. Kohara, K. Matsumoto, H. Noma, T. Aoki, Y. Oyama, H. Nishiwaki, P.S. Andry, C.K. Tsang, J.U. Knickerbocker, and Y. Orii, "IMC Bonding for 3D Interconnection", Proceedings of the 65th Electronic Components and Technology Conference, pp. 864-871, 2010.

- [4] Ruoh-Ning Tzeng, et al., "Low Temperature Bonding of Sn/In-Cu Interconnects for Three-Dimensional Integration Applications", Proceedings of Interconnect Technology Conference, pp. 1-3, 2013.

- [5] 冨田 至洋, 安藤 達也, 田中 直敬, 佐藤 知稔, 高橋 健司, "20 μm ピッチフリップチップにおける 10 μm 以下の微細間隙アンダーフィルに関する基礎検証", エレクトロニクス実装学会誌, Vol. 4, No. 7, pp. 607-614, 2001.

- [6] Toshihisa Nonaka, Yuta Kobayashi, Noboru Asahi, Shoichi Niizeki, Koichi Fujimaru, Yoshiyuki Arai, Toshifumi Takegami, Yoshinori Miyamoto, Masatsugu Nimura, and Hiroyuki Niwa, "High Throughput Thermal Compression NCF Bonding", Proceedings of the 64<sup>th</sup> Electronic Components and Technology Conference, pp. 913-918, 2014.

- [7] F. Liu, et al., "A 300-mm wafer-level three-dimensional integration scheme using tungsten through-silicon via and hybrid Cu-adhesive bonding", Proceedings of International Electron Devices Meeting, pp. 1-4, 2008.

- [8] Jihwan. Hwang, Jongyeon. Kim, Woonseong. Kwon, Unbyoung. Kang, Taeje. Cho, and Sayoon. Kang, "Fine Pitch Chip Interconnection Technology for 3D Integration", Proceedings of the 60<sup>th</sup> Electronic Components and Technology Conference, pp. 1399-1403, 2010.

# 謝辞

本研究では、試料作製から実装、解析まで多くの方々のご指導とご協力を頂きました。ここに謝意を表します。

社会人コースの博士号取得の機会とご支援、終始丁寧なご指導を頂きました早稲田大学理工学術院 庄子習一教授、早稲田大学ナノ・ライフ創新研究機構水野潤教授に心から感謝致します。学位審査において貴重なご意見、ご指導を頂きました早稲田大学理工学術院 川原田洋教授、早稲田大学理工学術院 谷井孝至教授に心から感謝致します。

試料作製や解析技術について多くの助言を頂きました早稲田大学ナノ・ライフ創新研究機構の齋藤美紀子教授、由比藤勇准教授、加藤邦男次席研究員に深く感謝致します。

研究室において研究生活を支えて頂きました関口哲志教授、錦織玲子秘書、 日頃から実験に関する議論をさせて頂きました篠原秀敏博士、尹棟鉉博士、笠 原崇史博士、岡田愛姫子氏、大山真輝氏、学生諸氏に深く感謝致します。

共同研究として長期間にわたり材料開発と実験結果に対する深い議論をさせて頂きました日産化学工業株式会社 榎本智之氏、田村護氏、荻野浩司氏に深く感謝致します。また、本研究の初期から研究全般において多大なご指導を頂きました IBM T.J. Watson Research Center 佐久間克之博士と国立研究開発法人物質・材料研究機構 重藤暁津博士に深く感謝致します。

博士号取得の機会を頂き、会社での業務と大学での研究の両立を支えて頂きました東レエンジニアリング株式会社 岩出卓氏、野上義生氏、平田肇氏、寺田豊治氏、新井義之氏、竹上敏史氏、朝日昇氏、恩地卓也氏、宮本芳範氏、水谷義人氏、今井宏一氏、青木進平氏、安井弘和氏、川上幹夫氏、安齋貴志氏に深く感謝致します。

# 業績一覧

# 查読付論文

- [1] <u>Masatsugu Nimura</u>, Jun Mizuno, Shuichi Shoji, Katsuyuki Sakuma, Hiroshi Ogino, Tomoyuki Enomoto, and Akitsu Shigetou, "Hybrid Au-Adhesive Bonding Technology Using Planar Adhesive Structure for 3D LSI", IEEE transaction on Components, Packaging and Manufacturing Technology, Vol.4, Issue 5, pp.762-768, 2014.

- [2] <u>Masatsugu Nimura</u>, Shigetou Akitsu, Katsuyuki Sakuma, Hiroshi Ogino, Tomoyuki Enomoto, Jun Mizuno and Shuichi Shoji, "Study on Hybrid Au-Undefill Resin Bonding Method with Lock-and-Key Structure for 3D Integration", IEEE transaction on Components, Packaging and Manufacturing Technology, Vol.3, Issue 4, pp.558-565, 2013.