### マルチコアプロセッサにおける Cプログラムの自動並列化と低消費電力化 に関する研究

Studies on Automatic Parallelization and Low Power Optimization of C Programs on Multicore Processors

2011年2月

間瀬正啓

### マルチコアプロセッサにおける Cプログラムの自動並列化と低消費電力化 に関する研究

Studies on Automatic Parallelization and Low Power Optimization of C Programs on Multicore Processors

2011年2月

早稲田大学大学院基幹理工学研究科 情報理工学専攻 先端プロセッサ構成研究

間瀬正啓

# 目 次

| 第1章 | 序論 1                                |    |  |

|-----|-------------------------------------|----|--|

| 1.1 | 本研究の目的と研究背景                         |    |  |

| 1.2 | 本論文の構成                              | 23 |  |

| 第2章 | OSCAR 自動並列化コンパイラ                    | 27 |  |

| 2.1 | はじめに                                | 28 |  |

| 2.2 | マルチグレイン並列処理                         | 30 |  |

|     | 2.2.1 マクロタスク生成                      | 30 |  |

|     | 2.2.2 粗粒度タスク並列性抽出                   | 30 |  |

|     | 2.2.3 データローカライゼーション                 | 32 |  |

|     | 2.2.4 プロセッサグループへのマクロタスク割り当て         | 33 |  |

| 2.3 | OSCAR コンパイラの構成と OSCAR API           | 36 |  |

|     | 2.3.1 OSCAR マルチコアアーキテクチャ            | 37 |  |

|     | 2.3.2 OSCAR API 指示文                 | 37 |  |

|     | 2.3.3 OSCAR API <b>を用いたコンパイルフロー</b> | 39 |  |

| 2.4 | 関連研究                                | 40 |  |

| 2.5 | まとめ                                 | 41 |  |

| 第3章 | ポインタ解析                              | 43 |  |

| 3.1 | はじめに                                | 44 |  |

| 3.2 | 基準と    | なるポインタ解析                                         | 47 |

|-----|--------|--------------------------------------------------|----|

|     | 3.2.1  | Points-to 解析                                     | 47 |

|     | 3.2.2  | Flow-Sensitive <b>ポインタ解析</b>                     | 48 |

|     | 3.2.3  | Context-Sensitive <b>ポインタ解析</b>                  | 50 |

|     | 3.2.4  | Heap-Sensitive <b>ポインタ解析</b>                     | 50 |

|     | 3.2.5  | Field-Sensitive ポインタ解析                           | 51 |

| 3.3 | Elemen | nt-Sensitive ポインタ解析                              | 51 |

|     | 3.3.1  | element alias 属性                                 | 52 |

|     | 3.3.2  | 伝達関数                                             | 52 |

|     | 3.3.3  | 交わり (meet) 演算子 /                                 | 54 |

|     | 3.3.4  | インタープロシージャ解析                                     | 55 |

|     | 3.3.5  | Cycle-Sensitive 不使用時の Element-Sensitive ポインタ解析   |    |

|     |        | の適用例                                             | 55 |

| 3.4 | Elemen | nt-Sensitive ポインタ解析と Cycle-Sensitive ポインタ解析の併用   | 56 |

|     | 3.4.1  | Element-Sensitive ポインタ解析と Aging の併用例             | 57 |

| 3.5 | Elemen | nt-Sensitive ポインタ解析の自動並列化への利用                    | 59 |

|     | 3.5.1  | イタレーション空間における依存解析                                | 60 |

|     | 3.5.2  | イタレーション空間における依存解析の例                              | 60 |

| 3.6 | マルチ    | コアシステム上での性能評価                                    | 61 |

|     | 3.6.1  | 自動並列化を適用する際のコンパイル手順                              | 62 |

|     | 3.6.2  | 評価対象プログラム・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・    | 62 |

|     | 3.6.3  | 評価環境                                             | 63 |

|     | 3.6.4  | 自動並列化による処理性能・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 63 |

|     | 3.6.5  | OSCAR <b>コンパイラによる自動並列化結果</b>                     | 65 |

| 27  | 問油加    | · · · · · · · · · · · · · · · · · · ·            | 67 |

| 3.8 | まとめ                                | 70 |

|-----|------------------------------------|----|

| 第4章 | Parallelizable C                   | 71 |

| 4.1 | はじめに                               | 72 |

| 4.2 | Parallelizable C の概念               | 73 |

|     | 4.2.1 C <b>言語のコーディングガイドライン</b>     | 74 |

|     | 4.2.2 対象のコンパイラの解析精度                | 74 |

| 4.3 | Parallelizable C のコーディングルール        | 75 |

|     | 4.3.1 C言語記述におけるルール                 | 75 |

|     | 4.3.2 外部関数に関するヒント情報                | 78 |

| 4.4 | Parallelizable C へのプログラム書き換え       | 79 |

|     | 4.4.1 書き換え項目とコード変更量                | 79 |

|     | 4.4.2 コード書き換え内容                    | 80 |

| 4.5 | OSCAR <b>自動並列化コンパイラの概要</b>         | 80 |

| 4.6 | マルチコアシステム上での性能評価                   | 81 |

|     | 4.6.1 評価方法                         | 82 |

|     | 4.6.2 評価対象プログラム                    | 83 |

|     | 4.6.3 評価環境                         | 83 |

|     | 4.6.4 自動並列化による処理性能                 | 84 |

|     | 4.6.5 OSCAR <b>コンパイラによる自動並列化結果</b> | 87 |

| 4.7 | 関連研究                               | 91 |

| 4.8 | まとめ                                | 94 |

| 第5章 | 低消費電力化制御                           | 95 |

| 5.1 | はじめに                               |    |

|     | マルチグレイン並列処理                        | 07 |

|     | 5.2.1 | マクロタスク生成・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | . 97  |

|-----|-------|----------------------------------------------|-------|

|     | 5.2.2 | マクロタスクグラフ生成                                  | . 98  |

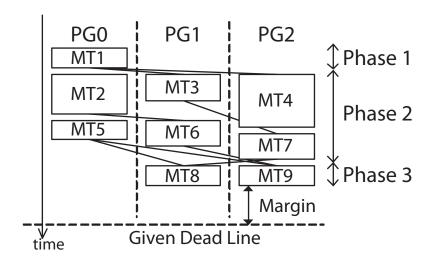

|     | 5.2.3 | マクロタスクスケジューリング                               | . 98  |

| 5.3 | OSCA  | $R$ コンパイラによる低消費電力化手法 $\ldots$                | . 98  |

|     | 5.3.1 | コンパイル時における低消費電力化手法                           | . 99  |

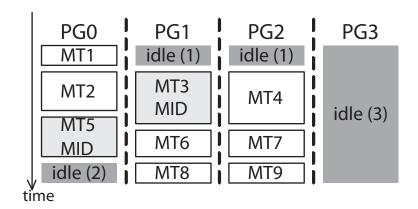

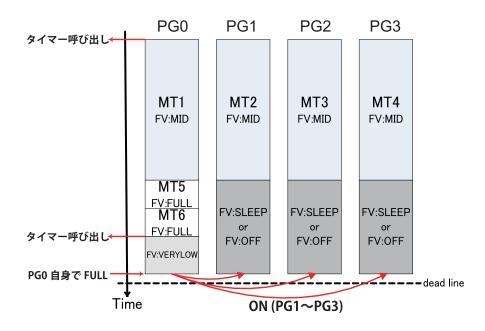

|     | 5.3.2 | 実行時負荷不均衡に対する低消費電力化手法                         | . 101 |

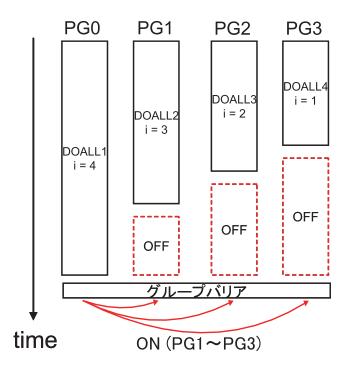

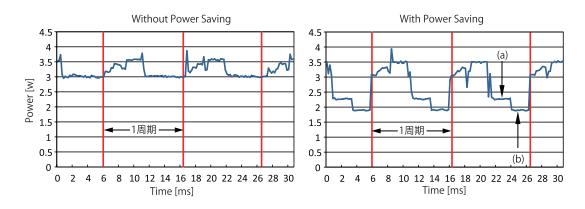

|     | 5.3.3 | デッドライン時刻までの待機電力最小化                           | . 104 |

| 5.4 | OSCA  | R API における電力制御用指示文                           | . 106 |

|     | 5.4.1 | 電力制御およびリアルタイム処理向け指示文                         | . 107 |

| 5.5 | 性能評   | 4価                                           | . 107 |

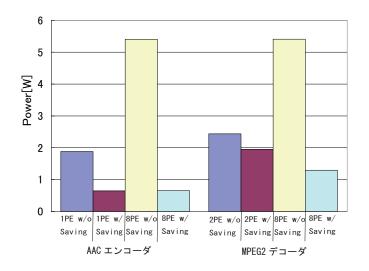

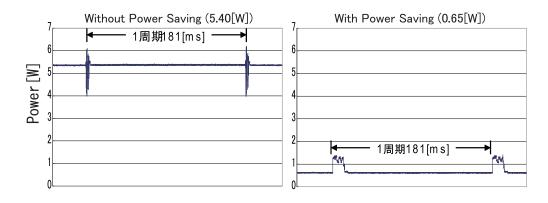

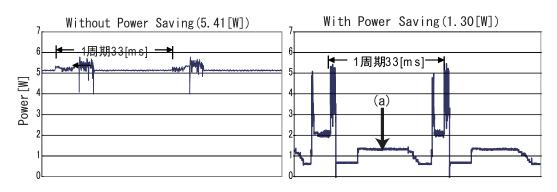

|     | 5.5.1 | 情報家電用マルチコア RP2                               | . 108 |

|     | 5.5.2 | 消費電力評価条件                                     | . 110 |

|     | 5.5.3 | 最速実行モードの評価                                   | . 110 |

|     | 5.5.4 | リアルタイム制約モードの評価                               | . 112 |

| 5.6 | 関連研   | 穷                                            | . 116 |

| 5.7 | まとめ   | )                                            | . 118 |

| 第6章 | ソフト   | - ウェアコヒーレンシ制御                                | 119   |

| 6.1 | はじめ   |                                              | . 120 |

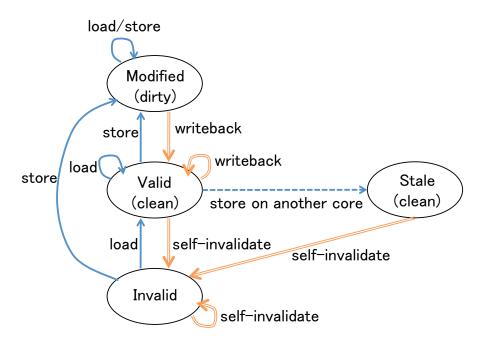

| 6.2 | ソフト   | ・ウェアコヒーレンシ制御                                 | . 122 |

|     | 6.2.1 | ノンコヒーレントキャッシュアーキテクチャ                         | . 122 |

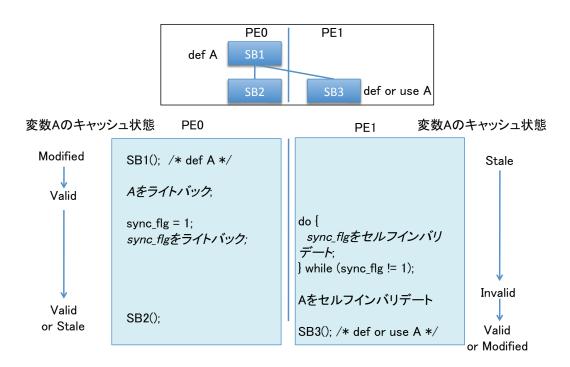

|     | 6.2.2 | ソフトウェアによるキャッシュコヒーレントプロトコル                    | . 124 |

| 6.3 | コンバ   | ペイラによるソフトウェアコヒーレンシ制御手法                       | . 126 |

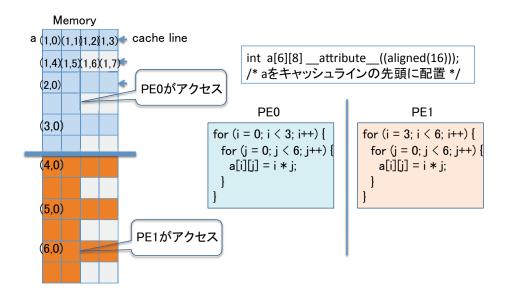

|     | 6.3.1 | 階層的粗粒度タスク並列処理                                | . 126 |

|     | 6.3.2 | 並列処理階層の決定                                    | . 126 |

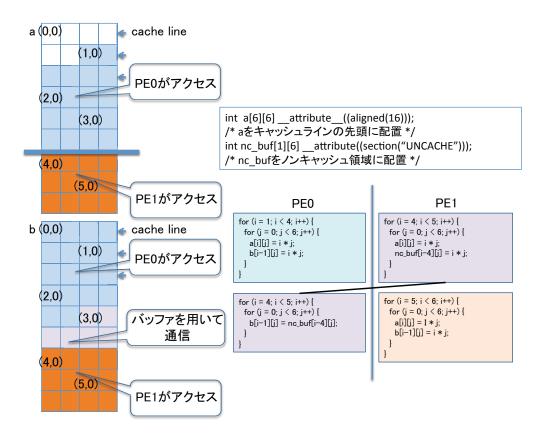

|     | 6.3.3 | 変数配置のアラインメント                                 | . 127 |

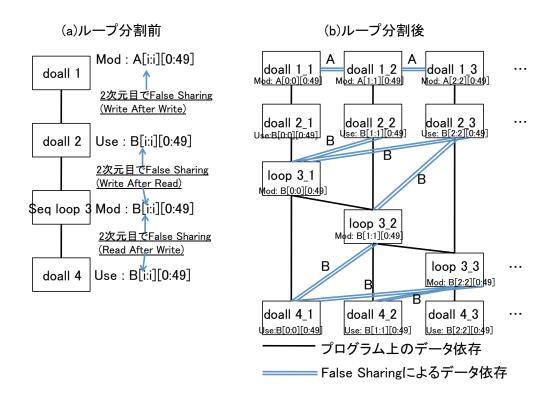

| 6.3.4 | フォルスシェアリングの解析                                                                           | . 128                                                                                                                                                                                                                                    |

|-------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.3.5 | フォルスシェアリングの回避                                                                           | . 130                                                                                                                                                                                                                                    |

| 6.3.6 | キャッシュのセルフインバリデートおよびライトバック操作                                                             |                                                                                                                                                                                                                                          |

|       | の挿入                                                                                     | . 133                                                                                                                                                                                                                                    |

| OSCA  | R API におけるキャッシュ制御用指示文                                                                   | . 133                                                                                                                                                                                                                                    |

| 6.4.1 | ノンコヒーレントキャッシュ向け指示文                                                                      | . 134                                                                                                                                                                                                                                    |

| 性能評   | '価                                                                                      | . 135                                                                                                                                                                                                                                    |

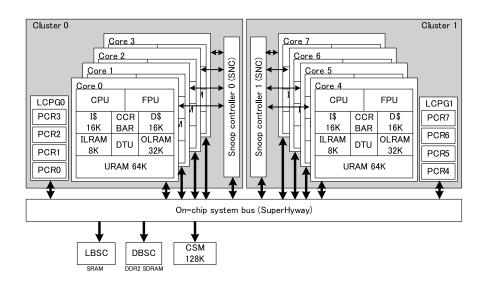

| 6.5.1 | 情報家電用マルチコア RP2                                                                          | . 135                                                                                                                                                                                                                                    |

| 6.5.2 | 評価条件                                                                                    | . 136                                                                                                                                                                                                                                    |

| 6.5.3 | コンパイラの実装・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                            | . 137                                                                                                                                                                                                                                    |

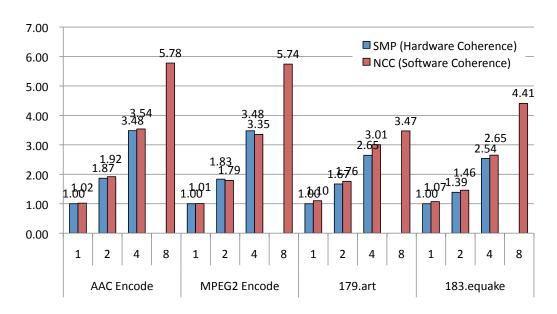

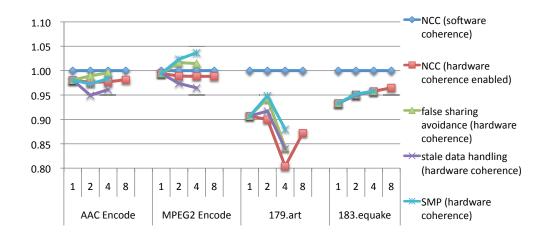

| 6.5.4 | 並列処理性能                                                                                  | . 137                                                                                                                                                                                                                                    |

| 6.5.5 | ソフトウェアコヒーレンシ制御による影響                                                                     | . 139                                                                                                                                                                                                                                    |

| 関連研   | 究                                                                                       | . 141                                                                                                                                                                                                                                    |

| まとめ   |                                                                                         | . 143                                                                                                                                                                                                                                    |

| 結論    |                                                                                         | 145                                                                                                                                                                                                                                      |

| 本研究   | により得られた成果....................................                                           | . 146                                                                                                                                                                                                                                    |

| 今後の   | ·<br>課題                                                                                 | . 148                                                                                                                                                                                                                                    |

|       |                                                                                         |                                                                                                                                                                                                                                          |

| 试     |                                                                                         | 150                                                                                                                                                                                                                                      |

|       |                                                                                         | 167                                                                                                                                                                                                                                      |

| 党業績   |                                                                                         | 169                                                                                                                                                                                                                                      |

|       | 6.3.5<br>6.3.6<br>OSCA<br>6.4.1<br>性 6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.5.5<br>関ま 結研 | 6.3.5 フォルスシェアリングの回避 6.3.6 キャッシュのセルフインパリデートおよびライトパック操作 の挿入 OSCAR APIにおけるキャッシュ制御用指示文 6.4.1 ノンコヒーレントキャッシュ向け指示文 性能評価 6.5.1 情報家電用マルチコア RP2 6.5.2 評価条件 6.5.3 コンパイラの実装 6.5.4 並列処理性能 6.5.5 ソフトウェアコヒーレンシ制御による影響 関連研究 まとめ 結論 本研究により得られた成果 今後の課題  就 |

# 図目次

| 2.1 | 階層的マクロタスク定義                                        | 31 |

|-----|----------------------------------------------------|----|

| 2.2 | マクロフローグラフとマクロタスクグラフ                                | 32 |

| 2.3 | データローカライゼーションにおけるループ整合分割                           | 34 |

| 2.4 | 階層的コード生成イメージ                                       | 36 |

| 2.5 | OSCAR マルチコアアーキテクチャ                                 | 38 |

| 2.6 | OSCAR コンパイラを用いたコンパイルフロー                            | 39 |

| 3.1 | 従来のポインタ解析では識別できないプログラム例                            | 45 |

| 3.2 | プログラムと Points-to 集合の例                              | 48 |

| 3.3 | element alias 属性の束 (lattice)                       | 52 |

| 3.4 | gen における element alias 属性計算アルゴリズム                  | 54 |

| 3.5 | Cycle-Sensitive を利用しないElement-Sensitive ポインタ解析の適用例 | 57 |

| 3.6 | Element-Sensitive ポインタ解析と Aging の併用例               | 59 |

| 3.7 | ポインタ解析を利用したイタレーション空間における依存解析結果                     | 61 |

| 3.8 | IBM p5 550Q における OSCAR コンパイラによる自動並列化結果 .           | 65 |

| 4.1 | lbm におけるループ中でのポインタの更新の除去                           | 81 |

| 4.2 | hmmer におけるバッファの使い回しの除去                             | 82 |

| 4.3 | IBM p5 550Q における OSCAR コンパイラによる自動並列化結果 .           | 86 |

| 4.4 | Intel Core i7 920 における OSCAR コンパイラによる自動並列化結果       | 86 |

| 4.5  | ルネサステクノロジ / 日立製作所 / 早稲田大学 RP2 における OS-                |     |

|------|-------------------------------------------------------|-----|

|      | CAR コンパイラによる自動並列化結果                                   | 87  |

| 4.6  | hmmer における主要処理ループ構造                                   | 90  |

| 4.7  | hmmer における主要処理ループのデータローカライゼーション                       | 91  |

| 5.1  | マクロタスクのスケジューリング結果の例                                   | 102 |

| 5.2  | 周波数・電圧制御の結果の例・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・      |     |

| 5.3  | 負荷不均衡のある並列ループに対する低消費電力化手法の適用例                         |     |

| 5.4  | リアルタイム制約モードの適用例                                       |     |

| 5.5  | 本手法で用いた OSCAR API                                     |     |

| 5.6  | RP2 <b>の構成図</b>                                       |     |

|      |                                                       |     |

| 5.7  | 最速実行モードにおける実行時間                                       |     |

| 5.8  | 最速実行モードにおける消費エネルギー                                    |     |

| 5.9  | art の電力波形                                             |     |

|      | リアルタイム制約モードでの平均電力・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |     |

|      | AAC エンコーダにおける電力波形                                     |     |

| 5.12 | MPEG2 デコーダにおける電力波形                                    | 116 |

| 6.1  | ノンコヒーレントキャッシュアーキテクチャ                                  | 123 |

| 6.2  | ソフトウェアによるキャッシュコヒーレントプロトコル                             | 125 |

| 6.3  | 階層的粗粒度タスク並列処理のイメージ                                    | 127 |

| 6.4  | 分割後の部分ループに関するフォルスシェアリングの検出                            | 129 |

| 6.5  | 配列のパディングによるフォルスシェアリングの回避                              | 131 |

| 6.6  | キャッシュライン境界に整合したループ分割とノンキャッシャブル                        |     |

|      | バッファを用いた通信の生成                                         | 132 |

| 6.7  | キャッシュのセルフインバリデート及びライトバック操作指示の挿入                       | 134 |

| 6.8  | 情報家電用マルチコア RP2 のブロック図      | 136 |

|------|----------------------------|-----|

| 6.9  | RP2 <b>における並列処理性能</b>      | 138 |

| 6.10 | ソフトウェアコヒーレンシ制御における性能への影響要因 | 141 |

# 表目次

| 3.1 | 評価環境                             | 63  |

|-----|----------------------------------|-----|

| 4.1 | Parallelizable C への書き換え項目とコード変更量 | 79  |

| 4.2 | 評価環境                             | 84  |

| 5.1 | RP2 <b>の電力状態</b>                 | 109 |

# 第1章

## 序論

### 1.1 本研究の目的と研究背景

組込み機器から PC,スーパーコンピュータに至るあらゆる情報機器において1チップ上に複数のプロセッサコアを集積したマルチコアプロセッサの普及が進んでおり,チップ内に集積するコア数の増加による高性能・低消費電力化が期待されている.半導体集積度の向上は続いているが,動作周波数向上の限界,命令レベル並列性の限界,プロセッサとメモリの速度差の乖離等の要因によりシングルプロセッサ性能の向上は頭打ちとなっている.特に,プロセッサの高周波数動作による発熱や電力消費は大きな問題となっており,消費電力を抑えつつ高性能を実現可能なマルチコアプロセッサの普及が進んでいる.

一方で、マルチコアプロセッサを含む、マルチプロセッサシステムを用いて高性能・低消費電力を実現するためには、並列化を含む高度な最適化技術を駆使したソフトウェア開発が必須となる。この並列ソフトウェア開発では、ループレベルの並列性のみならずプログラム中の複数レベルの並列性を利用した並列処理、キャッシュやローカルメモリを有効活用するためのデータローカリティ最適化、および低消費電力化のための周波数・電圧制御やクロック・電源制御が必要となる。しかしながら、並列処理の高度な専門知識を用いたプログラミングは、一般のアプリケーションプログラム開発者には難易度が高く、長期間の性能チューニングを要する。そのため、並列ソフトウェア開発の生産性向上が求められており、それを全自動で実現可能な自動並列化コンパイラの利用が求められている。

従来よりプログラム全域からの適切な粒度の並列性抽出,プロセッサ近傍の高速キャッシュメモリあるいはローカルメモリの最適利用を実現するための自動並列化コンパイラの研究・開発が行われてきた[Wol96, EHP98, HAA+96].これらの研究・開発の大部分はプログラム中のループ部分の並列化を対象としたものであり,現在までに様々なループ並列性解析手法やリストラクチャリング手法が開発されている.マルチプロセッサシステムの更なる実効性能向上のためには,従来のルー

プ並列性に加え,ループ間やサブルーチン間といった粗粒度タスク並列性や,基本ブロック内での命令・ステートメント間の近細粒度並列性などの複数レベルの並列性を利用することが必須である.OSCAR コンパイラ [本多 90, KHM+92, 笠原 03]では粗粒度タスク並列処理とループ並列処理および近細粒度並列処理を組み合わせたマルチグレイン並列処理を実現しており,さらにデータローカリティ最適化 [吉田 94, 石坂 02] や低消費電力化 [白子 06] を実現している.

自動並列化に関する研究は FORTRAN 言語の科学技術計算を主な対象として成 果を上げてきた.近年のマルチコアプロセッサの普及に伴い,ハイパフォーマン スコンピューティングのみならず組込み分野等でも自動並列化の需要が高まって おり,それに伴い組込み分野で標準的に利用されている C 言語を対象とした自動 並列化が強く求められている.しかしながら,C言語でプログラムを記述する際 にはポインタを多用した柔軟な記述が可能であり、自動並列化を含めたコンパイ ラによる最適化が困難となっている.Cプログラムに対して自動並列化を適用す るには、コンパイラによりポインタ変数がどのメモリ領域を指し示しているかを 解析するポインタ解析が必須となる.ポインタ解析の実装においては解析精度と 解析効率を両立したポインタ解析手法の実現が問題となっており [Hin01], 自動並 列化に有効な解析精度を効率的に得ることができるポインタ解析手法が必要とな る.また,ポインタ解析を利用しても C プログラムのあらゆる記述に対する完璧 な解析は事実上不可能なため,ユーザプログラマによるプログラム記述方法によ る対処,すなわち自動並列化コンパイラを有効利用するためのプログラミングモ デルが必要となる.そして,近年のプロセッサの低消費電力化への要求から,プ ロセッサハードウェアが備える周波数・電圧制御やクロック・電源遮断等の低消費 電力機能をソフトウェアにより適切に制御することによる低消費電力化が求めら れている.さらに,ハードウェアによるコヒーレントキャッシュのみならず,ソフ トウェア制御のコアローカルメモリ (スクラッチパッドメモリ) や、ソフトウェア

でコヒーレンシを制御するノンコヒーレントキャッシュ等,さまざまなメモリ構成のアーキテクチャへの最適化が求められており,特にソフトウェアによるコヒーレンシ制御が重要な課題となっている.

ポインタ解析に関しては多くの研究がなされており、その精度と効率について多 くの議論がなされている[HinO1].現在では高い精度の解析を効率的に行う手法が 確立されつつあり、これらのポインタ解析手法はコンパイラによる定数伝搬や部分 冗長性の除去等の一般的な最適化、プログラムのバグ検出ツールへの応用等で大き な成果を上げている.しかしながら,科学技術計算やメディア処理アプリケーショ ンのアルゴリズムは潜在的に高い並列性を持っていながら,従来のポインタ解析技 術では並列性の自動抽出にはしばしば不十分なことがある. 例えば, アルゴリズム 上は多次元配列として扱うことが可能なデータ構造を、ポインタへのポインタと メモリ動的確保を行うループの記述により実装する場合がある、このようなデー タ構造に対して従来のポインタ解析の適用を考えた場合,配列の各要素の情報が 配列全体で単一の情報に縮退されてしまうため,コンパイラによる依存解析がで きず,自動並列化が阻害されてしまう.そこで,本研究では科学技術計算やメディ ア処理アプリケーション等の自動並列化が特に有効と考えられるアプリケーション プログラムで頻出するプログラム記述に対して特に有効なポインタ解析手法を提 案する. Flow-Sensitive[EGH94, WL95, Kah08, HL09], Context-Sensitive[EGH94, WL95, WL04, NKH04, LLA07, Kah08, HL09, Heap-Sensitive[NKH04, LLA07], Field-Sensitive [PKH04, LLA07] ポインタ解析を基準となるポインタ解析精度とし て採用し,さらにこれらに加えて,従来あまり議論されていなかったヒープを確保 するループのイタレーションごとの精度を持たせる Cycle-Sensitivity[RRH08], 配 列の要素ごとに精度を持たせる Element-Sensitivity [WFPS02, 間瀬 10] について焦 点を当てる.本論文では新たに Element-Sensitive ポインタ解析を提案し,C プロ グラムで頻出するパターンの自動並列化を実現する.

高い精度のポインタ解析を効率的に行うことでコンパイラによる自動並列化を 利用することで、ユーザプログラマの並列ソフトウェア開発の負担を大きく低減 できると考えられる.しかしながら, C 言語のあらゆる記述に対してポインタの 指し先を静的に特定するのは事実上不可能となっており、自動並列化コンパイラ のようなツールを有効活用するためには、用途に応じてコーディングガイドライ ンにより記述の自由度を制限することが必要となる. MISRA-C[MIS04] は主に車 載ソフトウェア向けの高信頼性,高安全性,高移植性を目的としたコーディング ガイドラインであり、産業界で広く普及しておりコーディングガイドラインを遵 守しているかどうかを確認するチェッカツールも市販されている.マルチプロセッ サ向けの自動並列化においては , IMEC によるマルチプロセッサ向けのコーディン グガイドラインである Clean C[Cle] が提案されている.また, Hwuら [HRU+07] により assertion 等によるヒント情報を用いて自動並列化コンパイラを有効利用す る暗黙的な並列プログラミングモデルが提案されており、逐次プログラミングの ガイドラインと補完的に利用可能と考えられる.しかしながら,このようなガイ ドラインを利用した場合の有用性については、実際に自動並列化フレームワーク を用いた評価は行われていない.そこで,本論文ではコーディングガイドライン として Parallelizable C を提案するとともに、実際にプログラムの書き換えを行い、 様々なマルチコアプロセッサにおいて自動並列化結果の性能評価を行うことによ り有用性を示す.

並列処理による高い処理性能のみならず,コンピュータシステムの低消費電力化が求められており,特に組込み機器において低消費電力化への要求が強く,ハイパフォーマンスコンピューティングにおいてもシステム全体の消費電力増加が大きな問題となっている.そのため,処理性能の向上に加え,増加する消費電力をいかに抑えるかが大きな課題となっており,本論文ではコンパイラによる低消費電力化手法の提案と,その実マルチコアにおける評価を行う.その際に,コン

パイラの手法と併せて,コード生成の際に利用可能な並列処理 API を併せて提案 することで、様々なマルチコアプロセッサ上での低消費電力化制御を可能とする、 低消費電力化に関して,従来から様々な手法が提案されている.例えばキャッシュ ミス回数測定用カウンタや命令キューなどのハードウェアサポートにより実行時 にプログラム中の各フェーズにおける負荷を判断し,不要なリソースを停止する 手法 [ABD+03] や,計算資源の各部分に対して実行時の負荷に応じた周波数・電 圧制御 (FV 制御) を行う手法 [WJMC04] や , ループイタレーションレベルのプロ セッサ間の負荷不均衡に対して,実行時のハードウェアサポートにより電力制御 を行う Thrifty Barrier [LMH04] などがある.しかしながら,これらの実行時の情 報を利用した手法では,プログラム全域にわたるグローバルな消費電力の最適化 は難しく,局所的な最適化にとどまってしまう.また,実行時電力制御のための 処理やハードウェア追加が必要となるため遅延が大きいという欠点がある.この ような手法に対して、コンパイル時の静的な情報に基づく低消費電力化手法では、 プログラムの解析による詳細な情報を利用することができるため、よりきめ細や かな電力制御が可能となり、プログラム全域にわたる消費電力の最適化が実現で きる.コンパイラ制御によるシングルプロセッサ向けの低消費電力化手法 [HK03] が提案されている、しかしながら、この手法はシングルプロセッサのみを対象と しており、マルチコアプロセッサ向けの並列処理と電力制御との両立を実現でき ていない、マルチコアプロセッサ向けの OSCAR コンパイラではマルチグレイン 並列処理による並列性抽出に加え、プログラムの各部分に対するコアごとの適切 な動作周波数/電圧および電源遮断のタイミングを決定し,必要な処理性能を維持 しつつ電力を低減させている [白子 06] . 本研究では , この OSCAR コンパイラに よる低消費電力化機能を実際にマルチコアプロセッサ上で適用するための API を 策定し、さらに低消費電力化機能を拡張して、負荷不均衡がある場合や、リアル タイム処理においても適用可能とする.

#### 1.1. 本研究の目的と研究背景

現在主流の4から8コア程度のマルチコアでは主記憶共有型のマルチプロセッサ システム (SMP) が一般的であるが、そのキャッシュコヒーレンシ制御機構のハー ドウェアは,プロセッサコア数の増加に伴い,その実装が回路規模的にも消費電力 的にも困難となることが知られている [CSG99] . そのため , 今後コア数が 32 コア から64コア以上のメニーコアとなっていくと,共有メモリ空間とコア毎のコヒー レンシ制御機能を持たないキャッシュ上でも、ソフトウェアによりコヒーレンシ制 御を行うことができれば、コスト及び電力消費を抑えつつ効率的な並列処理を実 現できると期待されている、特にハードウェアコストや消費電力およびリアルタ イム制約に厳しい組込み系マルチコアでは,4コアの富士通FR1000[SKK+05],8 コアの東芝 Venezia[NTF+08] 等において, すでにノンコヒーレントキャッシュアー キテクチャが採用されている.また,ルネサステクノロジ/日立製作所/早稲田 大学の RP2[IHY+08] は8コア集積しているが,ハードウェアではチップ価格を 抑えるためにコヒーレンシ機構は4コアまで対応とし,5コア以上のコア数では ノンコヒーレントキャッシュとして利用する設計となっている.高性能計算分野 においても,イリノイ大の Rigel[KJJ+09], Intel の Single-Chip Cloud Computer  $(SCC)[HDH^+10]$  は , それぞれのコアがキャッシュを持つが , チップ全体でのコヒー レンシ制御はソフトウェアにより行うことが想定されている.ソフトウェアによ リコヒーレンシ制御を行う手法としては OS や Runtime によるアプローチとコン パイラやプログラミングモデルによるアプローチがある [CSG99] . OS や Runtime によりソフトウェアによりコヒーレントな仮想共有メモリ空間を実現する Shared Virtual Memory[LH89] や Treadmarks[ACD+96] が提案されている.これらの手法 は一般的なプロセッサハードウェアで実現可能であり SMP 向けのソフトウェアが そのまま動作するが,コヒーレンシ維持のオーバーヘッドが大きい.Rigel[KJJ+09] ではBulk Synchronous モデルを元にしたタスクベースのプログラミングモデルを 提案し、そのタスクモデルを前提としたソフトウェアコヒーレンシ制御を提案し

ている [KJL+09]. しかしながら, Rigel ではバリア同期ごとのインターバル内でのコア間通信はサポートしておらず,また false sharing の対処には,ワードごとの dirty bit を持つ特別なハードウェアを想定しているため,この手法を汎用のマルチコアハードウェアでそのまま適用することはできない. 本研究では,一般的なキャッシュハードウェアにおいて実現可能な,コンパイラによるソフトウェアコヒーレンシ制御手法を提案し,ハードウェアによるコヒーレンシ制御と同等以上の性能が自動で得られることを示す.その際に,コンパイラの手法と併せて,コード生成の際に利用可能な並列処理 API を併せて提案することで,様々なマルチコアプロセッサ上でソフトウェアコヒーレンシ制御を実現する.

以上のような背景を踏まえて、本論文では以下を研究の目的とする、

- Cプログラムの自動並列化のためのポインタ解析の精度向上を提案し、頻出するプログラム記述のパターンについてポインタ解析による所望の解析精度を効率的に実現し、自動並列化による性能向上が得られることを示す。

- C プログラムの自動並列化のためのプログラム記述法を提案し,実際にプログラムの書き換えを行い,自動並列化コンパイラを利用することで,様々なマルチコアプロセッサ上で自動並列化による性能向上が得られることを示す.

- 実行時の負荷不均衡が存在する場合やリアルタイム処理時にも適用可能な、コンパイラによる低消費電力化制御手法を提案し、マルチコアプロセッサ向けの並列処理 API を提案して利用することで、実際にマルチコアプロセッサ上での消費電力が削減されることを示す。

- 一般的なキャッシュハードウェアを用いて自動で高性能が実現できるコンパイラによるソフトウェアコヒーレンシ制御手法を提案し、マルチコアプロセッサ向けの並列処理 API を提案して利用することで、実際にマルチコアプロセッサ上でソフトウェアコヒーレンシ制御により高い並列処理性能が得られ

ることを示す.

### 1.2 本論文の構成

本論文の構成は以下の通りである.

第2章「OSCAR 自動並列化コンパイラ」では,本研究で開発したOSCAR 自動 並列化コンパイラの機能と構成ならびにコンパイラの解析や最適化の処理フロー について述べる,OSCAR コンパイラは逐次 C または Fortran プログラムを入力 して並列処理用の指示文を含む並列 C または Fortran プログラムを自動生成する. OSCAR コンパイラは複数レベルの並列性を利用したマルチグレイン自動並列化を 行い,プログラムの階層(関数やループネスト等)ごとに並列性の抽出を行い,そ れぞれの階層の持つ並列性に応じて、ベーシックブロック、ループ、サブルーチン 等の粗粒度タスクをプロセッサにスケジューリングしていく.さらに,プロセッサ 近傍のキャッシュやローカルメモリを有効利用するためのデータローカリティ最適 化を適用する.並列コード生成にはOpenMPの持つ4つの指示文に加えて,電力 制御,メモリ配置,データ転送,グループバリア同期,時間管理をサポートする OSCAR API の指示文を利用する.この OSCAR コンパイラにより自動生成され た OpenMP および OSCAR API を含む並列プログラムを各マルチコア向けのコー ド生成コンパイラを用いてさらにコンパイルすることで実行バイナリを生成する. これにより、様々なマルチコアアーキテクチャ上で自動並列化および低消費電力化 を実現できる.本論文で提案するプログラムの解析や最適化手法は,このOSCAR コンパイラに実装されている.

第3章「ポインタ解析」では,Cプログラムを自動並列化する際に必要となるポインタ解析の解析精度向上について提案する.並列処理が求められるアプリケーションプログラムで頻出するデータ構造として,ポインタのポインタにより実現さ

れる擬似的な多次元配列があるが,従来のポインタ解析では解析できず自動並列化ができなかった.このようなデータ構造を解析して自動並列化を適用するために,ポインタの配列の各要素が指しているメモリ領域のエイリアス関係を解析するElement-Sensitive ポインタ解析を新たに提案する.この Element-Sensitive ポインタ解析に、従来のポインタ解析アルゴリズムの解析情報に 1 ビットのデータ構造を追加するだけの簡易な拡張であり,軽量な実装により頻出のデータ構造を用いたプログラムを自動並列化するのに必要な解析精度を得ることができる.従来のポインタ解析では自動並列化が不可能であった SPEC2000 equake および第4章で述べるParallelizable Cへの修正を行った SPEC2006 hmmer について,Element-Sensitiveポインタ解析を利用することで自動並列化が可能となった.自動並列化結果について8コア搭載の IBM p5 550Q サーバにおいて性能評価を行ったところ,8コア使用時に逐次実行時と比べてそれぞれ equake で 4.96 倍および hmmer で 6.06 倍の性能向上が得られた.

第4章「Parallelizable C」では、コンパイラによる自動並列化が可能なプログラム記述法として Parallelizable Cを提案する.コンパイラの解析精度,特にポインタ解析精度を考慮して、ポインタ演算やポインタのキャストを制限するようなプログラム記述のガイドラインを設定することで、Cプログラム自動並列化支援の枠組みを構築する.実際にこのガイドラインに沿ってプログラムの書き換えを行ったところ、市販コンパイラでは全く並列化できなかった SPEC2000 art, equake は書き換えが不要であり、SPEC2006 lbm で 1.8%、hmmer で 0.03%の書き換えにより自動並列化可能となった.Parallelizable C で記述した6つの逐次プログラムに対して OSCAR コンパイラによる自動並列化を適用し、マルチコアシステム上での処理性能の評価を行った.その結果、逐次実行時と比較して、2 コア集積のマルチコアである IBM Power5+を4基搭載した8コア構成のサーバである IBM p5550Q において平均 5.54 倍、4 コア集積のマルチコアである Intel Core i7 920 プ

ロセッサを搭載した PC において平均 2.43 倍 , SH-4A コアベースの情報家電用マルチコア RP2 の 4 コアを使用した SMP 実行モードにおいて平均 2.78 倍の性能向上が得られた .

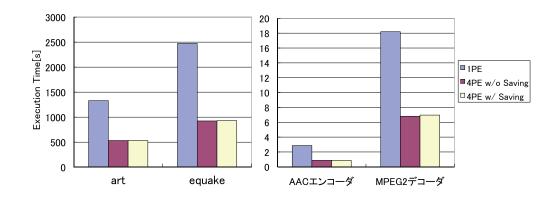

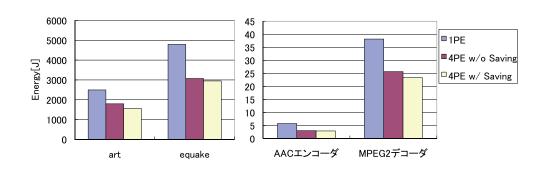

第5章「低消費電力化制御」では,現在のプロセッサで問題となっている消費電力削減のために,最速実行時とリアルタイム実行時におけるコンパイラによる低消費電力化手法を提案する.併せて,各社のマルチコア上で低消費電力化を利用するためのOSCAR APIの提案を行い,自動並列化コンパイラで逐次プログラムからOSCAR APIで記述された並列プログラムを自動生成することで,各社マルチコア上でコンパイラによる自動並列化と低消費電力化が利用可能となった.NEDO "リアルタイム情報家電用マルチコア "プロジェクトにおいて,新たに開発した8コア集積の情報家電用マルチコア RP2 において,マルチコアにおけるコンパイラによる消費電力制御を世界で初めて実現し,4 コアを用いた場合の最速実行モードにおいて消費エネルギーが SPEC2000 の art で 13.06%,equake で 3.99%,メディア処理の AAC エンコーダで 3.84%,MPEG2 デコーダで 9.01%削減された.また,8 コアを用いた場合のリアルタイム制約モードにおいて,平均電力が AAC エンコーダで 87.9%,MPEG2 デコーダで 76.0%削減された.

第6章「ソフトウェアコヒーレンシ制御」では、今後のメニーコアプロセッサにおける重要技術となる、コンパイラによるソフトウェアコヒーレンシ制御手法を提案する。コンパイラによる自動並列化と併せて、OSCAR API を用いてキャッシュライトバック、キャッシュセルフインバリデート、および変数配置のアラインメントを指示することで、ソフトウェアによる自動コヒーレンシ制御を実現した、科学技術計算およびメディア処理の4つのアプリケーションプログラムを用いて、上述のRP2において4コア使用時の自動並列化性能の評価を行ったところ、ハードウェアコヒーレンシ制御で1コアの逐次実行と比較して平均3.03倍、提案するソフトウェアコヒーレンシ制御においても同様の平均3.13倍の性能向上が得られ

た.さらに,ハードウェアではコヒーレンシ制御できない8コア使用時に平均4.88 倍の性能向上が得られた.

最後に,第7章「結論」では,本研究により得られた成果と今後の課題について述べる.

# 第2章 OSCAR自動並列化コンパイラ

### 2.1 はじめに

マルチコアプロセッサを含む,マルチプロセッサシステムを用いて高性能・低消費電力を実現するためには,ループレベルの並列性のみならずプログラム中の複数レベルの並列性を利用した並列処理,キャッシュやローカルメモリを有効活用するためのデータローカリティ最適化,および低消費電力化のための周波数・電圧制御やクロック・電源制御が必要となり,並列化を含む高度な最適化技術を駆使したソフトウェア開発が必須となる.しかしながら,並列処理の高度な専門知識を用いたプログラミングは,一般のアプリケーションプログラム開発者には難易度が高く,長期間の並列チューニングを要する.

並列プログラミングを行う場合には、共有メモリ向けの pthread や OpenMP 、分散メモリ向けの MPI 等のように、ユーザプログラマが明示的に並列処理箇所やデータの割り当て、プロセッサ間の通信を記述するものが主流である.このような明示的な並列処理の指定はデッドロックやレースコンディション等の並列バグを誘発しやすく、正しい並列プログラムを記述するのを困難にしている.さらに、並列処理による性能向上を得るためには、並列処理オーバーヘッドやデータローカリティを考慮する必要があり、一般のアプリケーションプログラマには難易度が高いものとなっている.また、所望の性能を得るために、対象のコア数やアーキテクチャに特化した記述が必要となることが多く、プログラムの異なるアーキテクチャ間でのポータビリティが阻害されてしまっている.そのため、シングルプロセッサ用のプログラムから、コンパイラが自動的に並列性を抽出して、マルチプロセッサ上での効率的な並列処理を可能とする自動並列化コンパイラの利用が強く期待されている.

従来より、プログラム全域からの適切な粒度の並列性抽出、プロセッサ近傍の 高速キャッシュメモリあるいはローカルメモリの最適利用を実現するための自動並 列化コンパイラの研究・開発が行われてきた [Wol96, EHP98, HAA+96]. これらの 研究・開発の大部分はプログラム中のループ部分の並列化を対象としたものであり、現在までに様々なループ並列性解析手法やリストラクチャリング手法が開発されている。このようなループ並列化手法は商用コンパイラにも導入され、IBM XL コンパイラや、Intel コンパイラ等は自動並列化機能を備えている。

ループ並列化手法は大きな進歩を遂げたが,現在では既に成熟期に至り今後の 大幅な性能向上は見込めないと考えられている.そのため,マルチプロセッサシ ステムの更なる実効性能向上のためには,従来のループ並列性に加え,ループ間 やサブルーチン間といった粗粒度タスク並列性や,基本ブロック内での命令・ス テートメント間の近細粒度並列性などの複数レベルの並列性を利用することが必 須である.

早稲田大学で開発されている OSCAR コンパイラ [本多 90, KHM+92, 笠原 03] では、粗粒度タスク並列処理、ループレベル並列処理、近細粒度並列処理を組み合わせたマルチグレイン並列処理を実現している。さらに OSCAR コンパイラは抽出したマルチグレイン並列性に応じ、プログラムの各所毎に並列性に見合った適切な計算資源(プロセッサ)の割当てや粗粒度タスク間にまたがる広域的なキャッシュメモリ最適化を実現している。本研究では、この OSCAR コンパイラを利用して様々なマルチコアプロセッサにおける C プログラムの自動並列化および低消費電力化に関する研究・開発を行った。本章ではこの OSCAR コンパイラの概要について述べる。

本章の構成は以下の通りである.まず,第 2.2 節では OSCAR コンパイラが実現しているマルチグレイン並列処理について述べ,第 2.3 節では OSCAR コンパイラの構成と,OSCAR コンパイラが並列コード生成に利用している並列処理用 APIである OSCAR API について述べる.そして,第 2.4 節では関連研究について述べ,最後に第 2.5 節でまとめを述べる.

### 2.2 マルチグレイン並列処理

本節では、OSCAR コンパイラで実現されているマルチグレイン並列処理について述べる。マルチグレイン並列処理は粗粒度タスク並列性、ループ並列性、近細粒度並列性を組み合わせ、プログラム全域から並列性を抽出する技術である。本論文では、粗粒度タスク並列性とループ並列性を用いたマルチグレイン並列処理を行う。

#### 2.2.1 マクロタスク生成

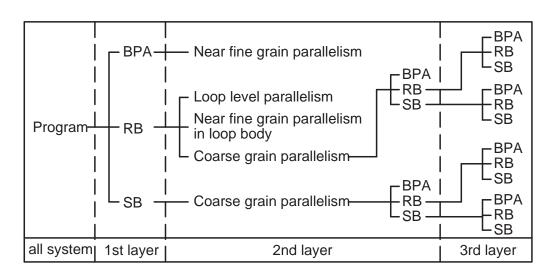

粗粒度タスク並列処理では、プログラムは基本ブロックまたはその融合ブロックで構成される疑似代入文ブロック BPA[笠原 03], DO ループや後方分岐により生じるナチュラルループで構成される繰り返しブロック RB[笠原 03], サブルーチンブロック SB[笠原 03] の3種類の粗粒度タスク(マクロタスク MT[笠原 03])に分割される、繰り返しブロック RB やサブルーチンブロック SB はその内部をさらにマクロタスクに分割し階層的なマクロタスク構造を生成する.

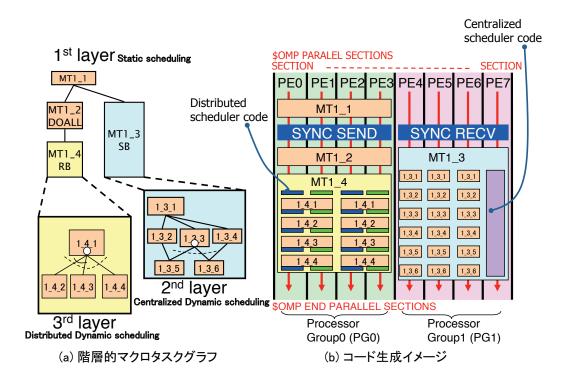

図 2.1 にマクロタスクの階層的定義の模式図を示す.まずプログラムのメインルーチン,すなわち第 1 階層を 3 種類のマクロタスクに分割し,マクロタスクの種類に応じて,第 2 階層,第 3 階層と階層的にマクロタスク分割する様子を示している.

#### 2.2.2 粗粒度タスク並列性抽出

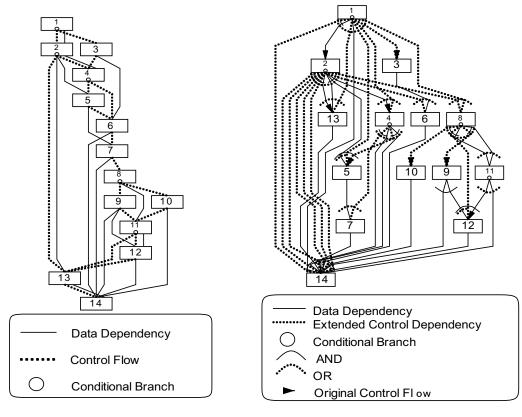

マクロタスク生成後,各階層においてマクロタスク間のデータ依存と制御フローを解析し,マクロタスク間のデータと制御のフローを表すマクロフローグラフ [本多 90, 笠原 03] を生成する.マクロフローグラフの例を図 2.2(a) に示す.マク

図 2.1: 階層的マクロタスク定義

ロフローグラフ中, ノードはマクロタスク, ノード中の番号はマクロタスク番号, ノード内の小円は条件分岐ノード, ノード間の実線はデータフロー, 点線は制御フローをそれぞれ表す. このマクロフローグラフは, マクロタスク間の制御フロー, データフローを表すだけであり, マクロタスク間の並列性を表してはいない.

次に,階層的に生成されたマクロフローグラフに対し最早実行可能条件解析 [本多 90, 笠原 03] を適用し,階層的なマクロタスクグラフ MTG[本多 90, 笠原 03] を生成する.最早実行可能条件とは,制御依存とデータ依存を考慮したマクロタスクの最も早く実行を開始してよい条件であり,マクロタスクグラフは粗粒度タスク並列性を表す.マクロタスクグラフの例を図 2.2(b) に示す.マクロタスクグラフでは,ノード,ノード中の番号,ノード中の小円はマクロフローグラフ同様マクロタスクと条件分岐を表しているが,ノード間の実線はデータ依存,点線は拡張された制御依存を表している.拡張された制御依存とは,通常の制御依存の他に,マクロタスクの非実行確定条件を含んでいることを表している.また,実線アーク(弧) は,アークが束ねるエッジが AND 関係にあり,点線アークは束ねるエッジが OR 関係にあることを表している.例えば,図 2.2(b) 中の MT6 の最早

(a) Macro Flow Graph (MFG)

(b) Macro Task Graph (MTG)

図 2.2: マクロフローグラフとマクロタスクグラフ

実行可能条件は「MT2がMT4に条件分岐することが決定するか,MT3の実行が終了」という条件になる.このマクロタスクグラフは,マクロタスク間の粗粒度タスク並列性を直接表現したグラフとなっている.

#### 2.2.3 データローカライゼーション

プロセッサとメモリの速度差の拡大によりキャッシュメモリやローカルメモリを 有効利用することがマルチプロセッサシステムの性能向上にとって重要となって いる.OSCAR コンパイラでは並列性とデータローカリティの両方を考慮したデー タローカライゼーション手法 [吉田 94, 石坂 02] により複数粗粒度タスク間でキャッシュあるいはローカルメモリ上のデータを効果的に用いる.

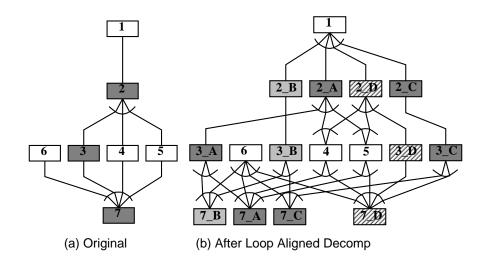

データローカライゼーション手法では,まず複数ループ間のデータ依存を解析し,データ依存する分割後の小ループ間におけるデータ授受がキャッシュあるいはローカルメモリを介して行われるようにそれらのループを整合して分割するループ整合分割[吉田94]を行う.分割されたループのうち同一データにアクセスする複数のマクロタスクは,データローカライザブルグループ(DLG)と呼ぶタスク集合にグループ化される.図 2.3 にループ整合分割を適用したマクロタスクグラフを示す.図中(b)の同じ網掛けで塗られたマクロタスクが DLG に属するマクロタスクである.

整合分割後の粗粒度タスクスケジューリングでは、粗粒度タスク間の並列性を考慮しながら、同一 DLG に属するマクロタスクが可能な限り同一プロセッサ上で連続的に実行されるようにスケジューリングを行う。このようにループ分割と DLG 内タスクの連続実行を組み合わせることにより、複数のループに渡り再利用することを可能とすることでメインメモリアクセスを削減し、タスク間のデータ授受をキャッシュあるいはローカルメモリを用いて高速に行うことが可能となる、

#### 2.2.4 プロセッサグループへのマクロタスク割り当て

粗粒度タスク並列処理では複数のプロセッサエレメント PE[小幡 03] をソフトウェア的にグループ化したプロセッサグループ PG[小幡 03] に割り当てる.割り当てられた MT 内で更に MTG が定義されている場合は,プログラム中の階層的MTG の並列性を有効に利用するため,内部 MTG の並列性に応じて PG 内の PE を階層的にグループ化する.

マクロタスクグラフがデータ依存のみから構成される場合はコンパイル時に静的にスケジューリングが行われ,各プロセッサグループの処理するマクロタスクが

図 2.3: データローカライゼーションにおけるループ整合分割

決定される.マクロタスクグラフが条件分岐等の実行時不確定性を含む場合は実行時にスケジューリングを行うダイナミックスケジューリングルーチンをコンパイラが自動生成し,実行時にマクロタスクを PG に割り当てる.ダイナミックスケジューリングには,1つのスケジューリング専用プロセッサを用いる集中型と,マクロタスクコードの実行とスケジューリングを全プロセッサが協調して行う分散型があり,実行するターゲットシステムのプロセッサ数やデータ通信オーバヘッド等の各パラメータに応じて適切な手法を選択する必要がある.各マクロタスクは階層的にスタティックスケジューリングあるいはダイナミックスケジューリングされる.生成されたスタティックスケジューリングコード及び実行時スケジューラはユーザコードであり,OS のシステムコールによるスケジューラに比べ極めて低オーバーヘッドなスケジューリングが可能である.

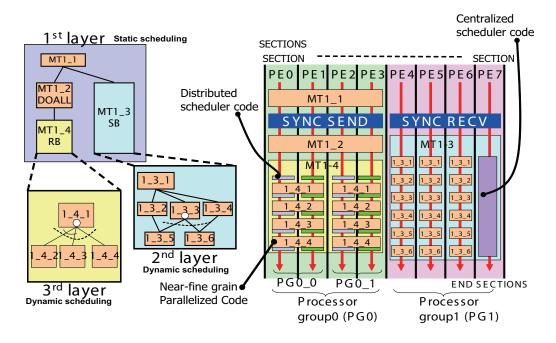

図 2.4 に階層的なコード生成のイメージ図を示す.まず,第 1 階層(図中 1st layer)では 8 つの PE を 4PE を持つ PG0,PG1 の 2PG にグループ化している.この階層はおいては条件分岐等の実行時不確定性を含まないため,スタティックスケジューリングされ, $MT1_-1$ , $MT1_-2$ , $MT1_-4$  は PG0 に, $MT1_-3$  は PG1 に割り当てられ

ている.スタティックスケジューリングを適用した場合,コンパイラは各 PE に対してスケジューリング結果に従い,異なるコードを生成する.

次に,サブルーチンブロックであるMT1\_3(SB)の内部に第2階層(図中2nd layer)が定義されており,MT1\_3\_3からMT1\_3\_5,MT1\_3\_6に対する条件分岐が存在するため,ダイナミックスケジューリングが行われ,この例ではMT1\_3を実行する4つのPEをそれぞれPGとし,集中スケジューリングを適用している.集中スケジューリングの場合,一つのPEがスケジューラとして働き,そのPEはマクロタスクの実行は行わず,その他のPEへのマクロタスクの割り当てのみを行う.したがって集中スケジューラとなるPE7用のコードにはスケジューリングルーチンが生成される.一方,スケジューラ以外のPEはマクロタスクの実行を担当するが,実行するマクロタスクは実行時にスケジューラによってきめられるため,各PEのセクションにはPE4からPE6に示すように,全ての第2階層のマクロタスクのコードが生成され,各PEは実行時にスケジューラの割り当て結果に従い,これらのマクロタスクを選択的に実行する.

一方、繰り返しブロックである MT1\_4(RB) の内部には第3階層 (図中3rd layer) が定義されており、この例では分散ダイナミックスケジューリングを適用している。また、この階層では MT1\_4 を実行する 4 つの PE を 2PE ずつにグループ化している。分散ダイナミックスケジューリングでは、各 PG がスケジューリングとマクロタスク実行の両方を行うので、各セクションには全マクロタスクのコードとスケジューリングルーチンの両方が生成される。各 PE はスケジューリングルーチンを実行し、自身が次に実行するマクロタスクを決定した後、そのマクロタスクを実行する。マクロタスクの実行終了後はマクロタスクコードの後に生成されたスケジューリングルーチンを実行し、次に実行するマクロタスクを決定する。

図 2.4: 階層的コード生成イメージ

# 2.3 OSCAR コンパイラの構成とOSCAR API

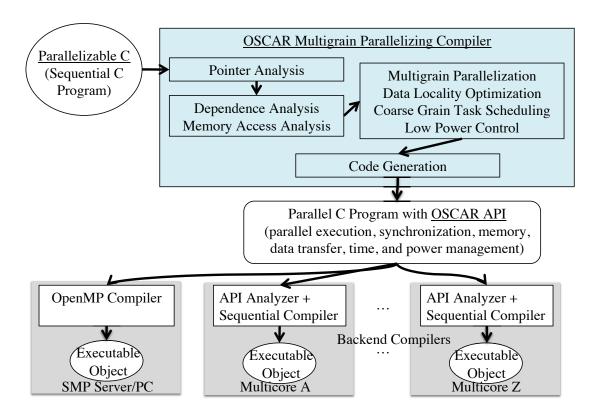

OSCAR コンパイラはソースコード変換により標準的な並列化指示文を含んだ Cまたは FORTRAN プログラムを生成することで,多様なプラットフォームに対するポータビリティを実現している.OSCAR コンパイラはこの並列化指示文として OSCAR API[OSC, KMM+09] を利用している.

OSCAR API は NEDO "リアルタイム情報家電用マルチコア技術" プロジェクトにおいて、早稲田大学、東芝、日本電気、パナソニック、日立製作所、富士通研究所、ルネサステクノロジによって開発された情報家電用マルチコア向け並列化 APIである。OSCAR 自動並列化コンパイラにより逐次プログラムから OSCAR APIを用いた並列プログラムを自動生成することが可能であり、既存の逐次コンパイラに API 解釈部を追加することにより、各社マルチコア上での並列処理が実現可能となる。OSCAR APIを用いることで、OSCAR コンパイラによる最適化を様々

なマルチコアで実現することができ,並列プログラムの大幅な生産性向上が期待できる.

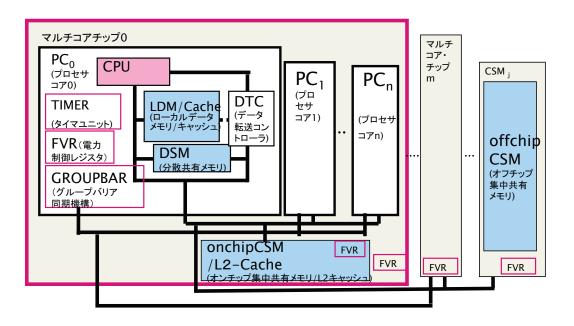

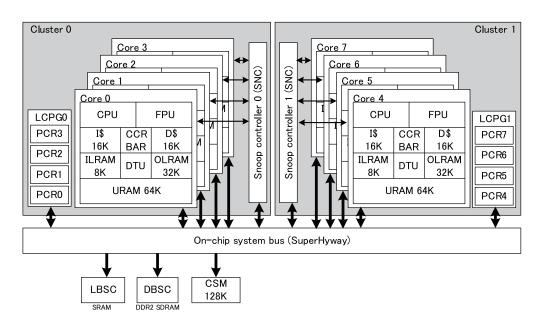

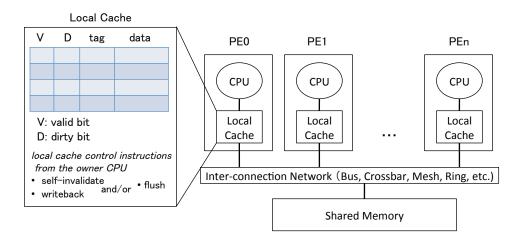

#### 2.3.1 OSCAR マルチコアアーキテクチャ

OSCAR API では標準的なアーキテクチャとして OSCAR マルチコアアーキテクチャを定めている。本節では OSCAR マルチコアアーキテクチャ[木村 01] の概要を述べる。

図 2.5 に示すように,OSCAR マルチコアアーキテクチャは複数のプロセッサコア (PE) および複数バスやクロスバ等の内部接続ネットワーク,オンチップおよびオフチップの集中共有メモリ (CSM) を持つ.各 PE は CPU コア,ローカルプログラムメモリ (LPM) または命令キャッシュ,ローカルデータメモリ (LDM) またはデータキャッシュ,分散共有メモリ (DSM),およびデータ転送コントローラ (DTC)を持つ.コンパイル時の情報に応じてこれらのメモリを適切に使い分けることにより,スタティック及びダイナミックスケジューリング時の両方において効率の良い並列処理を行うことを特徴とする.さらに,コンパイラによる低消費電力制御を実現するために,周波数・電圧制御レジスタ (FVR) が追加されている [白子 06].また,多くの実在するマルチコアプロセッサは OSCAR マルチコアのモデルで近似することができ,機能の有無やパラメタを変更することで,多様なマルチコアプロセッサへの対応が可能となる.

#### 2.3.2 OSCAR API 指示文

OSCAR API は C と FORTRAN に対応しており、共有メモリマルチプロセッサを対象とした OpenMP[ope05] のサブセットに、OSCAR マルチコアアーキテクチャ用の新たな指示文を追加したものとなっている.以下に指示文の構成を示す.

図 2.5: OSCAR マルチコアアーキテクチャ

#### OpenMP のサブセット

スレッド生成,同期,排他制御ディレクティブはOpenMP互換となっており, スレッド生成には "parallel sections",メモリアクセス順の保証には "flush", 排他制御には "critical"を用いる.これら3つがサポートされている環境で あれば,SMPモードにおけるマルチグレイン並列処理を簡単に実現できる.

#### 独自定義のディレクティブ

独自定義のディレクティブとしては , データのローカルメモリ配置 , DTC(DMAC) によるデータ転送 , 周波数・電圧・電源制御 , タイマ , 同期用の API が策定されている .

図 2.6: OSCAR コンパイラを用いたコンパイルフロー

#### 2.3.3 OSCAR APIを用いたコンパイルフロー

OSCAR 自動並列化コンパイラおよび並列化 API を用いたプログラムのコンパイルの流れを図 2.6 に示す.まず, C言語等で記述された逐次型アプリケーションプログラムを OSCAR 自動並列化コンパイラでコンパイルし, OSCAR API で記述された並列プログラムを生成する.次に,この並列化されたプログラムをコード生成コンパイラ(通常の 1 プロセッサ用のコンパイラに API 解釈部を加えたもの)でコンパイルしマシンコードを生成する.これにより OSCAR コンパイラを用いて異なる企業のマルチコアプロセッサ用の並列コードを自動生成することが可能となる.

# 2.4 関連研究

プログラム全域からの適切な粒度の並列性抽出,プロセッサ近傍の高速キャッシュメモリあるいはローカルメモリの最適利用を実現するための自動並列化コンパイラの研究・開発が行われてきた.

イリノイ大学の Polaris コンパイラ [EHP98] ではシンボリック解析, Array Privatization, 実行時データ依存解析, レンジテスト, インタープロシージャ解析といった強力な依存解析手法を用いたループ並列化を実現している. またスタンフォード大学の SUIF コンパイラ [HAA+96] では unimodular transformation や affine partitioning [WL91, LCL99] といった種々のループリストラクチャリングを内包した並列化手法を用いることでループレベルの並列性解析とデータローカリティ最適化を総合的に行っている. これらのコンパイラの研究により, ループ並列化技術は飛躍的に進化を遂げたが, ループ並列処理はすでに成熟期となっており, さらなる性能向上のためにはループ並列性のみならずタスク並列性やステートメントレベルの並列性の併用が必要不可欠と考えられる.

マルチレベルの並列性を利用するコンパイラにはNANOSコンパイラ [GMO+00], PROMISコンパイラ [SSP99], そしてOSCARコンパイラ [本多 90, KHM+92, 笠原 03]が挙げられる.カタルーニャ大学のNANOSコンパイラでは,拡張したOpenMPAPIによって粗粒度タスク並列性を含むマルチレベル並列性を抽出しようとしている.またPROMISコンパイラはフロントエンドとバックエンドで共通の中間表現を用いてループ並列性と命令レベル並列性を統合しようとしている.それに対して,早稲田大学で開発されているOSCARコンパイラでは,粗粒度タスク並列処理,ループレベル並列処理,近細粒度並列処理を組み合わせたマルチグレイン並列処理を実現している.

### 2.5 まとめ

本章では本研究で開発した OSCAR 自動並列化コンパイラの機能と構成ならび にコンパイラの解析や最適化の処理フローについて述べた .

OSCAR コンパイラは逐次でまたはFortranプログラムを入力して並列処理用の指示文を含む並列でまたはFortranプログラムを自動生成する。OSCAR コンパイラは複数レベルの並列性を利用したマルチグレイン自動並列化を行い、プログラムの階層(関数やループネスト等)ごとに並列性の抽出を行い、それぞれの階層の持つ並列性に応じて、ベーシックブロック、ループ、サブルーチン等の粗粒度タスクをプロセッサにスケジューリングしていく。さらに、プロセッサ近傍のキャッシュやローカルメモリを有効利用するためのデータローカリティ最適化を適用する。並列コード生成にはOpenMPの持つ4つの指示文に加えて、電力制御、メモリ配置、データ転送、グループバリア同期、時間管理をサポートするOSCAR APIの指示文を利用する。このOSCAR コンパイラにより自動生成されたOpenMPおよびOSCAR APIを含む並列プログラムを各マルチコア向けのコード生成コンパイラを用いてさらにコンパイルすることで実行バイナリを生成する。これにより、様々なマルチコアアーキテクチャ上で自動並列化および低消費電力化を実現できる。

OSCAR コンパイラを利用することにより,既存の並列処理手法を様々なマルチコアプロセッサにおいて実現しつつ,さらに新たな手法の研究・開発が可能となる.本論文の以下の章で提案するプログラムの解析や最適化手法は,このOSCARコンパイラに実装されている.

# 3.1 はじめに

組込み機器から PC , スーパーコンピュータに至るあらゆる情報機器において , マルチコアプロセッサが主流となってきており , 並列ソフトウェア開発の生産性 向上のため自動並列化コンパイラの実用化が期待されている . 従来より科学技術 計算分野の FORTRAN プログラムに対しては , Polaris[EHP98] , SUIF[HAA+96] , OSCAR[笠原 03] といった高性能な自動並列化コンパイラが開発され , 多くの並列 マシン上でその有効性が確認されてきた . より広く利用されている C 言語におい ても自動並列化コンパイラの利用が望まれているが , C 言語ではポインタを多用した自由な記述が可能であり , コンパイラがこれらのポインタの指し先を一意に解析できない場合 , 依存解析の精度が劣化し自動並列化の阻害要因となってしまう .

現状では多くの研究用あるいは商用の自動並列化コンパイラにおいて,Cプログラムに対する効果的な自動並列化や自動ベクトル化を期待する場合は,全てのポインタに対する restrict 修飾 [C9999] や,ポインタエイリアスの扱いに関する独自のコンパイラオプションを利用することが推奨されており,事実上全くポインタを使用しないプログラムを記述する必要がある.しかしながら,コンパイラによるポインタ解析の精度を高めることにより,プログラム記述に対する制約条件が緩和され,高度なコンパイラ最適化技術の利用によるマルチコア,メニーコア向けのソフトウェア生産性の向上が可能と考えられる.

ポインタ解析に関しては多くの研究 [Hin01] が行われているが, C 言語のあらゆる記述に対してポインタの指し先を静的に特定するのは事実上不可能となっている. そのため, 科学技術計算やメディア処理アプリケーションのアルゴリズムは潜在的に高い並列性を持っていながら, 従来のポインタ解析技術では並列性の自動抽出にはしばしば不十分なことがある.

そのような例の一つに,アルゴリズム上は多次元配列として扱うことが可能な データ構造を,ポインタへのポインタとメモリ動的確保を行うループの記述によ

```

/* 多次元配列のようなデータ構造を確保 */

BB1:

a = (int **)malloc(n * sizeof(int *))

LOOP2:

for (i = 0; i < n; i++) {

a[i] = (int **)malloc(m * sizeof(int *));

}

/* 確保したデータ構造に計算結果を代入 */

LOOP3:

for (i = 0; i < n; i++) {

LOOP3_1:

for (j = 0; j < m; j++) {

a[i][j] = i + j;

}

}

```

図 3.1: 従来のポインタ解析では識別できないプログラム例

り実装する場合がある.多次元配列と同様の機能を実現する際に,C言語では図 3.1 のように malloc によって各次元に相当する領域を確保し,ポインタの参照によってアクセスすることがある.図 3.1 の例では,添え字とメモリアドレスが 1 対 1 の関係になっており,i および j を変数としたとき a[i][j] は必ず一意なメモリアドレスへの参照となっている.一般に,アルゴリズム上は多次元配列となっていても,各次元の要素数が入力によって決定される場合には,C言語ではこのようなデータ構造が静的な配列の代替として利用されることが多い.

この例では,LOOP3の外側ループにおいてイタレーションごとの並列処理が可能である.しかし,このようなポインタへのポインタとヒープで確保されたデータ構造に対して従来のポインタ解析の適用を考えた場合,多くのポインタ解析では配列の個々の要素の指し先を独立には解析しないため,ポインタ配列の各要素の指し先情報は配列全体で単一の情報に縮退される.そのため,図3.1におけるLOOP3の外側ループでは,a[i]の示す各要素の間のエイリアスの関係が不明とな

ることから,ループイタレーション間の依存解析ができず,自動並列化が阻害されてしまう.

そこで本章では、ポインタの配列において各要素の指し先のエイリアス関係を 識別可能な Element-Sensitive ポインタ解析を提案する、ポインタ配列の各要素に 指し示されるオブジェクトに重なりが無い場合は、このようなデータ構造に対す るアクセスを含むループに対し、依存距離と依存ベクトルによるイタレーション 間依存解析が適用可能となり、並列性の抽出が可能となる。

提案する Element-Sensitive ポインタ解析では,既存のポインタ解析手法に対して簡単な追加情報を加えるだけで,自動並列化に有用なポインタ解析精度を得ることができる. Element-Sensitive ポインタ解析の利点としては,(1)既存の逐次プログラムが自動並列化可能となることによる速度向上,(2)既存の逐次プログラムを書き換えることで自動並列化による速度向上を得ようとした場合のコード書き換え量の削減,(3)ループリストラクチャリング等のプログラム最適化過程におけるポインタ指し先情報の表現として利用,そして(4)解析アルゴリズムがシンプルであり軽量で効率的な実装が可能,といったことが挙げられる.

本章の構成を以下に示す.従来のポインタ解析に関する研究成果を利用し,Flow-Sensitive[EGH94, WL95, Kah08, HL09], Context-Sensitive[EGH94, WL95, WL04, NKH04, LLA07, Kah08, HL09], Heap-Sensitive[NKH04, LLA07], Field-Sensitive[PKH04, LLA07] ポインタ解析を基準となるポインタ解析精度として採用し,さらにこれらに加えて,従来あまり議論されていなかった Cycle-Sensitivity[RRH08], Element-Sensitivity について焦点を当てる.まず第3.2節では基準となる既存のポインタ解析手法について述べ,第3.3節では新たに提案する Element-Sensitive ポインタ解析について述べる.次に第3.4節では Element-Sensitive ポインタ解析と Cycle-Sensitive ポインタ解析の併用について述べ,第3.5節でポインタ解析結果の自動並列化への利用方法について述べる.そして,第3.6節では Element-Sensitive ポ

インタ解析を利用して自動並列化を適用した際のマルチコアシステム上での処理 性能およびさらなるポインタ解析精度向上の可能性について述べる.最後に,第 3.7節で関連研究について述べ,第3.8節でまとめを述べる.

# 3.2 基準となるポインタ解析

ポインタ解析とは、プログラム中に現れるポインタ変数がメモリ上のどの領域を指すかを解析するものである。データ依存の解析、データフロー解析、データアクセス範囲解析等の並列性抽出のためのプログラム解析 [Wol96] の精度はポインタ解析の精度に大きく依存する。そのため、ポインタ解析ではポインタの指し先を一意に決定できることが望まれる。ポインタ解析はプログラムの内部状態や指し示される領域に関する情報の持たせ方によって分類され、解析精度と解析コストのトレードオフが問題となる [Hin01]。

本節では,本章において基準となるポインタ解析精度として採用した,Flow-Sensitive, Context-Sensitive, Heap-Sensitive, Field-Sensitive ポインタ解析について述べる.

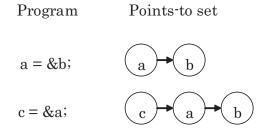

#### 3.2.1 Points-to解析

ポインタ解析では,メモリ上のあるポインタオブジェクトとそのポインタが指し示す可能性があるオブジェクトを解析するものが主流であり,Points-to 解析とも呼ばれる.この Points-to 解析で対象とするオブジェクトは,プログラム中で宣言されるスカラ変数や配列変数あるいはヒープ上の領域等を示し,しばしば複数のメモリ位置を一つの名前に抽象化して扱うため,抽象化されたメモリ位置(abstract memory location)とも呼ばれる.Points-to 解析のイメージを図 3.2 に示す.図中では,ポインタの指し先関係を  $\rightarrow$  を用いて表し, $(a \rightarrow b)$  はポインタオブジェク

図 3.2: プログラムと Points-to 集合の例

トaがオブジェクトbを指す可能性があることを示している.このようなポインタの指し先関係の集合を Points-to 集合と呼び,Points-to 解析は Points-to 集合を解析する.Points-to 集合におけるポインタの指し先情報は,各オブジェクトをノード,指し元オブジェクトから指し先オブジェクトへの関係をエッジで表現した有向グラフ (Points-to グラフ) として扱うことができる.

#### 3.2.2 Flow-Sensitive ポインタ解析

Flow-Sensitive ポインタ解析はプログラムのコントロールフローを考慮して,プログラムの各地点ごと,一般的にはステートメントごとに個別の解析情報を生成する. Flow-Insensitive 解析ではステートメントの順序を考慮せず,サブルーチンやプログラム全体で有効である単一の解析情報を生成するため, Flow-Sensitive よりも保守的な解析結果となる.

一般的に,Flow-Sensitive ポインタ解析は,データフロー解析 [ALSU07] の枠組みを用いて実装される.すなわち,対象となる束 (lattice) L,束の交わり (meet) 演算子  $\land$ ,伝達関数 (transfer function) F で定義される.ポインタ解析においては,束 L は Points-to 集合,交わり演算子  $\land$  は和集合  $\cup$  となり,伝達関数は各ステートメントにおける入力から出力に対する Points-to 集合の変化を計算する.また,ポインタ解析はコントロールフローグラフに沿って,順方向に行われる.

コントロールフローグラフにおける各ノードをkとすると,各ノードは入力する ポインタ解析情報  $IN_k$  と出力するポインタ解析情報  $OUT_k$  の二つの Points-to 集合 を保持する.それぞれのノードにおいて, $IN_k$ から伝達関数 $F_k$ を用いて $OUT_k$ を 計算する.このときのノードkにおけるデータフロー方程式は以下のようになる.

$$IN_k = \bigwedge_{x \in pred(k)} OUT_x$$

(3.1)

$OUT_k = F_k(IN_k)$  (3.2)

$$x \in pred(k)$$

$$OUT_k = F_k(IN_k) (3.2)$$

このときの伝達関数  $F_k$  は,以下の通りである.

$$F_k = gen_k \wedge (IN_k - kill_k) \tag{3.3}$$

ここで,  $gen_k$  にはそのステートメントによって新たに生成される Points-to 集合が 登録される.また, $kill_k$  は更新されるポインタに対して強い更新  $(strong\ update)$ を行うか,弱い更新(weak update)を行うかによって内容が異なる.新たに生成さ れる Points-to 集合において, あるポインタの指し元オブジェクト v が確実に更新 され,vが単一のポインタに対応することが決定できる場合は,強い更新が行われ る. すなわちvの更新前の指し先情報がkill集合に登録されて,その結果データ フロー方程式により除去されることになる.一方,ポインタの指し元オブジェク トvが確実に更新されるとは限らない,あるいはvが単一のポインタに対応する ことが決定できない場合は,弱い更新が行われる.すなわち kill 集合を空集合と することでそれまでのポインタ指し先情報は全て保持される.

本章のポインタ解析は Emami らの Flow-Sensitive , Context-Sensitive ポインタ 解析のアルゴリズム [EGH94] をベースとして実装している. Flow-Sensitive ポイ ンタ解析は解析コストが大きいことが問題となっていたが、近年は現実的な時間 で解析可能なアルゴリズムが提案されてきている [Kah08, HL09].

## 3.2.3 Context-Sensitive ポインタ解析

Context-Sensitive ポインタ解析では関数呼び出しの関数のコールパスごとに個別に解析情報を生成することで,解析精度を高めている.Context-Insensitive ポインタ解析では,コールパスを区別せず,ポインタの引数間のエイリアスの関係が異なる場合は,それらの情報が縮退され,保守的な解析結果となってしまう.

Emami らの Flow-Sensitive 、Context-Sensitive アルゴリズム [EGH94] では、引数におけるポインタ解析情報の関係に応じてサブルーチンをクローニングすることで Context-Sensitive 解析を実現している.関数呼び出しにおいてポインタを引数として渡す場合、呼び出された関数では引数のポインタを介して、スコープ外の変数にアクセスすることがある.そのような場合は、スコープ外の変数を不可視変数 (invisible variable) として定義し、解析情報を表現する.インタープロシージャ解析では、Mapping によって呼び元の関数の変数を呼び出される関数の不可視変数に対応付けを行い、呼び元における解析情報から呼び先における解析情報を合成する.そして、呼び先の関数の解析後に Unmapping を行う.すなわち、呼び先の関数における解析情報から呼び元における解析情報を合成する.

# 3.2.4 Heap-Sensitive ポインタ解析

ヒープ領域の抽象化についてもこれまでに多くの議論が行われてきたが,多くのポインタ解析では,メモリ動的確保を行うステートメントごとに別のオブジェクトとしている [Kah08, HL09].しかし,メモリ確保用のラッパ関数を用意していた場合,同じデータ型のオブジェクトを確保すると,それらが全て同一のオブジェクトとして縮退してしまい,解析の精度が低下する.

これを解決するために,ヒープを確保した際にメモリ動的確保が行われたコールパスごとに別名のオブジェクトとする手法があり,これらはHeap-Sensitive,あ

るいは Heap-Cloning と呼ばれる [NKH04, LLA07].

本章ではこの Heap-Sensitive ポインタ解析を採用している.この Heap-Sensitive 解析はインタープロシージャ解析時に,呼び出された関数の解析情報を呼び出し元の関数に Unmapping する際に,その都度,別名のオブジェクトとして扱うことで実現できる.

#### 3.2.5 Field-Sensitive ポインタ解析

Field-Sensitive ポインタ解析 [PKH04] では構造体の各メンバを区別して,それぞれ別のオブジェクトとして解析を行う. Field-Insensitive ポインタ解析では,構造体全体を単一のオブジェクトとして扱い,各メンバの指し先情報が縮退される.構造体をプログラムの主要なデータ構造として利用している場合は,高い解析精度を得るために Field-Sensitive 解析が重要となるため,本章では Field-Sensitive ポインタ解析を採用している.

# 3.3 Element-Sensitive ポインタ解析

本節では、新たに提案する Element-Sensitive ポインタ解析について述べる.多くのポインタ解析では、ポインタの配列に対して各要素の指し先を区別せず、各要素が指す可能性がある全ての領域を、単一の指し先情報に縮退して表現していた.しかし、これでは図 3.1 で示すようなポインタへのポインタとメモリ動的確保を用いたようなデータ構造において十分な解析精度が得られず、自動並列化の阻害要因となってしまう.このような例では、ポインタの配列において各要素ごとのポインタの指し先を識別することが必要となる.

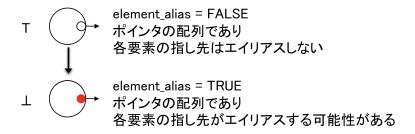

そこで,本節では既存のポインタ解析の各オブジェクトに対して *element alias* 属性という真偽値型の変数を追加するだけで効率的に Element-Sensitive 解析を実現

図 3.3: element alias 属性の束 (lattice)

する方法を述べる.この Element-Sensitive ポインタ解析のデータ構造およびデータフロー解析におけるアルゴリズムを示す.

#### 3.3.1 element alias 属性

本章で提案する Element-Sensitive ポインタ解析は,ポインタの配列における任意の 2 要素が指し示すオブジェクトのエイリアスの有無を, $element\ alias$  属性を持たせることで区別する.図 3.3 のイメージ図のように, $element\ alias$  属性は真偽値型の変数であり,各要素の指し先にエイリアスがある場合は真,無い場合は偽の値を保持する.このポインタ型の配列オブジェクトに追加される  $element\ alias$  属性がデータフロー解析の枠組みにより解析される.その際, $element\ alias$  属性の束 (lattice) は, $\top$  が偽 (FALSE), $\bot$  が真 (TRUE) となり,各オブジェクトの  $element\ alias$  属性は偽の値で初期化され,後述の伝達関数により解析が行われる.

#### 3.3.2 伝達関数

Element-Sensitive ポインタ解析の伝達関数では, $element\ alias$  属性を計算するために,従来の Flow-Sensitive ポインタ解析における  $gen\ o$ 計算に若干の変更を行う.従来の  $gen\ o$ 計算を  $gen_{fs}$  とすると,Element-Sensitive 解析における  $gen_{es}$

は以下のようになる.

$$gen_{es} = calc\_element\_alias(gen_{fs}, IN)$$

(3.4)

すなわち, $gen_{fs}$  と IN を入力として, $element\ alias$  属性の計算  $calc\_element\_alias$  を行う.データフロー解析において, $element\ alias$  属性を計算するためのアルゴリズム  $calc\_element\_alias$  を図 3.4 に示す.

element alias 属性の計算を行う関数 calc\_element\_alias は , 各ステートメントにお ける既存の Flow-Sensitive ポインタ解析の Points-to 集合 gen と Points-to 集合 IN を入力とし,  $element\ alias$ 属性を更新されたPoints-to集合genを返り値として返す.  $calc\_element\_alias$  では , gen に含まれるポインタの指し先関係  $(lh\_ptr \rightarrow rh\_object)$ における,各ポインタの指し元オブジェクト $lh\_ptr$ について, $lh\_ptr$ がポインタの配 列である場合に  $lh\_ptr$  の element alias 属性を計算する  $.lh\_ptr$  がポインタの配列で ある場合、更新されるポインタ要素が一意とはならないため強い更新が行われるこ とはなく , kill 集合は必ず空集合となる . すなわち , 伝達関数による処理後の  $lh\_ptr$ の指し先は , ステートメントの IN に含まれる  $lh\_ptr$  の指し先の集合  $rh\_objects\_IN$ と,gen 集合で生成された  $lh\_ptr$  の指し先の集合  $rh\_objects\_gen$  の和集合となる. ここで,  $lh_-ptr$  のそれまでの指し先のオブジェクトの集合  $rh_-objects_-IN$  と, 新た なポインタの指し先として登録されるオブジェクトの集合  $rh\_objects\_gen$  に重な りがある場合は,ポインタの配列の各要素の指し先がエイリアスする可能性がある ため,gen における lh\_ptr の element alias 属性を真とする.一方,rh\_objects\_gen と $rh\_objects\_IN$ に重なりがない場合は,この更新によってポインタの配列オブ ジェクト  $lh\_ptr$  の各要素の指し先にエイリアスが発生する可能性は無いため , genにおける lh\_ptr の element alias 属性は偽のままとなる.

```

function calc_element_alias (Points_to_set gen, Points_to_set IN)

return : Points_to_set

begin

for each lh\_ptr \in \{lh\_ptr \mid \exists rh\_object (lh\_ptr \rightarrow rh\_object) \in gen\}

if lh\_ptr is array of pointer then

rh\_objects\_IN = \{rh\_object \mid (lh\_ptr \rightarrow rh\_object) \in IN\};

rh\_objects\_gen = \{rh\_object \mid (lh\_ptr \rightarrow rh\_object) \in gen\};

if rh\_objects\_IN \cap rh\_objects\_gen \neq \phi then

lh\_ptr.element\_alias = TRUE;

endif

endif

endfor

return gen;

```

図 3.4: gen における element alias 属性計算アルゴリズム

# 3.3.3 交わり (meet) 演算子∧

データフロー解析の交わり (meet) 演算子  $\wedge$  は, $element\ alias$  属性に関しては図 3.3 のように真偽値の 2 通りの値のみを取り得るため,あるオブジェクトについて全てのパスでその  $element\ alias$  属性が偽の場合は偽,一つでも真であれば真となる.

各ステートメントの gen の計算では,IN における Points-to 集合と element alias 属性を入力として element alias 属性を計算していたが,コントロールフローの交わり  $\wedge$  ではオブジェクトの指し先の関係は考慮せずに各オブジェクトの element alias 属性のみを入力として演算を行う.これは,実際にプログラムを実行する際には,交わり後のポインタオブジェクトが指し示すのはその先行パスのいずれかで指し示していた指し先となるためである.このとき,オブジェクトのエイリアス関係には指し先のオブジェクトの重複は影響しないため,各パスの Points-to 集合に重なりがあった場合でも,全ての先行パスの element alias 属性が偽であれば,

交わり後の element alias 属性は偽とすることができる.

#### 3.3.4 インタープロシージャ解析

インタープロシージャ解析では,複数のオブジェクトを単一の不可視変数に Mapping する場合に,element alias 属性の Mapping について考慮する必要がある.この場合,交わり (meet) 演算子 ^ と同様に,呼び出し元におけるそれぞれのオブジェクトの element alias 属性が 1 つでも真の場合は Mapping された不可視変数の element alias 属性は真,そうでなければ偽とする.

呼び先におけるオブジェクトから呼び元におけるオブジェクトへの Unmapping 時には,解析情報の合成は起こらないため,呼び先の情報から対応する呼び元におけるオブジェクトの element alias 属性を設定する.

# 3.3.5 Cycle-Sensitive 不使用時の Element-Sensitive ポインタ 解析の適用例

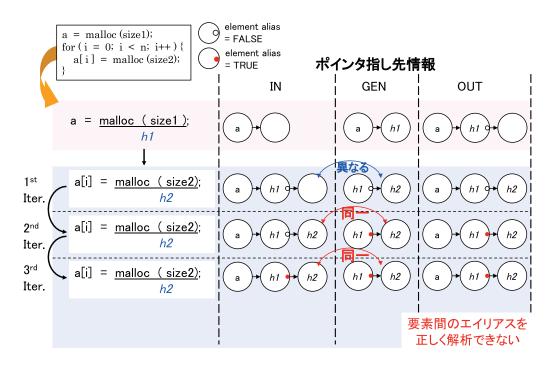

図 3.1 のコード例について、Cycle-Sensitive を使用せずに Element-Sensitive ポインタ解析のみを適用した場合の解析イメージを図 3.5 に示す.この例ではまずポインタへのポインタ a の指し先として、ポインタの配列オブジェクトがヒープ領域に確保され、ポインタ解析においては h1 という名前で識別される.次に、a[i] の各要素の指し先として、ループ中でそれぞれヒープ領域を確保しており、これらをまとめて一つのオブジェクトとして扱い、h2 という名前が付けられる.すなわち、プログラム実行時には a[i] の指し先は各イタレーションで確保されたそれぞれ独立した領域を指し示すことになるが、ポインタ解析におけるヒープの名前付けはプログラム中の静的なステートメントの場所によって行われるため、各イタレーションで確保されるヒープは全て h2 という名前に縮退されて表現される.

データフロー解析では,ループについては反復的に解析を行い,解析結果が収束するまで計算を続ける.この例ではまず 1 イタレーション目では「h1 が h2 を指す」という解析情報が gen として生成される.この時点では,IN は h1 は未初期化状態のため,このイタレーションでは h1 の指し先が IN と gen で重複することはなく,OUT は h1 が h2 を指し,h1 の element alias 属性は偽という情報となる.

次にデータフロー解析の2イタレーション目でも,h1 が h2 を指すという解析情報が gen として生成される.しかし,このときは既に IN において fh1 が h2 を指す」という情報が存在するため,IN と gen において h1 の指し先が重複する.そのため,gen における h1 の element alias 属性は真となり,OUT は h1 が h2 を指し,h1 の element alias 属性は真となる.3 イタレーション目は 2 イタレーション目と同様に処理が進み,OUT が 2 イタレーション目の OUT と同一になるため,h1 が h2 を指し,h1 の element alias 属性が真という結果でデータフロー解析が収束する.

この例においては,各イタレーションで確保されたヒープオブジェクトが単純に同一の名前のオブジェクト h2 として扱われるため,各イタレーションで確保する領域が別の領域であることを認識できず,element alias 属性を正しく偽と設定できなかったことになる.そこで,第 3.4 節では Element-Sensitive ポインタ解析と Cycle-Sensitive ポインタ解析を併用することで,element alias 属性を解析する方法を示す.

# 3.4 Element-Sensitiveポインタ解析とCycle-Sensitive ポインタ解析の併用

ループのイタレーションを識別する Cycle-Sensitive 解析を実現する方法の一つ として , Aging[RRH08] という手法がある.この手法では , ヒープオブジェクトの

#### 3.4. Element-Sensitive ポインタ解析と Cycle-Sensitive ポインタ解析の併用

図 3.5: Cycle-Sensitive を利用しない Element-Sensitive ポインタ解析の適用例

名前付けを行う際に,確保されたヒープオブジェクトについて,現在のイタレーションで確保されたものなのか,前のイタレーションで確保されたものなのかを区別することで,簡易な実装で Cycle-Sensitive 解析を実現する.Aging により各イタレーションで確保するヒープ領域を識別することで,Element-Sensitive ポインタ解析において,element alias 属性を適切に設定することが可能となる.

# 3.4.1 Element-Sensitive ポインタ解析と Aging の併用例

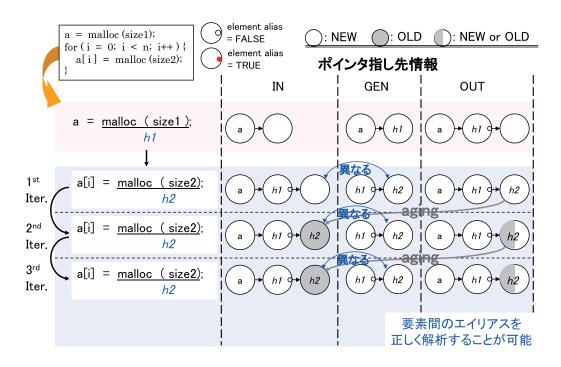

図 3.1 におけるデータ構造構築部分のコードを例に, Element-Sensitive ポインタ解析と Aging を併用した場合の解析イメージを図 3.6 に示す.

この例においても a が h1 を指すという情報を生成する地点までは , 図 3.5 と同様であるが , a[i] の指し先を動的確保するループの部分について , Aging を利用す

ることで解析の流れが変わってくる.

まず1イタレーション目では「h1 がh2 を指す」という解析情報がgen として生成される.このとき,Aging を用いる場合は,新たに確保されたヒープオブジェクトについては,NEW という属性が設定され,現在のループイタレーションで確保されたオブジェクトであることが明示される.この時点では,IN において h1 は未初期化状態のため,このイタレーションでは h1 の指し先が IN と gen で重複することはなく,OUT は h1 が h2 を指し,h1 の element alias 属性は偽という情報となる.

次にデータフロー解析の 2 イタレーション目の処理の開始時に Aging が適用され、h1 が h2 の NEW のオブジェクトを指す」という情報が「h1 が h2 の OLD のオブジェクトを指す」という情報に変化する.すなわち、IN の情報は h1 が h2 の OLD を指す、という情報となる.ここで gen の生成は 1 イタレーション目と同様に h1 が h2 の NEW を指すという解析情報となるため、h1 の指し先は IN では h2 の OLD 、gen では h2 の NEW となり、異なるオブジェクトなので h1 の element alias 属性は偽となる.そして、OUT は h1 が h2 の NEW または OLD を指し、h1 の element alias 属性は偽となる.3 イタレーション目の処理の開始時に再度 Aging が行われ、h1 が h2 の NEW または OLD を指す」という情報に変化する.その後は 2 イタレーション目と同様に処理が進み、OUT が 2 イタレーション目の OUT と一致するため、h1 が h2 の NEW または OLD を指す」という情報に変化する.その後は 2 イタレーション目と同様に処理が進み、OUT が 2 イタレーション目の OUT と一致するため、h1 が h2 の NEW または OLD を指し、h1 の element elem

#### 3.5. Element-Sensitive ポインタ解析の自動並列化への利用

図 3.6: Element-Sensitive ポインタ解析と Aging の併用例

# 3.5 Element-Sensitive ポインタ解析の自動並列化へ の利用

本節では Element-Sensitive ポインタ解析による解析情報の自動並列化への適用について述べる. Element-Sensitive ポインタ解析における element alias 属性の情報は,ポインタへのポインタを介したアクセスに対して,配列ベースのプログラム向けの自動並列化技術 [Wol96, LLL01, 吉田94] を適用するための条件となっている. これにより多次元配列をデータ構造としてプログラムを記述した場合と同様に自動並列化が適用可能となる.

#### 3.5.1 イタレーション空間における依存解析

自動並列化のためのループレベル並列性やデータローカリティ最適化はイタレーション空間におけるループ依存解析結果を元に行う.多次元配列においては,配列の添字とメモリアドレスが一意に対応可能なことから,ループ制御変数と依存ベクトルを用いてイタレーションスペースにおける依存解析が可能である.

ポインタアクセスされる領域についても,対象のループにおいてそのポインタを用いて添字アクセスを行う場合に,その添字とアクセスするメモリアドレスが一意に対応可能なことが保証できれば,多次元配列と同様にイタレーション空間における依存解析が可能となる.

#### 3.5.2 イタレーション空間における依存解析の例

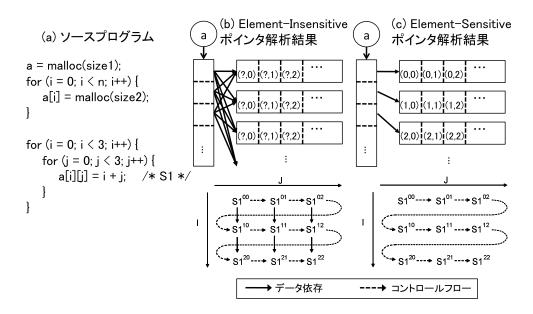

図3.1の例と同様のコードサンプル(図3.7(a))を用いた場合の Element-Insensitive および Sensitive ポインタ解析結果と、それぞれの場合のイタレーション空間における依存解析結果を示す。

図3.7(b)のElement-Insensitiveポインタ解析を適用した場合は,保守的にポインタの配列 a[i]の各要素が指しうるオブジェクトに重複がある可能性があるものとして解析する.指しうるオブジェクトに重複がある可能性がある場合は,Points-toグラフの葉ノードにあたるオブジェクト,すなわち添字の最右側次元のアクセスに対応するメモリ領域については,添字とメモリ領域との対応が一意となるため,安全に依存解析を行うことができる.よって,図中 a[i][j]のjによるアクセスではオブジェクトの先頭からのオフセットはjの値により一意に決定される.しかし,左側次元の添字については,メモリ上の領域との対応関係が不明なため,多次元配列のように依存解析を行うことはできない.

それに対し, Element-Sensitive ポインタ解析を適用した場合 (図 3.7(c)) は,ポ

図 3.7: ポインタ解析を利用したイタレーション空間における依存解析結果

インタの配列 a[i] の各要素が指す領域が独立していることを保証できるため,a[i][j] の各次元の添字のパターンとそのアクセス先のメモリ位置の対応付けが可能となり,多次元配列と同様に扱うことができる.

# 3.6 マルチコアシステム上での性能評価

本節では, Element-Sensitive ポインタ解析を適用した際の, コンパイラによる自動並列化結果について述べる. Element-Sensitive ポインタ解析の有無による処理性能の違いについて評価する.

第 3.2 節で述べた基準となる Flow-, Context-, Heap-, Field-Sensitive ポインタ解析, および第 3.3 節で述べた新たに提案する Element-Sensitive ポインタ解析と第 3.4 節で述べた Aging(Cycle-Sensitive ポインタ解析) を, OSCAR 自動並列化コンパイラ [笠原 03] に実装し評価を行った. OSCAR コンパイラを用いて自動並列化した際の 8 コア構成の SMP サーバである IBM p5 550Q における使用するコア

数と処理性能について評価を行う.

#### 3.6.1 自動並列化を適用する際のコンパイル手順

OSCAR コンパイラは C 言語等のソースコード変換をサポートしており,逐次の C 言語で記述されたプログラムに対して,OSCAR コンパイラは自動並列化を適用し,OpenMP[ope05] で並列化された C プログラムを自動生成する.このときに利用する OpenMP 指示文は parallel sections,flush,critical の 3 種類の指示文のみであり,OpenMP 仕様のうちこれらの構文をサポートしている環境であれば,並列コード生成が可能である.この 3 つのディレクティブは情報家電向けのマルチコア用並列処理 API である OSCAR API[OSC] においても,並列処理に必要なOpenMP 指示文のサブセットとして定義されている.

この OSCAR コンパイラにより自動生成された OpenMP C (OSCAR API C) プログラムを対象プラットフォームの OpenMP あるいは OSCAR API に対応したネイティブコンパイラによりコード生成を行う.

#### 3.6.2 評価対象プログラム

SPEC2000 より art のオリジナルコード, equake を並列処理向けに修正を行ったコード, および SPEC2006 より hmmer, lbm をポインタ解析精度を考慮して修正を行ったコード (Parallelizable C[間瀬 09]) に対して自動並列化を適用した.この Parallelizable C コードは, Element-Sensitive ポインタ解析を用いてもオリジナル C コードではポインタの指し先が解析できない場合に, ポインタ解析精度を考慮したソースコードの修正を行うことで自動並列化を適用可能としたものである.

IBM p5 550Q System Power5+ CPU  $(1.5\text{GHz} \times 2 \times 4)$ L1 D-Cache 32KB for 1 core L1 I-Cache 64KB for 1 core L2 cache 1.9MB for 2 cores L3 cache 36MB for 2 cores IBM XL C/C++ Native for AIX Compiler V10.1 Compiler OSCAR: -O5 -qsmp=noauto Compile Native: -O5 -qsmp=auto Option 備考 SMT: disabled

表 3.1: 評価環境

#### 3.6.3 評価環境

本評価においては,8 コア搭載の SMP サーバである IBM p5~550Q において評価を行った.評価環境のパラメータを表 4.2 に示す.

ただし、本章の評価では equake のみ IBM XL C/C++ コンパイラの最適化レベルを-O4 としている.これは、OSCAR コンパイラで自動生成した OpenMP プログラムを IBM XL C/C++ コンパイラで-O5 でコンパイルした際に正常に実行できなかったためである.本評価では並列処理による速度向上を評価するため、equake の全評価において最適化レベルを-O4 に統一した.

#### 3.6.4 自動並列化による処理性能

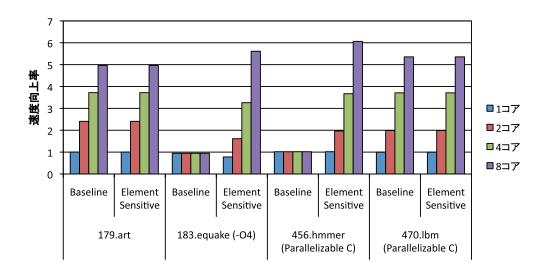

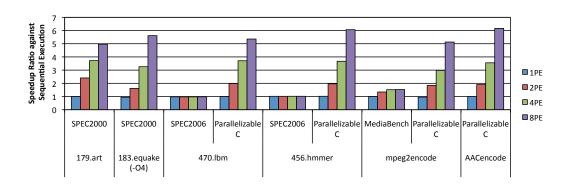

オリジナルコードと Parallelizable C に書き換えたコードそれぞれに対して , OSCAR コンパイラで自動並列化を適用した際の処理性能を示す . IBM p5 550Q における処理性能を図 3.8 に示す .

図中,横軸が各アプリケーションと使用するポインタ解析における Element-

Sensitive および Cycle-Sensitive の有無を示す. Baseline は基準となる Flow-, Context-, Heap-, Field-Sensitive ポインタ解析を利用して自動並列化を適用した場合, Element Sensitive は基準となるポインタ解析に加え, Element-Sensitive ポインタ解析と Aging を併用した場合を示す. 縦軸はオリジナルコードをネイティブコンパイラの1コアで逐次実行した場合に対する速度向上率を示す. 横軸の各項目内のバーは使用しているプロセッサコア数を示し,それぞれ左から1コア,2コア,4コア,8コアとなる.

#### IBM p5 550Q における処理性能

art, equake については Element-Sensitive ポインタ解析により自動並列化に必要なポインタの指し先情報を解析可能であり,図 3.8 に示すように,8 コア使用時に逐次実行時と比較して, art で 4.96 倍, equake で 5.61 倍の速度向上が得られた.hmmer, lbm についてはオリジナルコードは Element-Sensitive ポインタ解析を用いても十分なポインタ解析結果を得ることができなかったが,ポインタの利用法について若干の書き換えを行うことで,オリジナルコードの逐次実行時と比較して8コア使用時に hmmer で 6.06 倍, lbm で 5.35 倍の速度向上が得られた.これらの,ポインタ解析の解析精度を考慮して書き換えを行ったプログラムを含めると,Element-Sensitive ポインタ解析を用いた自動並列化により,逐次実行と比較して8コア使用時に平均 5.50 倍の性能向上が得られた.

このうち, Element-Sensitive ポインタ解析の利用によって大きな並列化効果が得られたのは equake と hmmer である. equake と hmmer については,基準となるポインタ解析では自動並列化による速度向上が全く得られていなかったが, Element-Sensitive ポインタ解析を利用することで自動並列化による大きな速度向上が得られた.

図 3.8: IBM p5 550Q における OSCAR コンパイラによる自動並列化結果

#### 3.6.5 OSCAR コンパイラによる自動並列化結果

評価を行った art, equake, hmmer, lbm の各アプリケーションプログラムについて, 適用された自動並列化の概要およびポインタ解析結果を以下に示す.

#### SPEC2000 art

art では、オリジナルの C ソースコードを修正すること無く、自動並列化による 速度向上を得ることができた. art では、Element-Insensitive の基準となるポイン タ解析において、OSCAR コンパイラの自動並列化により 8 コア使用時に 4.96 倍 の性能向上が得られている.

art の主要なデータ構造は、複数のスカラ変数をメンバに持つ構造体の配列が ヒープ領域に確保され、ポインタを介してアクセスされる形状となっている。す なわち、主要なデータ構造は構造体の1次元配列となっており、主要なループは 構造体の配列の各要素に対して処理を行う。そのため、基準となるポインタ解析 でも十分にポインタの指し先が解析されていた。

#### SPEC2000 equake

equake では Element-Insensitive ポインタ解析では自動並列化による速度向上を得ることができなかったが, Element-Sensitive ポインタ解析により 5.61 倍と大きな速度向上が得られた.

これは, equake の主要なデータ構造が図 3.1 で示したようなポインタへのポインタとヒープ領域を用いたデータ構造となっており,解析には Element-Sensitive ポインタ解析が必要不可欠となるためである.

#### SPEC2006 hmmer

オリジナルコードでは Element-Sensitive ポインタ解析を用いても,自動並列化による速度向上を得ることができなかったため,自動並列化可能となるように Parallelizable C に書き換えたコードに対する自動並列化結果を示している. Parallelizable C で記述することで,OSCAR コンパイラによる自動並列化により IBM p5 550Q で 8 コア使用時に 6.06 倍の速度向上が得られた.

hmmer のソースコード中にはポインタの配列は存在しないが,自動並列化の過程で,ループディストリビューションおよびスカラエキスパンションが適用され,その後に Element-Sensitive ポインタ解析が行われることで,大きな速度向上が得られた.すなわち,自動並列化の過程において,ソースコード上でスカラ変数であったポインタ変数を,コンパイラの中間表現ではポインタの配列として扱っている.このように,コンパイラにおけるプログラムリストラクチャリング適用後の解析情報の表現に Element-Sensitive ポインタ解析が有用となる.

#### SPEC2006 lbm

lbm においても、オリジナルコードでは Element-Sensitive ポインタ解析を用いても、自動並列化による速度向上を得ることができなかったため、図 3.8 では自動並列化可能となるように Parallelizable C に書き換えたコードに対する自動並列化結果を示している.Parallelizable C で記述することにより、OSCAR コンパイラによる自動並列化により 8 コア使用時に 5.36 倍の速度向上が得られた.lbm の主要なデータ構造はヒープ上に確保された 1 次元化された配列であり、Parallelizable C に書き換えを行うことにより、基準となるポインタ解析で自動並列化可能となった.

# 3.7 関連研究

従来よりポインタ解析の精度と効率について多くの研究がなされており [Hin01] , 現在では従来高精度とされてきたポインタ解析も実用的な時間で実現可能となっ ており, さらなる精度向上も現実的となっている.

Flow-Sensitive, Context-Sensitiveのポインタ解析は古くはデータフロー解析により定式化され, Emamiら [EGH94] による関数ポインタを考慮したアルゴリズムや、Wilsonら [WL95] によるPartial Transfer Functionを用いたインタープロシージャ解析アルゴリズムが提案されている. Flow-SensitiveのアルゴリズムもContext-Sensitiveのアルゴリズムも最悪計算量が指数関数時間となる. 現在ではより効率のよいアルゴリズムが提案されているが、しかしながら、当時のFlow-Sensitive, Context-Sensitiveポインタ解析は高い解析精度を持っていたものの解析効率が低く、数万行程度のプログラム規模までしか実用的な時間で解析することができなかった. そのため、解析効率の高い Flow-Insensitive 解析手法について研究がなされ、型推論によって定式化された Andersen の Subset-Based の多項式時間のアルゴリズム [And94] と、精度が劣るがほぼ線形時間で解析可能である Steensgaard の Inclusion-

Based のアルゴリズム [Ste96] が提案された.その後はより精度の高い解析を効率的に実現する手法が研究され, Heintzeら [HT01] により Subset-Based で100万行のプログラムの解析までスケールアップする Flow-Insensitive, Context-Insensitive アルゴリズムが提案された.さらに, Berndlら [BLQ+03] や Whaleyら [WL04] による BDD を用いたポインタ解析により, Subset-Based, Flow-Insensitive, Context-Sensitive 解析が実用的な時間で可能となった.そして, Kahlon [Kah08] の精度の低いポインタ解析で対象の問題を分割することで高い精度のポインタ解析を適用する対象問題を小さくする手法や, Hardekopfら [HL09] による Semi-Sparse ポインタ解析, Yuら [YXH+10] による Full-Sparse ポインタ解析により, 現在では Flow-Sensitive 解析も実用的な解析時間で実現可能となっている.

ヒープの扱いについても精度の議論が行われており、プログラム上のヒープを確保する malloc()等の関数呼び出しのステートメントごとに別の領域として扱う方式が主流であったが、さらにヒープを確保する関数のコーリングコンテクストごとに領域を区別して扱う Heap-Sensitive あるいは Heap-Cloning と呼ばれる手法 [NKH04] が提案されており、ヒープを確保する際にラッパ関数を用いるような場合に必要な解析精度となっている。また、構造体のメンバの扱いについても議論が行われており、メンバを全て別の領域として扱う Field-Sensitive 解析を効率的に扱う手法が Pearce ら [PKH04] により提案されている。Lattner ら [LLA07] は Heap-Cloning と Field-Sensitive を両立した Context-Sensitive 解析を実用的な時間で可能な手法を提案している。

このように,現在では Flow-, Context-, Heap-, Field-Sensitive なポインタ解析も実用的に利用可能となっており,本章ではこれらの研究成果をベースとして, Element-, Cycle-Sensitive なさらに高精度なポインタ解析を実現した.

本章で Cycle-Sensitive 解析を実現するために利用した Aging[RRH08] は , ループのイタレーションの先頭でバッファを確保し , 次のイタレーションでも使い回す

ようなパターンに対する解析として提案された.このような例では,通常のデータフロー解析では,各イタレーションで確保されるバッファがデータフロー解析の収束演算により同一領域とみなされてしまう.そこで,Aging を適用することで,そのイタレーションで確保されたヒープ領域とそれ以前のイタレーションで確保されたオブジェクトを別のオブジェクトとして解析可能とすることを可能としている.Aging の提案においても Element-Sensitive 解析との補完関係について言及されていたが,実際に本章で提案する Element-Sensitive ポインタ解析と Aging を併用することで高い解析精度を得ることができた.

既存の Element-Sensitive ポインタ解析として,ポインタの配列の各要素とヒープオブジェクトを確保したループイタレーションの情報をマッピングする Element-Wise Points-to Set [WFPS02] がある.Element-Wise Points-to Set は Java の自動並列化を指向して提案されたもので,シンボリック式を用いてオブジェクトの対応関係を計算している.本章で提案する方式では element alias 属性という真偽値のみで表現しているが,これだけで自動並列化のための解析を行う必要条件を満たしており,軽量で効率的な実装が可能となる.

Points-to 解析ではなく、任意のポインタ変数の間のエイリアス関係を解析するポインタ解析も提案されている.Connection 解析 [GH96a] では複数のポインタオブジェクトが指し示す領域に重なりがないかどうかを解析する.本章で提案した element alias は複数のポインタオブジェクトの関係ではなく、単一オブジェクトの各要素の指し先の関係を解析するものであるが、Connection 解析と同様の概念を採用している.

また,リスト構造や木構造のように自身の構造体型へのポインタを持つような, 再帰的なデータ構造に特化したポインタ解析が存在する. Shape 解析 [GH96b] ではポインタの指し先の具体的なオブジェクトを解析するのではなく,ポインタが指し示すデータ構造が木構造なのか DAG なのかサイクルなのか,といったデータ

構造の解析を行う.しかしながら,既存の高度な並列化あるいはデータローカリティ最適化技術 [Wol96, LLL01, 吉田94] は主に多次元配列とループによる処理を対象としており,再帰的なデータ構造には対応していないのが現状である.そのため,再帰的なデータ構造に対する並列化技術と併せた解析手法の改良が今後の課題となる.

### 3.8 まとめ

本章ではコンパイラによる自動並列化のためのポインタ解析として Element-Sensitive ポインタ解析を提案した.提案した Element-Sensitive ポインタ解析は,element alias という真偽値型の変数のみによる表現により,軽量で効率的な実装を可能とし,既存の Flow-Sensitive ポインタ解析を容易に拡張可能である.Element-Sensitive ポインタ解析と Cycle-Sensitive ポインタ解析の併用により,C 言語で頻出のデータ構造に対する自動並列化を可能とし,本手法が有効なアプリケーションプログラムが存在することを示した.科学技術計算およびマルチメディア処理を行う4つのプログラムに対して Element-Sensitive ポインタ解析を利用した自動並列化を適用し,マルチコアシステム上での処理性能の評価を行ったところ,8 コア構成のサーバである IBM p5 550Q において逐次実行時と比較して平均 5.50 倍の速度向上が得られた.

本章で提案した Element-Sensitive ポインタ解析により,既存のCプログラムの自動並列化による速度向上に加え,ユーザプログラマがプログラムを修正することによる自動並列化の適用可能性も広がる.ポインタ解析を利用したユーザプログラマへのプログラム書き換え支援ツールの開発等により,マルチコア向けソフトウェア開発における自動並列化の利用を促進し,ソフトウェア生産性の向上が実現可能と考えられる.

# 第4章

## Parallelizable C

## 4.1 はじめに

マルチコアプロセッサを含め、マルチプロセッサシステム用の並列プログラミングは難易度が高く、所望の性能を得るために長期間の並列チューニングが必要であることで知られており、並列ソフトウェア生産性向上が大きな課題となっている。そのため、CやFORTRANのような既存の逐次型プログラムをコンパイラで自動並列化することによる、短時間での高性能の実現が強く期待されている。

従来より科学技術計算分野のFORTRANプログラムに対しては,Poralis[EHP98], SUIF[HAA+96], OSCAR[笠原 03] といった高性能な自動並列化コンパイラが開発され,多くの並列マシン上で,その有効性が確認されてきた.しかしながら,C言語ではポインタを多用した自由な記述が可能であり,コンパイラによるポインタ解析において,ポインタの指し先を静的に特定するのは非常に困難である[Hin01]. 冗長なポインタエイリアス情報が存在することにより,コンパイラによる依存解析の精度が劣化することが,自動並列化の阻害要因となっている.

そこで、Cプログラムの記述を制約することで自動並列化コンパイラによる階層的な並列性の利用やキャッシュ、ローカルメモリ最適化といった高度な並列処理手法の利用を可能とするために、Cプログラム記述のガイドラインとして Parallelizable Cを提案する. Parallelizable Cでプログラムを記述することにより、プログラマはアルゴリズムのチューニングに専念し、煩雑な並列処理向けのテクニックはコンパイラにより自動で適用可能となる.

C言語の記述の自由度を用途に合わせて制限するコーディングガイドラインは,主に車載ソフトウェア向けの高信頼性,高安全性,高移植性を目的とした MISRA-C[MIS04] に代表されるように,産業界で広く普及している.マルチプロセッサ向けの自動並列化においても,IMEC によるマルチプロセッサ向けのコーディングガイドラインである Clean C[Cle] や,Hwu らにより assertion 等によるヒント情報を用いて自動並列化コンパイラを有効利用する暗黙的な並列プログラミングモ

デル [HRU+07] が提案されている.このようなガイドラインを設定する場合に,そのプログラム記述が現実的かどうか,つまり実際にどの程度の自動並列化の効果が得られるか,そしてその記述法がプログラマに不自由なプログラム記述を強制していないかどうかが,そのガイドラインの普及に向けた課題となる.

本章で提案する Parallelizable C は C 言語のサブセットとして定義され, C 言語の処理系で正常にコンパイルし実行可能である. Parallelizable C を利用したプログラム開発では,フルセットの C プログラムのうち,並列化を意識したい部分をParallelizable C 言語で書き換えることで,それに応じた自動並列化を可能とすることを目指している.並列処理による高速化が期待されている,科学技術計算およびマルチメディア処理の逐次プログラムについて書き換えを行ったところ,それらは少量の書き換えにより,コンパイラによる自動並列化が適用可能であることを確認した.

本章の構成を以下に示す.まず第4.2節ではParallelizable Cの概念について,第4.3節ではParallelizable Cのコーディングルールについて述べる.第4.4節ではParallelizable Cへのプログラム書き換えについて述べ,そして,第4.5節では性能評価に利用したOSCAR コンパイラの概要について,第4.6節ではParallelizable Cプログラムに対してOSCAR コンパイラの自動並列化を適用した際のマルチコアシステム上での処理性能について述べる.第4.7節で関連研究について述べ,第4.8節でまとめを述べる.

## 4.2 Parallelizable Cの概念

第3章で述べたポインタ解析の実装により,コンパイラによる自動並列化の適 用範囲が拡大可能になっていくと考えられる.しかし,C言語のあらゆる仕様を 網羅するポインタ解析の実装は事実上不可能であり,自動並列化コンパイラを現

実的に利用していく上では,解析可能な C プログラムの記述を明確化し,その範囲でプログラムを記述する必要がある.

#### 4.2.1 C言語のコーディングガイドライン

Parallelizable C は C 言語のサブセットで定義されるコーディングガイドラインあり, C 言語の処理系で正常にコンパイルし実行可能である。本章で提案するParallelizable C を利用したソフトウェア開発では, C プログラムのうち, 並列化を意識したい部分を Parallelizable C の要件を満たすように書き換えることで,それに応じた並列性抽出を可能とすることを目指している。Parallelizable C の記述は,対象のコンパイラの解析器の精度に大きく左右されるため,コンパイラの解析精度が高くなるほど,プログラム記述ルールの制約が緩和され,プログラマの負荷を軽減することができる。

#### 4.2.2 対象のコンパイラの解析精度

本章では以下のようなポインタ解析機能を持つコンパイラを想定して Parallelizable C のコーディングルールを決定する .

- ステートメントごとにコントロールフローに沿った解析を行う (flow-sensitive)

- 関数の呼び出し箇所ごとに解析を行う (context-sensitive)

- メモリ動的確保までの関数呼び出し経路ごとにヒープオブジェクトを区別する (heap-cloning)

- 構造体のメンバをそれぞれ別のオブジェクトとして扱う (field-sensitive)

- ポインタがオブジェクトの先頭を指すかどうかを判別する

- ポインタの配列について各要素の指し先に重なりがないかを判別する

- ヒープオブジェクトを確保したイタレーションを判別する

また,構造体の解析においては以下のような機能を持つものとする.

- スカラとして扱う構造体のメンバは別のオブジェクトとして扱う

- 配列として扱う構造体はそれ自体を配列オブジェクトとして扱い,配列要素内のメンバの区別は行わない

ここで,ポインタの指し先の領域についても,そのポインタからの逆参照時のオフセットが必ずゼロとなるような領域はスカラ,オフセットがゼロ以外になる場合がある領域は配列として扱うものとする.

## 4.3 Parallelizable Cのコーディングルール

本節ではポインタ解析をサポートしたコンパイラを想定した, Parallelizable Cのコーディングルールについて述べる.本仕様はC言語記述におけるルールと,コンパイル時の外部関数に対するヒント情報から構成される.

#### 4.3.1 C言語記述におけるルール

Parallelizable Cでは本節で述べるルールに従ってプログラムの記述を行うものとする.ただし, Parallelizable CはフルセットのC言語に対応した処理系でコンパイルされるため,プログラマの判断でルールを逸脱することも許されるが,コンパイラによる自動並列化は困難になる.

以下に, Parallelizable CのC言語記述におけるルールを示す.

変数宣言の境界を超えたアクセスを行わない

構造体のメンバや多次元配列の各次元の境界を越えたアクセスを行わない. C コンパイラでは処理系により正常動作することもあるが, C 言語仕様上は未定義である.

#### ポインタのキャストを行わない

メモリ動的確保時を除いて,ポインタのキャストを行わない.ポインタ参照先のオブジェクトのオフセットを正しく解析するためである.

#### ポインタ算術演算を行わずに添字アクセスを行う

ポインタ算術演算は行わない.ポインタ指し先の領域にアクセスする場合には ポインタ変数の値は更新せずに,ポインタ変数に対する逆参照演算子(\*)もしくは 添字アクセス([])により行うこととする.

#### 条件分岐やループ内でポインタ変数への値の代入を行わない

メモリ動的確保時を除いて,条件分岐やループ内ではポインタ変数への値の代 入を行わない.

#### 同一領域に対する複数のポインタを関数の引数として渡さない

配列の単一次元内の異なるオフセットのアドレスを関数の引数として渡さない. ただし,同一配列でも重なりのない部分配列であればよい.これは,2つの引数の指し先を別々のオブジェクトとして扱えなくなるためである.

#### 一時バッファとして利用するヒープ領域を使い回さない

ヒープ領域の使い回しは,通常の変数の使い回しよりも解析が困難であり,並列性抽出の阻害要因となる.ヒープ領域を使い回す例としては,ループのボディにおいてのみ利用するバッファ領域を複数ループイタレーションに渡って確保し続けて再利用する,といったことが挙げられる.

#### 構造体の配列のメンバに対する配列アクセスを行わない

配列メンバを持つ構造体の配列を使用しない.構造体のメンバに配列がある場合は,下位の関数に構造体の1要素にあたる領域を引数として渡し,下位の関数内でそのメンバの配列へのアクセスを行う.これは配列要素間と同様に,構造体のメンバ間の識別精度も解析精度に影響するためである.

#### 再帰的なデータ構造を利用しない

リストや木構造等,再帰的に同じ型の構造体オブジェクトへのリンクがあるデータ構造を使用しない.リストや木構造であれば並列処理可能なことがあるが,リストや木構造の解析には専用の解析が必要となる.配列ベースの記述であればコンパイラによる高度な最適化が適用できるため,配列型のデータ構造に変換してから計算処理を行うこととする.

#### 呼び出し間に依存のある外部関数を使用しない

ファイル入出力,エラー処理等の,ライブラリ内で内部状態を持ち,呼び出しごとに依存がある外部関数を使用しない.エラー処理やログ出力は並列化したい部分の外側にくくり出す等の工夫が必要である.

#### 関数の再帰呼び出しを使用しない

関数は直接的か間接的かに関わらず,その関数自体を呼び出さない.コールグラフを静的に決定できなくなったり,メモリ使用量の見積もりが難しくなったりするためである.

#### 関数ポインタを使用しない

関数ポインタを使用せず switch-case を用いて関数呼び出しを記述する.これは関数の呼び出し先の静的な解析が難しくなるためである.

#### 可変個引数を持つ関数を定義しない

可変個引数には未定義の動作が多いためである.

#### 4.3.2 外部関数に関するヒント情報

プログラム全体に対して解析を行うことを前提としているが,ライブラリ関数等を利用する場合は,そのライブラリ関数による挙動をディレクティブやコンパイルオプションにより指示することでコンパイラの解析精度劣化を防ぐことができる.そのような指示を行う方法としては,以下のようなヒント情報が挙げられる.

- 外部関数においてポインタ引数の指し先は変化しないことを仮定する

- 外部関数からの戻り値がポインタ型の場合,そのポインタの指し先は新たに 領域確保されたヒープ領域であることを仮定する

- ◆ 外部関数における入出力変数についてのデータフロー情報を指定する

|                        | 合計    |                  | 削除量   | 追加量   | 変更率   |

|------------------------|-------|------------------|-------|-------|-------|

| アプリケーションプログラム          | (LOC) | 書き換え項目           | (LOC) | (LOC) | (%)   |

| SPEC2000 art           | 1270  | N/A              | 0     | 0     | 0%    |

| SPEC2000 equake        | 1513  | N/A              | 0     | 0     | 0%    |

| SPEC2006 lbm           | 1155  | オブジェクト先頭以外へのポインタ | -7    | +7    | 1.8%  |

|                        |       | ループ内のポインタ更新      | -10   | + 14  |       |

| SPEC2006 hmmer         | 35992 | ヒープ領域の再利用        | -9    | +8    | 0.03% |

| Mediabench mpeg2encode | 3750  | アルゴリズムの変更        | -640  | +864  | 23.5% |

表 4.1: Parallelizable C への書き換え項目とコード変更量

## 4.4 Parallelizable Cへのプログラム書き換え

本節ではSPEC2000より art, equake, SPEC2006より lbm, hmmer, MediaBench より mpeg2encode を例に, Parallelizable Cへの書き換えについて述べる.

各アプリケーションの書き換えにおいては,まず最初にファイルを一つにまとめて,入出力や時間計測用のコードを整備した参照コードを作成し,それに対して書き換えを行った際の修正箇所を調べた.

書き換えの過程においては、Parallelizable C に適合するための書き換えに加えて、プログラムの持つ並列性を十分に抽出するためのプログラム構造の書き換えも行った。

### 4.4.1 書き換え項目とコード変更量

Parallelizable Cへの書き換えのコストを定量化するために,書き換え項目のリストアップおよび,書き換えの際の変更前のコードサイズを基準とした,削除量と追加量の割合を計測した.計測方法は,各ソースコードのインデントを無くしてから,行単位の diff を取り,削除側,追加側それぞれの行数をカウントした.表4.1 にそれぞれのアプリケーションごとの,Parallelizable Cへの書き換え項目および削除量,追加量の割合を示す.また,このときの削除量と追加量のうちの大きい方を変更量とする.

#### 4.4.2 コード書き換え内容

${

m SPEC} 2000$  の  ${

m art}$  については , オリジナルコードの時点で  ${

m Parallelizable}$   ${

m C}$  のルールに適合していたため , 書き換えは行わなかった .

SPEC2000のequakeについては, Parallelizable Cのルールには適合していたが, Parallelizable Cコードでは,プログラム実行時間の大部分を占める関数 smvp()において,配列全体に対するリダクション処理による並列化を行うために手動でリストラクチャリングを行った.

SPEC2006の lbm については、配列の途中を指すポインタと、ループ中におけるポインタ変数の更新があったため、Parallelizable C コードではそれらの除去を行った。図 4.1(a) のようなループ中でのポインタ更新については、図 4.1(b) のようにフラグ変数と条件分岐を用いて修正した。

SPEC2006 の hmmer については、図 4.2(a) のように、複数イタレーションに渡ってバッファ領域を使い回していたため、Parallelizable C コードでは図 4.2(b) のように各イタレーションごとに領域を確保して解放するように修正した.

mpeg2encode では,MPEG2 エンコードアルゴリズムが持つマクロブロックレベルの並列性とデータローカリティが利用不可能なプログラム構造となっているため,並列性抽出のためのプログラム構造の変更[小高 05] を併せて行った.

## 4.5 OSCAR 自動並列化コンパイラの概要

OSCAR コンパイラ [笠原 03] は C や FORTRAN 言語で記述された逐次ソースプログラムを入力し,並列プログラムを自動生成する自動並列化コンパイラである.従来は,FORTRAN77向けに開発されていたが,新たにCフロントエンド,Cソースコード生成部,ポインタ解析器の実装等の拡張を行うことで,C言語の自動並列化にも対応した.

```

for( t = 1; t <= param.nTimeSteps; t++ ) {

...

LBM_performStreamCollide( *srcGrid, *dstGrid ); /* 主要計算部 */

LBM_swapGrids( &srcGrid, &dstGrid ); /* srcGrid と dstGrid のポインタ値を交換する */

...

}

(a) オリジナルコード

flg = 0;

for( t = 1; t <= param.nTimeSteps; t++ ) {

...

if (flg % 2)

LBM_performStreamCollide( *dstGrid, *srcGrid ); /* 主要計算部 */

else

LBM_performStreamCollide( *srcGrid, *dstGrid ); /* 主要計算部 */

flg++;

...

}

```

図 4.1: lbm におけるループ中でのポインタの更新の除去

(b) Parallelizable C $\neg \vdash \vdash$

OSCAR コンパイラではループイタレーションレベルの並列処理を行うのみでなく,ループ・手続き間の粗粒度タスク並列処理 [本多 90],ステートメント間の近細粒度並列処理 [木村 01] を組み合わせたマルチグレイン並列処理 [笠原 03],メモリウォール問題に対処するための複数ループにわたるキャッシュあるいはローカルメモリの最適利用 [吉田 94, 石坂 02] が実現されている.さらに,プログラム中の各並列処理部に対する適切なリソース割り当てや,各リソースの周波数・電圧・電源制御による消費電力の自動削減 [白子 06] が実現されている.

## 4.6 マルチコアシステム上での性能評価

本節では、Parallelizable C プログラムを OSCAR コンパイラで自動並列化した際の PC,サーバ、組込み機器向けのそれぞれのマルチコアシステム上における使用するコア数と処理性能について評価を行う。

```

static void main_serial_loop() {

mx = CreatePlan7Matrix(1, hmm->M, 25, 0); /* P7Viterbi() で使用するデータ構造を malloc */

for (idx = 0; idx < nsample; idx++)</pre>

score = P7Viterbi(..., mx); /* 主要計算部 */

}

}

static float P7Viterbi(char *dsq, int L, struct plan7_s *hmm, struct dpmatrix_s *mx) {

ResizePlan7Matrix(mx, ...); /* 作業領域を realloc により使い回す */

... /* score の計算 */

return score:

(a) オリジナルコード

static void main_serial_loop() {

for (idx = 0; idx < nsample; idx++)</pre>

score = P7Viterbi(...); /* 主要計算部 */

}

}

struct dpmatrix_s *mx;

mx = AllocPlan7Matrix(...); /* イタレーションごとに作業領域を malloc */

... /* score の計算 */

FreePlan7Matrix(mx); /* イタレーションごとに作業領域を free */

return score;

}

```

図 4.2: hmmer におけるバッファの使い回しの除去

(b) Parallelizable C コード

#### 4.6.1 評価方法

OSCAR コンパイラによる並列化の際には,データローカリティ最適化を含めたマルチグレイン並列化を適用し,OpenMP[ope05] で並列化された C プログラムを出力する.このときに利用する OpenMP 指示文は OSCAR API[OSC] で規定されている OpenMP 指示文のサブセット部分にあたる.

自動生成された OpenMP C (OSCAR API C) プログラムを対象プラットフォームの OpenMP あるいは OSCAR API に対応したネイティブコンパイラによりコード生成を行う.また,ネイティブコンパイラにおいて自動並列化をサポートしている環境については,ネイティブコンパイラによる自動並列化結果も併せて示す.

#### 4.6.2 評価対象プログラム

第4.4節で述べた,SPEC2000 より art, equake,SPEC2006よりlbm,hmmer, MediaBench より mpeg2encode の 5 種類の C プログラムについて,オリジナル C コードと Parallelizable C コードそれぞれに対し,OSCAR コンパイラによる自動 並列化を適用した際の処理性能を示す.また,本章では書き換えを行っていないが,Parallelizable C を満たすように実装されている音声圧縮プログラムである AAC エンコード (AACencode) についても,併せて評価を行う.AAC エンコードは株式 会社ルネサステクノロジ提供のプログラムであり,関数の引数ポインタ以外のポインタ・構造体を原則的に使用せずに製品レベルのミドルウェア仕様を参照実装したものである [間瀬 07].

#### 4.6.3 評価環境

本評価においては,8 コア搭載の SMP サーバである IBM p5 550Q,Intel の 4 コア CPU である Core i7 を 1 基搭載した PC,ルネサステクノロジ,日立製作所,早稲田大学で共同開発した情報家電用マルチコア RP2[IHY $^+$ 08] における SH-4A を 4 コア構成による SMP モードの 3 つの環境で評価を行った.各環境におけるパラメータを表 4.2 に示す.IBM p5 550Q では,1 プロセッサあたり 2 スレッド実行の Simultanemous Multi-Threading(SMT) が可能であるが,本評価で SMT は用いないものとした.同様に,Intel Core i7 においても 1 プロセッサあたり 2 スレッド実行の Hyper-Threading が可能であり,またチップ温度を計測してハードウェアで自動的にオーバークロックする Turbo Boost が利用可能であるが,本評価では共に用いないものとした.

Renesas/Hitachi/Waseda RP2 System IBM p5 550Q Intel Core i7 920 Power5+ Nehalem SH-4A CPU $(1.5\text{GHz} \times 2 \times 4)$  $(2.66GHz \times 4)$  $(600MHz \times 4)$ L1 D-Cache 32KB for 1 core 32KB for 1 core 16KB for 1 core L1 I-Cache 64KB for 1 core 32KB for 1 core 16KB for 1 core L2 cache 1.9 MB for 2 cores256KB for 1 core 36MB for 2 cores L3 cache 8MB for 4 cores IBM XL C/C++ Intel C/C++ SH C Compiler Native for AIX Compiler V10.1 Compiler verion 11.0 + OSCAR API Parser Compiler OSCAR: -O5 -qsmp=noauto OSCAR: -fast -openmp Compile Option Native: -O5 -qsmp=auto Native: -fast -parallel

表 4.2: 評価環境

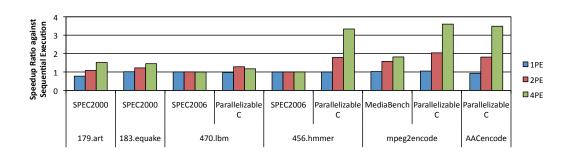

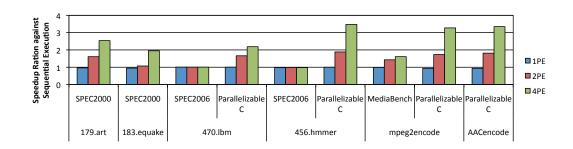

#### 4.6.4 自動並列化による処理性能

オリジナルコードと Parallelizable C に書き換えたコードそれぞれに対して,OSCAR コンパイラで自動並列化を適用した際の処理性能を示す.IBM p5 550Q における処理性能を図 4.3 に,Intel Core i7 における処理性能を図 4.4 に,ルネサステクノロジ / 日立製作所 / 早稲田大学 RP2 における処理性能を図 4.5 に示す.

図中,横軸が各アプリケーションとコードの種類を示し,縦軸はオリジナルコードをネイティブコンパイラの1コアで逐次実行した場合に対する速度向上率を示す.横軸の各項目内のバーは使用しているプロセッサコア数を示し,それぞれ左から1PE,2PE,4PE,8PEとなる.

#### IBM p5 550Q における処理性能

OSCAR コンパイラでは各アプリケーションのオリジナルコードに対して,8 コア使用時に逐次実行時と比較して,artで 4.96 倍,equake で 1.69 倍,mpeg2encode で 1.53 倍の性能向上を得ることができた. さらに,Parallelizable C で書き換えを行うことで,オリジナルコードの逐次実行時と比較して equake で 5.61 倍,lbm で 5.35 倍,lbm で 6.06 倍,mpeg2encode で 5.12 倍の性能向上が得られた.また,元々Parallelizable C で記述されている AAC エンコーダでは 6.16 倍の性能向上が

得られた.以上をまとめると, Parallelizable C で記述されたプログラムを OSCAR コンパイラで自動並列化することで,逐次実行と比較して平均 5.54 倍の性能向上が得られた.

なお, IBM p5 550Qの評価においては, equake のみ最適化レベルを-O4としている. これは, Parallelizable C コードを OSCAR コンパイラで生成した OpenMP プログラムを IBM XL コンパイラで-O5 でコンパイルした際に正常に実行できなかったためである. 本評価では並列処理による性能向上を評価するため, equake の全評価において最適化レベルを-O4 に統一した.

#### Intel Core i7における処理性能

OSCAR コンパイラではオリジナルコードに対して,4コア使用時に逐次実行時と比較して art で 1.51 倍, equake で 1.15 倍, mpeg2encode で 1.81 倍の性能向上を得ることができた.さらに,Parallelizable C で書き換えを行うことで,オリジナルコードの逐次実行時と比較して equake で 1.45 倍,lbm で 1.28 倍,hmmer で 3.34 倍,mpeg2encode で 3.60 倍の性能向上が得られた.また,元々Parallelizable C で記述されている AAC エンコーダでは 3.48 倍の性能向上が得られた.以上をまとめると,Parallelizable C で記述されたプログラムを OSCAR コンパイラで自動並列化することで,逐次実行と比較して4コア使用時に平均 2.43 倍の性能向上が得られた.

#### ルネサステクノロジ / 日立製作所 / 早稲田大学 RP2 における処理性能

OSCAR コンパイラではオリジナルコードに対して,4コア使用時に逐次実行時と比較して art で 2.53 倍, equake で 1.33 倍, mpeg2encode で 1.61 倍の性能向上を得ることができた. さらに, Parallelizable C で書き換えを行うことで,オリジ

図 4.3: IBM p5 550Q における OSCAR コンパイラによる自動並列化結果

図 4.4: Intel Core i7 920 における OSCAR コンパイラによる自動並列化結果

ナルコードの逐次実行時と比較して equake で 1.95 倍, mpeg2encode で 3.27 倍の性能向上が得られた.また,元々Parallelizable C で記述されている AAC エンコーダでは 3.34 倍の性能向上が得られた.以上をまとめると, Parallelizable C で記述されたプログラムを OSCAR コンパイラで自動並列化することで,逐次実行と比較して 4 コア使用時に平均 2.78 倍の性能向上が得られた.

なお ,  $\mathrm{SPEC}2006$  のアプリケーションについては , 本章では  $\mathrm{RP}2$  上での評価を行っていない .

図 4.5: ルネサステクノロジ / 日立製作所 / 早稲田大学 RP2 における OSCAR コンパイラによる自動並列化結果

#### **4.6.5** OSCAR コンパイラによる自動並列化結果

本章で書き換えを行った art, equake, lbm, hmmer, mpeg2encode について,適用された自動並列化の概要を以下に示す.その際に, IBM XL コンパイラ, Intel コンパイラによる自動並列化結果についても併せて示す.

#### SPEC2000 art

art では,オリジナルコードにおいて,OSCAR コンパイラの自動並列化により IBM p5 550Q において8コア使用時に4.96 倍の性能向上が得られている.art では実行時間の95% 程度は train\_match と match という2 つの関数によって占められており,ともに処理の大部分は7つの並列化可能なループの収束演算によって占められている.OSCAR コンパイラではこれらのループを並列化することにより性能向上が実現された.

IBM XL コンパイラ, Intel コンパイラでは自動並列化による性能向上は得られなかった.

#### SPEC2000 equake

オリジナルコードでは IBM p5 550Q において8コア使用時に 1.69 倍と性能向上が限定的であったが,書き換えを行うことで 5.61 倍と大きな性能向上が得られるようになった.書き換えを行った smvp()のループでは,配列全体に対するリダクション計算が行なわれている.各プロセッサごとに対象の配列の一時配列を用意し,各プロセッサで配列の全要素について,部分和の計算結果を一時配列に格納する.その後,各プロセッサで部分和を格納した一時配列について,その総和を元の対象配列に格納することで,並列処理を実現している.このため,配列全体のコピーを行うオーバーヘッドにより逐次処理時間が 20%ほど増加しているが,プログラムの大部分が並列処理可能となり,プロセッサコア数に応じた性能向上が得られた.

XL コンパイラ, Intel コンパイラではオリジナルコード, Parallelizable C コードともに自動並列化による性能向上は得られなかった.

#### SPEC2006 lbm

オリジナルコードでは自動並列化による性能向上を得ることができなかったが、 Parallelizable C に書き換えることで、OSCAR コンパイラによる自動並列化により IBM p5 550Q で 8 コア使用時に 5.36 倍の性能向上が得られた.

lbm ではLBM\_performStreamCollide という関数が実行時間の90% 程度を占めており、この関数は単一の並列化可能なループで構成されている.オリジナルコードでは、この関数の呼び出し部を含むループにおいてポインタの更新が行われており(図 4.1)、このポインタ更新により、ポインタの指し先情報が曖昧になっていたことが並列性抽出の阻害要因となっていた.これを、Parallelizable C への書き換えによって、ポインタの更新を除去することにより並列性抽出が可能となり、大

きな性能向上が得られた.

IBM XL コンパイラでは自動並列化による性能向上は得られなかったが, Intel コンパイラではオリジナルコード, Parallelizable C コード共に自動並列化による性能向上が得られており, OSCAR コンパイラによる Parallelizable C コードの自動並列化時と同等の性能となっていた.

#### SPEC2006 hmmer

オリジナルコードでは自動並列化による性能向上を得ることができなかったが, Parallelizable C に書き換えることで, OSCAR コンパイラによる自動並列化により IBM p5 550Q で 8 コア使用時に 6.06 倍の性能向上が得られた.

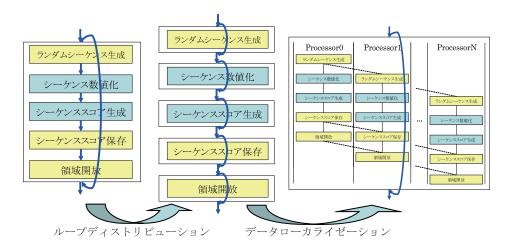

456.hmmer の全プログラム実行時間の 90%以上を占めるループは図 4.6 で示される構造となっている.逐次ループ内部にイタレーション間の依存がある部分とない部分が存在するため,並列処理を行うためにはループのリストラクチャリングが必要となる.OSCAR コンパイラによってループディストリビューションを行い,データローカライゼーション手法 [吉田 94] を適用した.このイメージを図 4.7に示す.

この例では,まず図 4.6 のループに対してスカラエキスパンションが適用される.このとき,図 4.6 のランダムシーケンス生成部とシーケンス数値化部の関数戻り値はポインタであり,これらに対してスカラエキスパンションを適用するとポインタの配列となる.これらのポインタ配列の各要素間にエイリアスがないことが解析され,ループディストリビューションが適用される.その後,粗粒度タスク並列化におけるデータローカライゼーション手法が適用され性能向上を得ている.

オリジナルコードに対しては図 4.6 のループ内部で,ヒープ領域に確保したバッファをイタレーションを超えて再利用しているため,ポインタ解析を利用しても並列性の抽出ができず,性能向上は得られなかった.

#### コアループ部切り出しコード

```

for (idx = 0; idx < nsample; idx++) {

/* ランダムシーケンス生成 */

seq = RandomSequence(...);

/* シーケンス数値化 */

dsq = DigitizeSequence(seq, ...);

/* シーケンススコア生成 */

score = P7Viterbi(dsq, ..);

/* シーケンススコア保存 */

AddToHistogram(score, ...);

if (score > max) max = score;

/* 領域開放 */

free(dsq);

free(seq);

}

/タレーション間依存あり:

```

イタレーション間依存あり: イタレーション間依存なし:

図 4.6: hmmer における主要処理ループ構造

IBM XL コンパイラ, Intel コンパイラによる自動並列化では, オリジナルコード, Parallelizable C コードともに性能向上は得られなかった.

#### MediaBench mpeg2encode

オリジナルコードでは,IBM p5 550Q で OSCAR コンパイラによる自動並列化により 4 コア使用時に 1.53 倍の性能向上が得られた.この性能向上は動き推定処理中の関数である frame\_estimation() が粗粒度タスク並列処理された結果である.コンパイラにより解析された並列度は 2.5 となっており,3 プロセッサが割り当てられ並列処理が行われた.そのため,4 コア使用時と 8 コア使用時では性能の差が見られなかった.

Parallelizable C コードでは OSCAR コンパイラの自動並列化により 8 コア使用時に 5.13 倍の性能向上が得られた.これは,プログラムの書き換えにより, OS-

図 4.7: hmmer における主要処理ループのデータローカライゼーション

CAR コンパイラによるマクロブロックレベルの並列性とデータローカリティの抽出 [小高 05] が可能となったためである .

IBM XL コンパイラ, Intel コンパイラによる自動並列化では, オリジナルコード, Parallelizable C コードともに性能向上は得られなかった.

## 4.7 関連研究

並列ソフトウェア開発のためのプログラミングモデルは大きな課題となっており,並列プログラミングを容易化するための並列プログラミング言語の提案や,逐次プログラムから自動的に並列化するための逐次プログラミングモデルの改良が提案されている.

新しい並列プログラミング言語としては,ストリーム処理に特化したStreamIt[TKA02] や,ロックを用いずに並列性を記述可能であり PGAS(Partitioned Global Address Space) メモリモデルをサポートする X10[CGS+05], 階層的なメモリを対象とした並列性とデータローカリティをプログラム可能な Sequoia[FHK+06], 並列処理タスクの宣言的な記述とそのタスク内部処理の命令的な記述を可能とする Molatomium[高山 10]

等が提案されている.このような新しい並列プログラミング言語の導入により,並列ソフトウェア開発の生産性が飛躍的に向上する可能性がある.しかしながら,新しいプログラミング言語の開発現場への導入には,プログラマの教育や既存の資産の移植が必要であり,導入障壁が高くなってしまっている.そこで本論文では,既存の逐次プログラミング言語の記述方法のガイドラインを設定することで自動並列化の適用を可能とし,効果的な並列処理と多様なアーキテクチャへの移植性を実現する.本研究では実際に自動並列化による高い性能を得ることを目的として,自動並列化フレームワークを構築し,性能評価を行った.