#### Waseda University Doctoral Dissertation

# Research on Combined Approaches of Graph Theory and Mathematical Programming for High-Level and Physical Synthesis of VLSI

### Cong HAO

Graduate School of Information, Production and Systems

Waseda University

July 2017

#### Abstract

Along with explosive VLSI applications in modern technologies, VLSI design using software tools becomes of the utmost importance, which is referred to as electronic design automation (EDA). EDA design flow, also called IC design flow, is a process which consists of several automated steps to accomplish the design of an IC. Since EDA tools play an important role in developing ICs with high performance, low cost and fast time-to-market, the development of high efficiency algorithms used in EDA design flow for various optimization objectives are attracting more and more research interests. The general EDA design flow contains several representative steps including high level synthesis (HLS), logic synthesis, and physical synthesis, etc., to meet various design requirements such as power, chip area, clock frequency and signal delay.

Since mid-1970s, the investigations of EDA design methodologies have been carried on for decades, and significance achievements have been made for automated designs instead of manual designs. Along with the development of commercial EDA tools, EDA companies are also growing fast and continuously, proposing latest design solutions. Apart from the achievements, there are still unsolved problems in the flow, either because of the hardness of the problem, or because of the rapidly growing problem size. For example in HLS, for the researches in low power scheduling and binding, the solution quality is still lower than manual designs, which has a large room for improvement; for the researches in interconnection optimization, some important problems such as the port assignment problem, are ignored and not being fully investigated, which is regretful since they do has a great affection on total power consumption. Therefore, algorithms with high optimality are still expected, which equal or even excel manual designs. In addition, in physical synthesis, one of the problems is, together with the growing design and circuit size, some problems, say the TSV assignment problem, become extremely huge, which makes it difficult to be solved using existing algorithms. Therefore, algorithms with high efficiency are expected to handle large scaled problems in physical synthesis.

Motivated by the existing issues, in this research, several problems in two main stages, are to be studied, including **high level synthesis** and **physical synthesis**, because most problems in high level synthesis and physical synthesis share similar problem formulations, say Integer Linear Programming (ILP) formulation or graph formulation. Given their similar properties, in this research, some combined approaches of **graph theory** and **mathematical programming**, is to be investigated and to be applied on HLS and physical synthesis to solve the above issues. In the HLS process, several major steps including scheduling, resource allocation and binding, and interconnection optimization are discussed. In physical synthesis for 3D IC, the TSV insertion problem for 3D-IC is mainly studied. They are studied by common technologies, including graph theory, mathematical programming and iterative methods say local search with random re-start, with the principle of improving the algorithm optimality and efficiency. This thesis is organized as the follows.

Chapter 1, [Introduction], first gives a brief introduction to EDA design flow, mainly including high level synthesis, logic synthesis and physical synthesis. Some existing problems in current EDA design flow are addressed, for example in high level synthesis, the optimality of existing algorithms is not high enough, and in physical synthesis the algorithm efficiency is low especially for large scaled problems. Motivated by the existing problems, the principles of this research are given, which are improving algorithm optimality for small and medium sized problems, as well as improving algorithm efficiency for large sized problems. Then, three major topics of this research are introduced, including: (1) the multiple supply/threshold voltage scheduling for dynamic/leakage power minimization, which corresponds to the scheduling step in HLS; (3) the interconnection optimization between functional units and registers, which corresponds to the interconnection allocation step in HLS; and (3) the through silicon via (TSV) insertion on 3D-ICs to reduce routing wire length, which corresponds to the floor plan and placement step in physical synthesis. Their common technologies are also briefly addressed. Finally, the background knowledge of HLS, 3D IC and TSV insertion problem are briefly addressed.

Chapter 2, [A Unified Scheduling Approach with Multiple  $V_{dd}$  or/and  $V_{th}$  in HLS], discusses the dynamic and leakage power minimization problem using multiple  $V_{dd}$  and  $V_{th}$  technology in operation scheduling. The combined scheduling and binding method is also discussed in this chapter. For this problem, the inputs are small or medium scaled, but the optimality of existing algorithms are still not high enough because of the hardness of this problem. Therefore, the purpose of this topic is to propose algorithms with high optimality, which equal or even excel the manual designs.

In this chapter, a unified scheduling approach which is applicable to various optimization problems is proposed, including: (1) dynamic power and resource usage co-optimization; (2) leakage power optimization; and (3) dynamic power and leakage power co-optimization. To deal with different objectives with high flexibility, three problems are divided into two common sub-problems including delay assignment and resource density variance minimization. Then a vertex potential based mobility allocation model is proposed to solve two sub-problems simultaneously. On the proposed mobility graph, the network simplex method is applied to solve the mobility allocation problem, which optimizes both dynamic power and resource usage by adjusting the vertex potentials. The mobility allocation is iteratively updated by local search until the algorithm meets stop criteria. The combined scheduling and binding for power minimization is also investigate, which conducts binding after scheduling only when the scheduling results are promising in reducing current overall power consumption.

Experimental results show that, for dynamic power and resource co-optimization, the proposed unified scheduling approach produces optimum solutions for all 6 benchmarks with 15 groups of data; for leakage power optimization, it also greatly excels the latest existing work, by 20% leakage power reduction and 52 times speedup. Besides, for dynamic power and leakage power co-optimization, the Pareto Solutions are studied.

Chapter 3, [Interconnection Allocation Between Functional Units and Registers in HLS], discusses the interconnection optimization techniques in HLS, which has not been fully investigated. Algorithms are proposed for the port assignment problem between functional units and registers. This problem is also small or medium scaled, but has a large impact on chip design, such as chip area, power

consumption and signal delay. Further, this problem may be solved iteratively in HLS tools, which requires high efficiency of the algorithms.

In this chapter, the port assignment problem for binary commutative operators for interconnection complexity reduction is discussed. First, the port assignment problem is formulated on a constraint graph. By constructing a spanning tree and extracting a conflict graph, a practical method is proposed to find a valid and initial solution. For solution optimization, an elementary spanning tree transformation based local search algorithm is proposed. To improve the efficiency of optimization, a matrix formulation is also proposed, and by substituting the  $\oplus$  for + operations in LP formulation, network simplex method is adopted, where pivoting operations are used to perform optimization. The pivoting properties and two-step successive pivotings are also discussed to further improve algorithm efficiency and optimality.

The experimental results show that on the randomly generated test cases, the matrix-based algorithm shows the highest solution optimality and is five times faster than the elementary transformation method. On the real high-level synthesis benchmarks, the matrix-based method reduces 14% interconnections, while the previous greedy algorithm reduces 8% on average, which implies that interconnection reduction has a large impact on chip performance.

Chapter 4, [A Multi-Level Algorithm for 3D-IC TSV Assignment in Physical Synthesis], discusses the problem of Through Silicon Via (TSV) insertion on 3D-ICs in physical synthesis. The problems in this stage are generally large scaled, which lack of efficient algorithms. For example, for large scaled inputs, the execution time of current algorithms may exceed ours or days. Therefore in this topic, the purpose is to propose algorithms with high efficiency, and meanwhile the solution quality is not sacrificed.

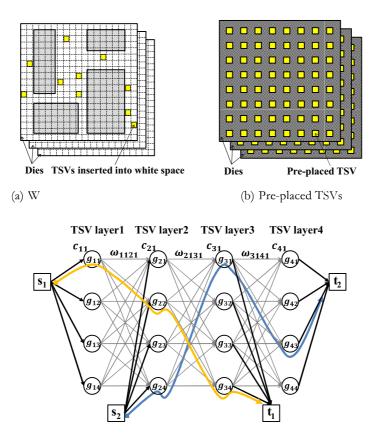

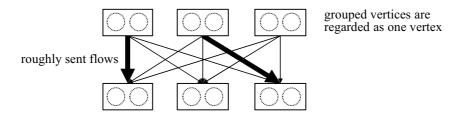

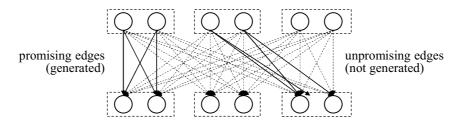

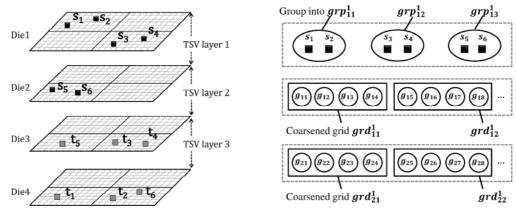

Through-silicon via (TSV) assignment problem is one of the key design challenges of 3D-ICs, which is crucial to the wire length and signal delay. In this chapter the TSV assignment problem is formulated as an Integer Minimum Cost Multi Commodity (IMCMC) problem on a IMCMC network. To reduce the huge number of edges of the IMCMC network, a multi-level algorithm is proposed. It first coarsens the IMCMC network level by level, applies a rough flow assignment on each level of coarsened graph, and then generates only promising edges to reduce the IMCMC network size. Benefiting from the multi-level structure, a mixed single and multi commodity flow method is proposed to improve the TSV assignment solution quality. Besides, given a TSV assignment, an extended layer by layer algorithm is proposed to further optimize the TSV assignment.

The experimental results show that the proposed multi-level proposal achieves 37X speedup compared to the previous work, and meanwhile reduces the total wire length by 7.0%, which shows both high optimality and high efficiency. The extended layer by layer optimization further reduces 0.6% total wire length.

Chapter 5, [**Conclusions**], summaries this thesis and addresses some open issues of this research. Some future works are also addressed.

### Contents

| Al | bstrac | t                                                                        | i          |

|----|--------|--------------------------------------------------------------------------|------------|

| Li | sting  | of figures                                                               | viii       |

| Li | sting  | of tables                                                                | X          |

| 1  | Intr   | oduction                                                                 | 1          |

|    | 1.1    | Background                                                               | 1          |

|    |        | 1.1.1 EDA Design Flow                                                    | 1          |

|    |        | 1.1.2 Research Status                                                    | 3          |

|    | 1.2    | Research Motivations and Principles                                      | 4          |

|    |        | 1.2.1 Research Principle                                                 | 6          |

|    | 1.3    | Research Contents and Common Technologies                                | 7          |

|    |        | 1.3.1 Dynamic and leakage power minimization <sup>3</sup>                | 7          |

|    |        | 1.3.2 Interconnection allocation between FUs and registers 35            | 7          |

|    |        | 1.3.3 Through silicon via (TSV) insertion for 3D-IC <sup>71</sup>        | 8          |

|    | 1.4    | Preliminaries of High Level Synthesis                                    | 9          |

|    |        | 1.4.1 Necessity of High Level Synthesis                                  | 9          |

|    |        | 1.4.2 Necessity of Low Power High Level Synthesis (HLS)                  | 10         |

|    |        | 1.4.3 Related Low Power HLS Works                                        | 10         |

|    | 1.5    | Preliminaries of 3D-IC and Through Silicon Via Insertion                 | 12         |

|    | 1.6    | Thesis Organization                                                      | 13         |

| 2  | ΑU     | nified Scheduling Approach with Multiple $V_{dd}$ or/and $V_{th}$ in HLS | 15         |

|    | 2.1    | Background and Contributions                                             | 15         |

|    | 2.2    | Problem Formulations                                                     | 17         |

|    |        | 2.2.1 Problem Description                                                | 17         |

|    |        | 2.2.2 Unified ILP Formulation                                            | 19         |

|    | 2.3    | Preliminaries and Motivations                                            | 20         |

|    |        | 2.3.1 Two Common Sub-problems                                            | 21         |

|    |        | 2.3.2 Mobility and Mobility Overlap                                      | 22         |

|    |        | 2.3.3 Motivations for Mobility Graph and Mobility Allocation             | 22         |

|    |        | 2.3.4 Motivations for Vertex Potential                                   | 23         |

|    | 2.4    | Operation Delay Assignment                                               | 24         |

|    |        | 2.4.1 Linear Programming (LP) Relaxation From ILP                        | 25         |

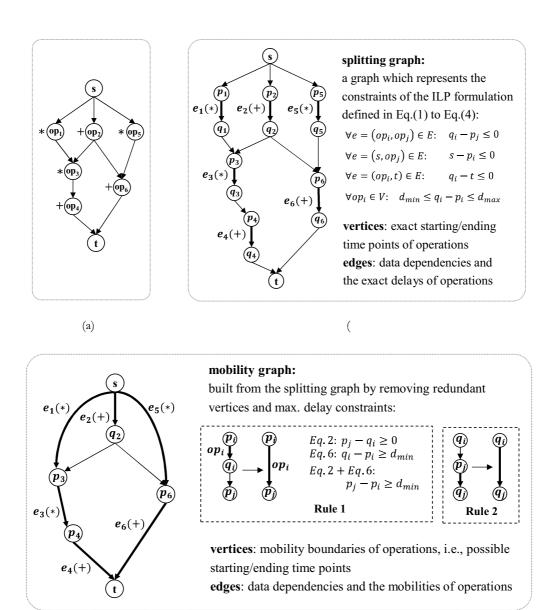

|    |        | 2.4.2 Splitting Graph                                                    | 25         |

|    |        | 2.4.3 Mobility Graph                                                     | 25         |

|    |        | 2.4.4 Vertex Potential and Mobility Allocation                           | 28         |

|    |        | 2.4.5 Delay Assignment                                                   | 29         |

|    |        | 2.4.6 Mobility Allocation Problem                                        | 30         |

|    | 2.5    | Resource Density Variance Minimization                                   | <b>3</b> 0 |

|    |        | 2.5.1 Resource Density                                                   | 30         |

|       | 2.5.2   | Objective Linearizing Using Target Vertex Potential             | 31       |

|-------|---------|-----------------------------------------------------------------|----------|

| 2.6   | Piece   | wise-Linear Extended Network Simplex Method                     | 32       |

|       | 2.6.1   | Outline of PLNSM                                                | 32       |

|       | 2.6.2   | PLNSM Based Mobility Allocation                                 | 33       |

|       | 2.6.3   | PLNSM based Extended Mobility Allocation                        | 35       |

|       | 2.6.4   | Analysis of PLNSM                                               | 35       |

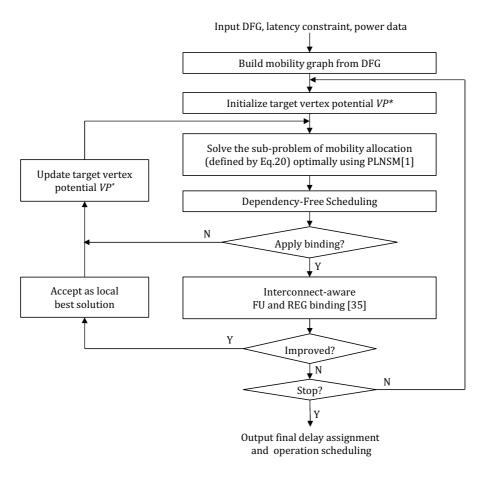

| 2.7   |         | osed Unified Scheduling Scheme                                  | 36       |

|       | 2.7.1   | Overview of Unified Scheduling Scheme                           | 37       |

|       | 2.7.2   | Dependency-Free Scheduling                                      | 37       |

|       | 2.7.3   | Functional Unit and Register Binding                            | 38       |

| 2.8   |         | rithm Utilization on Three Problems                             | 39       |

|       | 2.8.1   | Problem 1: Dynamic Power and Resource Co-Optimization           | 39       |

|       | 2.8.2   | Problem 2: Leakage Power Minimization                           | 39       |

|       | 2.8.3   | Problem 3: Dynamic and Leakage Power Co-Optimization            | 42       |

| 2.9   |         | rimental Results                                                | 43       |

| 2.7   | 2.9.1   | Dynamic Power and Resource Usage Co-Optimization                | 43       |

|       | 2.9.2   | Leakage Power Minimization                                      | 44       |

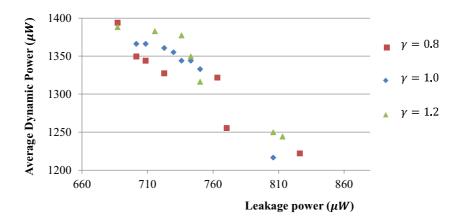

|       | 2.9.3   | Dynamic Power and Leakage Power Co-Optimization                 | 45       |

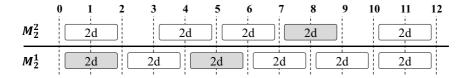

|       |         | Interconnection-Aware FU and Register Binding                   | 47       |

| 2.1   |         | nary                                                            | 48       |

| ۷.1   | o sum   | пату                                                            | 40       |

| 3 Int | erconne | ection Allocation Between Functional Units and Registers in HLS | 49       |

| 3.1   |         | ground and Contributions                                        | 49       |

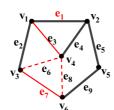

| 3.2   | _       | em Formulation                                                  | 51       |

|       | 3.2.1   |                                                                 | 52       |

|       | 3.2.2   | ILP Formulation                                                 | 53       |

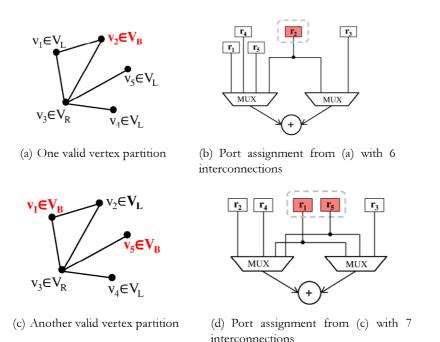

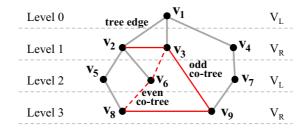

| 3.3   | Confl   | lict Graph Based Initial Solution Generation                    | 54       |

|       | 3.3.1   | Initial Vertex Partition on the Spanning Tree                   | 54       |

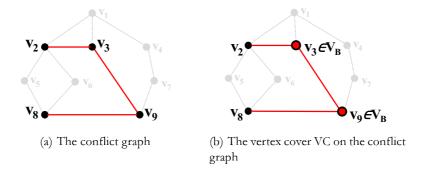

|       | 3.3.2   | Solution Legalization: Vertex Cover on Conflict Graph           | 55       |

| 3.4   | Elem    | entary Tree Transformation Based Solution Optimization          | 57       |

|       | 3.4.1   | Solution Optimization                                           | 57       |

|       | 3.4.2   | Elementary Tree Transformation                                  | 57       |

|       | 3.4.3   | Local Search Based Optimization Algorithm                       | 58       |

|       | 3.4.4   | Critical Path Optimization                                      | 59       |

| 3.5   |         | lex Method Based Solution Optimization                          | 59       |

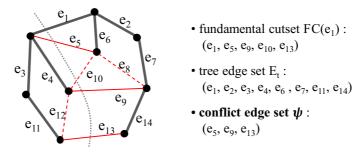

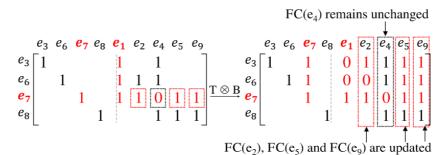

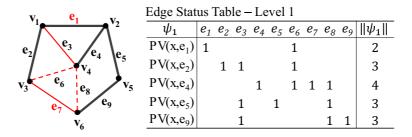

|       | 3.5.1   | Preliminaries and Mathematic Formulation                        | 60       |

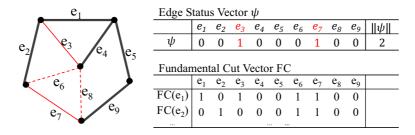

|       | 3.5.2   | Matrix Formulation                                              | 61       |

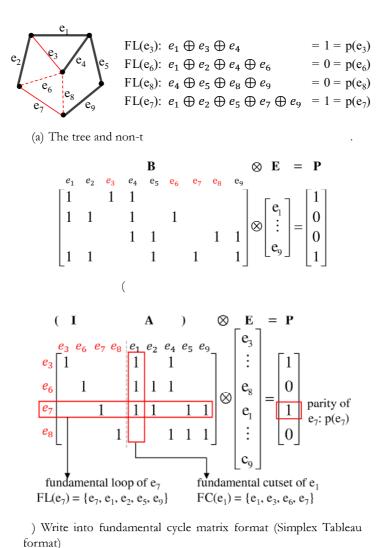

|       | 3.5.3   | Simplex Tableau Format                                          | 63       |

|       | 3.5.4   | Pivoting                                                        | 65       |

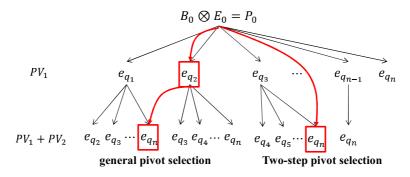

|       | 3.5.5   | Pivot Selection                                                 | 66       |

|       | 3.5.6   | Successive Pivotings                                            | 67       |

|       | 3.5.7   | A Two-Step Pivot Selection                                      | 70       |

|       | 3.5.8   | Multi-Step Pivotings                                            | 71       |

| 3.6   |         | rimental Results                                                | 71       |

| 5.0   | 3.6.1   | Optimality and Runtime Test on Random Constraint Graph          | 74       |

|       | 3.6.2   | Optimality and Runtime Test on DFGs                             | 74<br>74 |

|       | 3.6.3   | Power, Area and Delay Evaluation                                | 76       |

|       | 5.0.5   | Tower, Arica and Delay Evaluation                               | 70       |

|   | 3.7  | Summary                                                              | / / |

|---|------|----------------------------------------------------------------------|-----|

| 4 | ΑN   | Aulti-Level Algorithm for 3D-IC TSV Assignment in Physical Synthesis | 79  |

|   | 4.1  | Introduction                                                         | 79  |

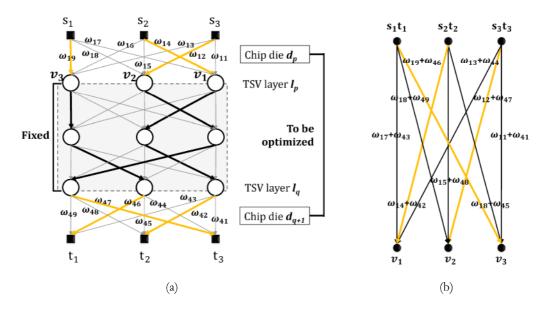

|   | 4.2  | Problem Formulation                                                  | 81  |

|   |      | 4.2.1 Problem Description                                            | 81  |

|   |      | 4.2.2 IMCMC Network Formulation                                      | 82  |

|   | 4.3  | Previous Issues and Motivations                                      | 83  |

|   | 4.4  | Multi-Level TSV Assignment                                           | 84  |

|   |      | 4.4.1 Grid Coarsening and Source Grouping                            | 84  |

|   |      | 4.4.2 Rough Flow Assignment and Graph Un-coarsening                  | 85  |

|   | 4.5  | Rough Flow Assignment: Mixed Single and Multi Commodity Flow         | 87  |

|   |      | 4.5.1 Mixed Single and Multi Commodity Flow Algorithm                | 88  |

|   | 4.6  | Extended Layer by Layer TSV Assignment Optimization                  | 91  |

|   | 4.7  | Experimental Results                                                 | 93  |

|   | 4.8  | Summary                                                              | 96  |

| 5 | Cor  | nclusions and Future Work                                            | 97  |

|   | 5.1  | Conclusions                                                          | 97  |

|   | 5.2  | Open Issues and Future Work                                          | 98  |

| A | ppen | dix A Publication List                                               | 109 |

# Listing of figures

| 1.1        | A traditional EDA design flow                                                                                                                                                                                                                                         | 2  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2        | Power saving opportunity and effort at different levels of abstraction from 5                                                                                                                                                                                         | 4  |

| 1.3        | research contents                                                                                                                                                                                                                                                     | 5  |

| 1.4        | Common Technologies: graph theory, mathematical programming and iterative methods                                                                                                                                                                                     | 8  |

| 1.5        | Basic concept of High Level Synthesis.                                                                                                                                                                                                                                | 9  |

| 1.6        | An example of 3D-IC and Through Silicon Vias (TSV)                                                                                                                                                                                                                    | 12 |

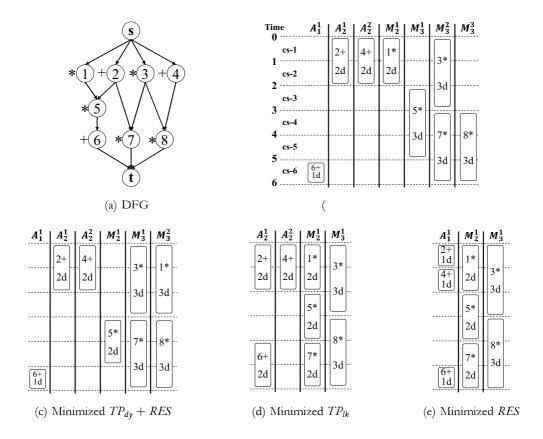

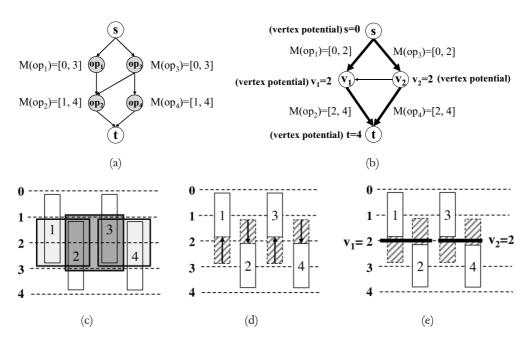

| 2.1        | Different scheduling and delay assignment results for: (b) dynamic power minimization, (c) dynamic power and resource usage co-optimization, (d) leakage power minimization, and (e) resource minimization only. In the figures 1d means the delay of operation is 1, |    |

|            | etc; cs-1 means control step 1, etc                                                                                                                                                                                                                                   | 20 |

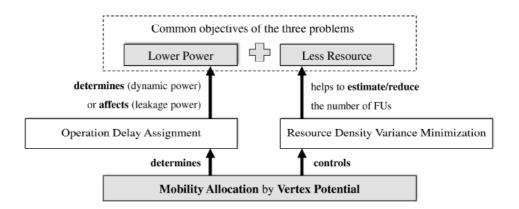

| 2.2        | Three problems share two common sub-problems: delay assignment and resource density variance minimization. Mobility allocation by vertex potential is proposed to optimize the two problems simultaneously.                                                           | 21 |

| 2.3        | Motivations for mobility graph and vertex potential. (a) In previous works mobilities are defined on vertices. (                                                                                                                                                      |    |

|            | . (d) Mobility overlap removal in <sup>23</sup> . (e) Overlap-free mobility allocation in this                                                                                                                                                                        |    |

|            | proposal                                                                                                                                                                                                                                                              | 23 |

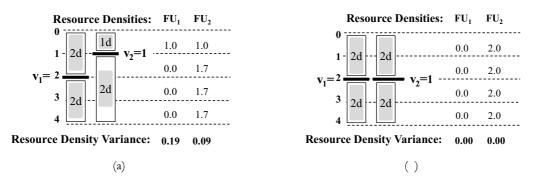

| 2.4        | Vertex potentials determine both delay assignment and resource density — the common control variable for power and resource optimization. (a) One $FU_{\rm I}$ (1-delay) and two                                                                                      |    |

|            | $FU_2$ (2-delay) are needed. (b) Only two $FU_2$ are needed                                                                                                                                                                                                           | 24 |

| 2.5        | (a) DFG. (b) The splitting graph built from (a). (c) The mobility graph built from (b)                                                                                                                                                                                |    |

|            | by redundant vertex removal under two rules                                                                                                                                                                                                                           | 26 |

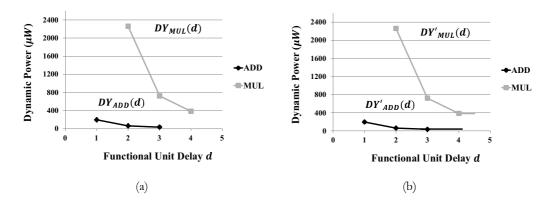

| 2.6<br>2.7 | <ul><li>(a) Original cost functions for MUL and ADD. (b) Extended cost functions</li><li>(a) The mobility graph with vertex potentials. (</li></ul>                                                                                                                   | 27 |

|            |                                                                                                                                                                                                                                                                       | 29 |

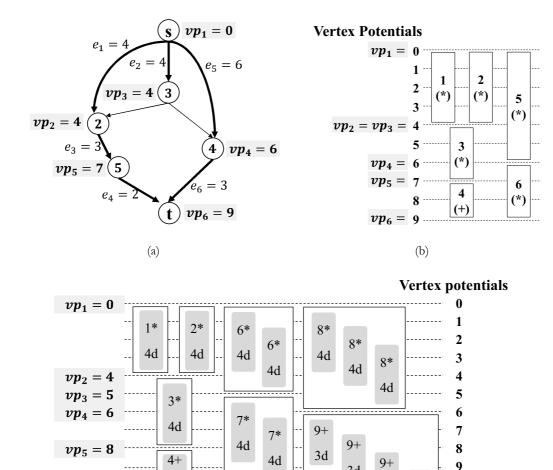

| 2.8        | Example of PLNSM on mobility graph                                                                                                                                                                                                                                    | 34 |

| 2.9        | Example of PLNSM with target vertex potential                                                                                                                                                                                                                         | 35 |

| 2.10       | Flow-chart of the unified scheduling approach                                                                                                                                                                                                                         | 36 |

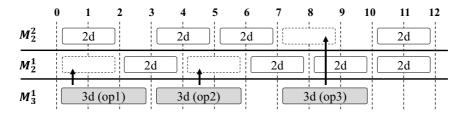

|            | Example of post processing for leakage power minimization                                                                                                                                                                                                             | 42 |

| 2.12       | Dynamic power and leakage power solution space                                                                                                                                                                                                                        | 45 |

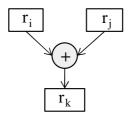

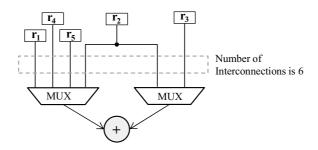

| 3.1        | An example of a binary commutative functional unit with the interconnection allocation                                                                                                                                                                                |    |

|            | between the registers and MUXes                                                                                                                                                                                                                                       | 52 |

| 3.2        | The examples of vertex partitions and the corresponding port assignment solutions                                                                                                                                                                                     | 54 |

| 3.3        | Example of tree edges, odd non-tree edges and even non-tree edges                                                                                                                                                                                                     | 55 |

| 3.4        | The example of initial vertex partition legalization                                                                                                                                                                                                                  | 55 |

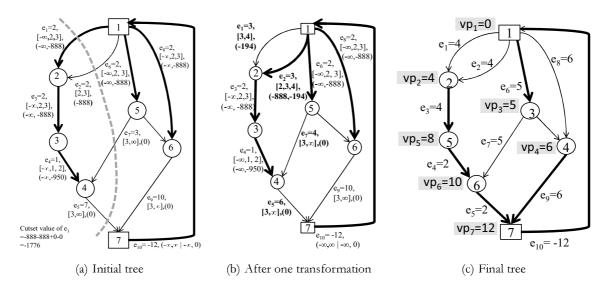

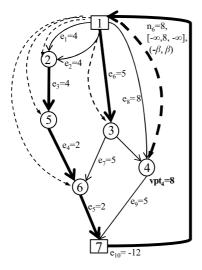

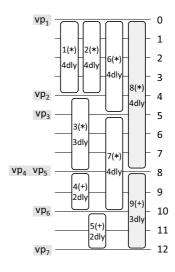

| 3.5        | Example of fundamental cutset FC, tree edge set $E_t$ and conflict edge set $\psi$                                                                                                                                                                                    | 57 |

| 3.6        | Examples of fundamental cut vector $FC$ and edge status vector $\psi$                                                                                                                                                                                                 | 60 |

| 3.7        | The example of mathematic formulation and its matrix formulation                                                                                                                                                                                                      | 62 |

| 3.8        | Example of the pivoting using pivoting matrix $T$                                                                                                                                                                                                                     | 64 |

| 3.9        | The example of the pivoting using pivoting matrix $T$                                                                                                                                                                                                                 | 64 |

| 3.10       | Pivot selection using an edge status table                                                                                                                                                                                                                            | 67 |

| 3.11 | Examples of redundant successive pivotings                                                             | 67 |

|------|--------------------------------------------------------------------------------------------------------|----|

| 3.12 | Example of the edge status table of level 2                                                            | 68 |

|      | The two-step pivot selection                                                                           | 70 |

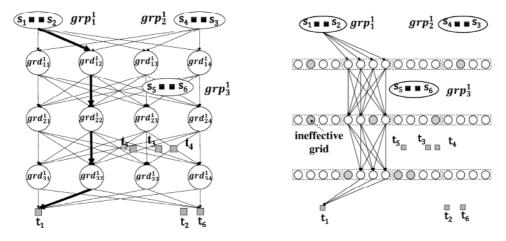

|      | Both kinds of TSV assignment problems can be formulated as an integer min-cost multi-                  |    |

|      | commodity (IMCMC) problem.                                                                             | 81 |

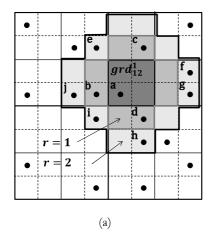

| 4.2  | Main idea of the proposed multi-level algorithm.                                                       | 84 |

| 4.3  | Grids are clustered into coarsened grids, and source pins are grouped according to their               |    |

|      | locations on chip dies                                                                                 | 86 |

| 4.4  | Rough flow assignment and graph un-coarsening                                                          | 86 |

| 4.5  | (a) Grid extension on graph of level ε. (                                                              |    |

|      |                                                                                                        | 87 |

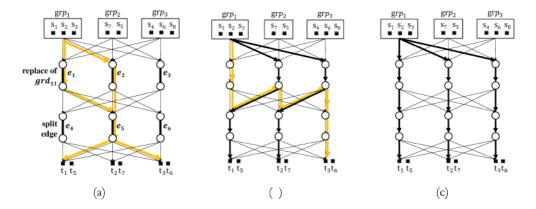

| 4.6  | (a) Grid vertices are replaced by edges; costs are grid capacities. Flows from a same                  |    |

|      | source group are undistinguished. (b) Assign a net of $grp_{_{\rm I}}$ through the residual edges.     |    |

|      | (c) Flows of $grp_1$ are updated                                                                       | 88 |

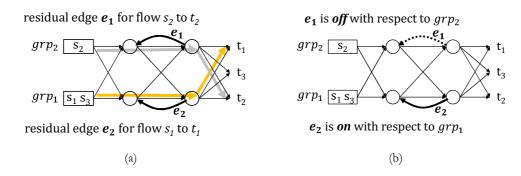

| 4.7  | Edge status of on and off with respect to source groups. (a) Flows sent for $(s_i, t_i)$ and           |    |

|      | $(s_2, t_2)$ . (b) Residual network with respect to $grp_1$ when sending flow for $(s_3, t_3)$ , whose |    |

|      | source belongs to $grp_{_{\rm I}}$                                                                     | 89 |

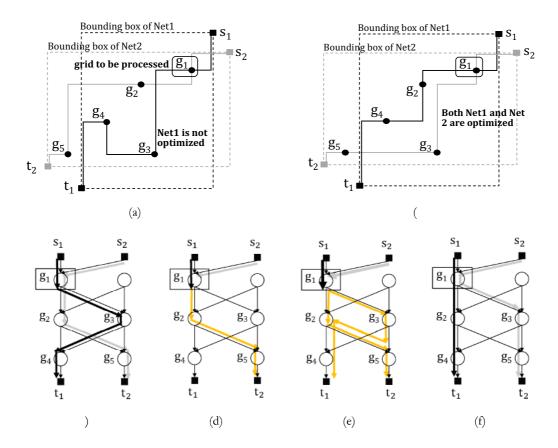

| 4.8  | The example of single flow algorithm applied on grids. (a) Before processing $g_t$ , Net1              |    |

|      | is not optimized. (b) After processing $g_i$ , both Net1 and Net2 are optimized. (c) Initial           |    |

|      | flow assignment. (d) A shortest path from $g_1$ to $t_2$ . (e) An augmenting path from $g_1$ to $t_1$  |    |

|      | going through a residual edge. (f) Updated flow assignments from (c).                                  | 91 |

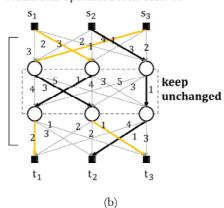

| 4.9  | (a) Traditional layer by layer optimization with total cost of 19. (b) Extended layer by               |    |

|      | layer optimization with total cost of 16                                                               | 92 |

| 4.10 | (a) Extended layer by layer to optimize the TSV assignments of two non-adjacent dies.                  |    |

|      | cost matching                                                                                          | 93 |

# Listing of tables

| 2.1 | Dynamic Power-Delay Table for ADD and MUL under clock frequency of 769MHz (clock                          |    |

|-----|-----------------------------------------------------------------------------------------------------------|----|

|     | period 1.3ns)                                                                                             | 18 |

| 2.2 | Leakage Power-Delay Table for ADD and MUL under clock frequency of 769M (clock period                     |    |

|     | 1.3ns)                                                                                                    | 18 |

| 2.3 | Scheduling Algorithm Utilizations on Three Problems                                                       | 39 |

| 2.4 | Leakage power minimization without and with resource concern                                              | 41 |

| 2.5 | Comparisons between this scheduling approach and ILP solution                                             | 44 |

| 2.6 | Comparisons between my scheduling approach and existing work 23 for leakage power                         |    |

|     | minimization only                                                                                         | 46 |

| 2.7 | Scheduling combined with FU and register binding for leakage power minimization                           | 47 |

| 3.1 | Information of Test Benches                                                                               | 71 |

| 3.2 | Area, power and delay of multiplexers from 63.                                                            | 72 |

| 3.3 | comparison between elementary tree transformation based and matrix transformation based                   |    |

|     | optimization methods                                                                                      | 72 |

| 3.4 | port assignment on high level synthesis testbenches                                                       | 73 |

| 3.5 | Estimated area, power and critical path delay of all MUXes                                                | 73 |

| 3.6 | Implementation of testbench FFT on FPGA platform under 50MHz clock frequency                              | 76 |

| 4.1 | Edge reduction and algorithm speedup by the multi-level proposal                                          | 93 |

| 4.2 | Comparisons between work <sup>76</sup> and the multi-level proposal with/without penalty                  |    |

|     | function, and with/without min-cost flow on grid vertices                                                 | 94 |

| 4.3 | Evaluation of the traditional layer by layer <sup>77</sup> and the extended layer by layer optimizations. | 95 |

|     |                                                                                                           |    |

## Acknowledgments

I wish to express my sincere appreciation to those who have contributed to this thesis and supported me in one way or the other during this amazing three years.

First of all, I am extremely grateful to my main supervisor, Professor Takeshi Yoshimura. Pursuing a doctoral degree is a hard and long journey, which I obviously cannot finish without the help of my professor. On academic topics, he gives me all his support, showing his guidance and all the useful discussions and suggestions anytime I ask for. His deep insights helped me at various stages of my research. More importantly, he is teaching me how to think, how to learn, and how to be more excellent, and continuously encouraging me to be a better person. In daily life, my professor also gives me as much help as he could, which is the strongest support for my study and life in Japan. I feel so grateful that I could be one of the students of professor Yoshimura, which I believe is the luckiest thing that could ever happen on me in the world.

Secondly, I would like to express my sincere thanks to Professor Watanabe and Professor Kimura, w

I also want to express my thanks to all my lab members, Nan Wang, Delong Li, Nan Ding, Hui Zhu, Huanji Sun, Wencan Zhang, Jiayao Wu, Jiayi Ma, and so many friends I did not list here. It is all of you who made my life in Japan gorgeous.

Then, I want to show my deep love to a special association, the Judo circle of the University of Kitakyushu and the Hibikino Judo Club, which opens a totally new world to me and has greatly changed my life. Our couches, Mr. Takenouchi and Mr. Tomohiro, as well as all the members in this club, are always the ones who provide me power, energy and vigour, and are the sources of my fighting will. I love them as teachers, as friends and as families.

Finally, I conserve my deepest thanks to my families. It was their love and encouragement that supported me to finish my doctoral degree and to pursue dreams in the future.

# 1 Introduction

Very Large Scale integration (VLSI) first appeared in the 1970s, and then quickly began to show evolutional improvements over discrete circuits mainly on cost and performance, and are becoming one of the most indispensable components of the modern technology. Accordingly, designing and developing various functional VLSI, especially by software tools because of the high complexity of modern circuits, are also become of the utmost importance, which is referred to as electronic design automation (EDA), also as electronic computed aided design (ECAD).

Sprouted by the mid-1970s, the EDA industry is going through a rapid growth during the past decades, and is still attracting more and more exploring interests in nowadays. Given the pressing demands for faster and stronger EDA tools especially along with the continuous scaling of semiconductor technology, in this work, main efforts are put in the design field of EDA tools, in order to improve the efficiency and performance of particular methods in the EDA design flow.

In the following parts of this chapter, first, a brief introduction to EDA design flow is given in Section 1.1, as well as some existing problems in current EDA design flow. and in Section 1.2, the motivations and principles of this research are addressed. In Section 1.3, the main contents and common technologies of this research are briefly introduced. Finally in Section 1.6 the organization of this thesis is given.

#### 1.1 Background

#### 1.1.1 EDA Design Flow

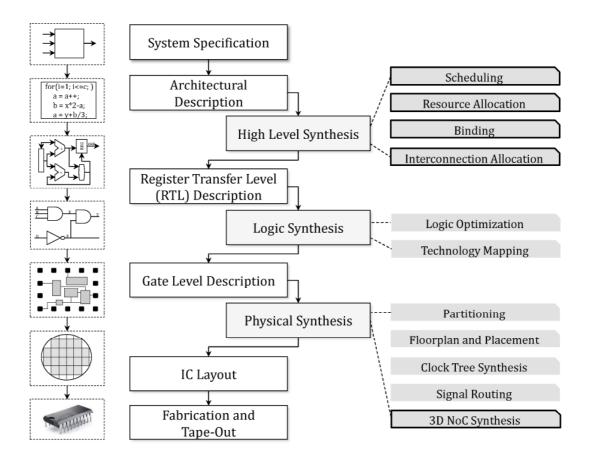

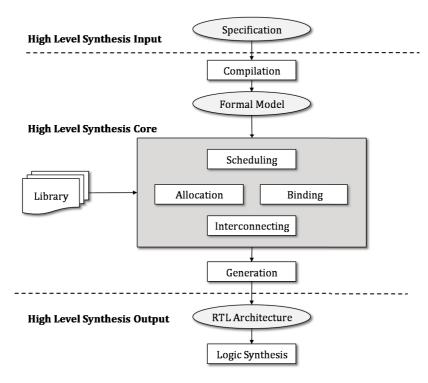

EDA design flow is a process which consists of several automated steps to accomplish the design of a VLSI circuit. The general EDA design flow contains several representative steps, as shown in Fig.1.1, including:

1. High-Level Synthesis (HLS) (or behavioural synthesis) — takes architectural design as an input, transforms architectural design descriptions (eg. designs written in C/C++) into register transfer

Figure 1.1: A traditional EDA design flow.

level (RTL) descriptions, which is referred to as functional design or logic design;

- 2. Logic Synthesis takes the logic design as an input, transforms the RTL description (eg. designs written in Verilog or VHLD) into a netlist of logic gates, which is called circuit design;

- 3. Physical Synthesis takes the circuit design as an input, transforms the gate-level circuits into geometric representations with exactly determined locations for circuit components, which are ready for layout;

- 4. Verification, fabrication and finally Tape-out last steps in EDA design flow before a chip is manufactured and into market.

During the EDA design flow, up to dozens of design requirements are needed to be considered, such as chip area, power, thermal, routability, signal timing, delay, noise, reliability, etc., which makes it extremely difficult to meet all or a critical part of the requirements while keeping the design cost low and time-to-market fast. Therefore, the development of high efficiency algorithms used in EDA design steps for various optimization objectives are continuously attracting both industrial and academical research interests.

#### 1.1.2 Research Status

The investigations of EDA design methodologies have been carried on for decades since mid-1970s, and significance achievements have been made for automated designs instead of manual designs. Along with the developments of commercial EDA tools, EDA companies are also growing fast and continuously proposing latest design solutions. Following shows a brief review of the current worldwide research situation.

1. **High Level Synthesis:** HLS is one important technology to deal with rapid growing VLSI integration by raising the abstraction level of system descriptions. In recent years, along with the growth of portable and battery-equipped devices, reducing power has became the first-priority design factor. Therefore, the **low power HLS** has became the new hottest topic in HLS.

Consequently, more and more works are focusing on low power HLS technologies, for example the multiple supply voltage or multiple threshold voltage technology for power reduction, power reduction through interconnection optimization, clock gating and power gating, and dynamic power and frequency scaling, etc. Among them, the proposals for multiple supply or threshold voltage technology, like 10 13 14 and 78 23, shows significance achievements in reducing power consumption in the scheduling and binding step of HLS. Besides, works like 43 32 55 try to reduce power by reducing the interconnection complexity, mainly in the interconnection allocation step of HLS.

**Existing issues:** Although there are plenty works have been proposed for low power HLS, they are still far from mature. For the researches in low power scheduling and binding, the solution quality is still lower than manual designs, which is expected to be greatly improved; for the researches in interconnection optimization, some important problems such as the port assignment problem, are ignored and not being fully investigated, which is regretful since they do has a great affection on total power consumption.

2. **Logic Synthesis:** Logical synthesis has a much longer history than HLS, which makes its solutions far more mature than HLS. Also, there are a plenty of commercial logic synthesis tools such as the Design Compiler by Synopsys, Encounter RTL Compiler by Cadence Design Systems, HDL Designer by Mentor Graphics, Quartus II integrated Synthesis by Altera, XST (delivered within ISE) by Xilinx, etc. There are also open source tools like the Logic Synthesis Tool (SIS)<sup>47</sup>. In academic researches, there are several major topics including combinational and sequential logic synthesis, synthesis for asynchronous circuits, synthesis for elastic circuits, automatic pipelining, etc<sup>46</sup>.

**Existing issues:** As pointed out in <sup>46</sup>, equivalence checking problem still exists in the transformations that modify timing beyond the natural boundaries of RTL state signals. Besides, the automation for out-of-order execution is also pointed out as another challenge.

3. **Physical Synthesis:** Similar to logic synthesis, physical synthesis also has a long history with several mature commercial tools. such as the RTL Compiler/Build Gates/Physically Knowledgeable Synthesis (PKS) by Cadence, and the Design Compiler by Synopsys. Therefore, the solution quality is satisfied for traditional synthesis, such as partitioning,

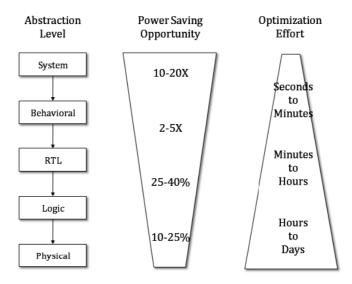

Figure 1.2: Power saving opportunity and effort at different levels of abstraction from <sup>5</sup>

floorplan and placement, clock tree synthesis and routing. On the other hand, along with the development of 3D ICs, the physical synthesis for 3D IC, or 3D Network-on-Chip (NoC), has became a new topic in the physical synthesis.

In the physical synthesis for 3D IC, one important topic is the Through Silicon Via (TSV) insertion (also called the TSV assignment problem), because the TSVs are very large compared to logic gates, say dozens to hundreds of times the area of a standard cell, and the TSV assignment is crucial to the wire length and signal delays of 3-D circuits. In the related works of TSV assignment, some works handle TSV insertion as an independent problem, whose optimization objectives include: total wire length, chip thermal, interconnection complexity, etc. Some other works perform TSV insertion together with floorplan or placement, where TSVs are pre-planned during floorplan or placement, and are once more optimized after the floorplan or placement is finished. These works imply that a careful TSV assignment can greatly reduce total wire length, chip area or improve thermal issues.

**Existing issues:** One of the problems in TSV assignment is, together with the growing design and circuit size, the TSV assignment problem size is also becoming huge, which makes it difficult to be solved using existing algorithms. For example in the work <sup>76</sup>, since the problem formulation is extremely huge, the authors proposed several methods to reduce the formulation size by scarifying the solution optimality. Another work <sup>77</sup> proposed a Lagrangian based algorithm but it cannot be applied on large testcases.

#### 1.2 Research Motivations and Principles

Motivated by the existing issues in EDA design flow, in this research, several problems in two parts are to be studied. One is the **low power HLS** technology, including the scheduling, resource allocation and binding, and interconnection optimization. Another is the **physical synthesis for 3D IC** technology,

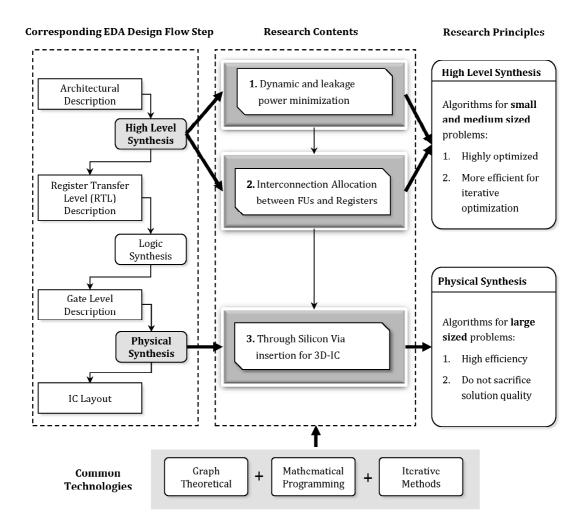

Figure 1.3: research contents

- 1. Both low power HLS and physical synthesis for 3D IC technologies are of great importance with worth deep investigation. As pointed out in 5, attempting to reduce power at RT level typically requires much more efforts than at behaviourial or system level, and as shown in Fig.1.2, the higher abstraction level is, the less optimization effort is needed, and the higher power saving opportunity is. Therefore exploration for low power HLS is a promising topic both now and in the future. On the other hand, physical synthesis for 3D IC is an indispensable step for impelling real applications of 3D IC chips in industry, which is a promising solution for higher and higher IC integration.

- 2. There are open issues for low power HLS and physical synthesis for 3D IC to be solved, as pointed out in Section 1.1.2. In HLS, it is still difficult for the automated design algorithms to produce optimal solutions better than manual designs for even small or medium sized HLS problems. Therefore, **more optimized algorithms in HLS are required.** In physical synthesis, along with the design size growing, it is difficult for the current existing algorithms to handle huge sized problems. Therefore, **more efficient algorithms for huge sized problems are required.**

Essentially, these open issues for low power HLS and physical synthesis for 3D IC are essentially the same, which is to propose **high efficiency** algorithms. In order to improve the algorithm optimality, one important and effective way is to use iterative optimization: assume the possibility to get optimum solutions in one iteration is  $p(o \le p \le 1)$ , if the algorithm is executed for n iterations with random restart, the possibility to get optimum solutions is  $p^* = 1 - (1 - p)^n$ . Obviously the larger n is, the closer  $p^*$  is to 1. This requires in each iteration, the algorithm must be efficient enough to produce solutions fast. Therefore, fast and highly optimized algorithms are still expected.

3. Moreover, the problems for both low power HLS and physical synthesis for 3D IC share similar formulations, which allows similar methodologies to be adopted. To be specific, all these problems can be formulated by Integer Linear Programming (ILP), one of the methods in **mathematical programming**, and written into  $A \cdot x = B$  where x are integers. In these problems, matrix A happens to be the incidence matrix of a graph. Therefore, if the constraints that x are integers can be relaxed (for example if A is totally unimodular), the ILP formulations can be transformed into Linear Programming (LP), and therefore **graph theories** can be considered. Besides, since one of the purposes is to improve optimality, **iterative methods** are also expected. Consequently, **common technologies** can be applied to these problems, to improve the efficiency and optimality of their solutions.

#### 1.2.1 Research Principle

Therefore, the principle of this research is stated as the following:

By utilizing **graph theory** and **mathematical programming** methods, which are widely used methodologies in EDA design area,

- 1. For small and medium sized problems in HLS, say the scheduling and binding problems, algorithms that produce solutions as optimal as possible (optimal or sub-optimal), which excel manual designs, are to be proposed. For this purpose, since iterative optimizations are expected to improve solution quality, algorithms also expected to be efficient for one iteration.

- 2. For huge sized problems in physical synthesis of 3D-IC which are impossible for manual design or with no existing practical solutions, for example in floorplan and placement step in physical synthesis, algorithms which are efficient enough to produce solutions in reasonable time with no or slight optimality degrade are to be proposed.

#### 1.3 Research Contents and Common Technologies

In this section, the principles of this research, as well as main contents, common key technologies and contributions are introduced. Fig.1.3 gives an overview of the organization of this research. There are three parts in this research, corresponding to particular design steps in EDA design flow. The first two parts are the works in HLS, and the third part is the work in physical synthesis. The three works share common key technologies including **graph theory**, **mathematical programming** and **iterative optimization**, as shown in the right part of Fig.1.3.

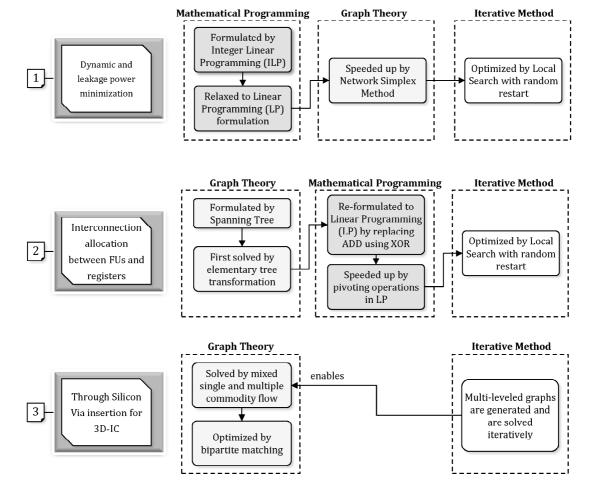

In the following, three works are briefly introduced respectively, as well as their common and specified core technologies shown in Fig.1.4.

#### 1.3.1 Dynamic and leakage power minimization<sup>3</sup>

The dynamic and leakage power minimization under multi- $V_{dd}$  or/and multi- $V_{th}$  corresponds to the highest step, operation scheduling in HLS procedure. It solves the problem that, how to determine the schedule and the supply/threshold voltage for each operation, to reduce the overall dynamic/leakage power consumed by functional units. The goal is to propose a new algorithm, which can excel previous works in both efficiency and solution optimality. Besides, the combined scheduling and binding for power minimization is also discussed.

**Technologies:** it is first given mathematical formulation, the integer linear programming (ILP), and then is relaxed to linear programming (LP) formulation. Although general linear programming methods can solve this problem, given the special properties of its constraint graph, the network simplex method, one of the graph theoretical methods, is adopted to improve the algorithm efficiency. Further, to improve solution quality, an iterative method, local search based optimization with random restart, is adopted.

#### 1.3.2 Interconnection allocation between FUs and registers 35

The research of this part corresponds to the interconnection allocation step in HLS procedure. It solves the problem that, after functional unit and register binding, how to determine the interconnections

Figure 1.4: Common Technologies: graph theory, mathematical programming and iterative methods

between registers and functional unit ports, in order to minimize the interconnection complexity and multiplexer size, and further to reduce the interconnection power and chip area.

**Technologies:** it is first formulated as a graph with spanning tree, and solved using graph theoretical methods including elementary tree transformation and minimum vertex cover. Then, to improve algorithm efficiency, the problem is reformulated as LP problem by replacing adding operations in standard LP by exclusive-or operations. By doing so, the algorithm is speeded up by pivoting operations in standard LP, which is one of mathematical programming methods. Finally, to improve solution quality, similar to work 1, an iterative method, local search based optimization with random restart, is also adopted.

#### 1.3.3 Through silicon via (TSV) insertion for 3D-IC<sup>71</sup>

TSV insertion for 3D-IC is the physical synthesis for 3D ICs. It solves the problem that, given a floorplan of modular on a 3D chip and a net list, how to insert TSVs between chip dies, such that the total wire length that connecting signal pins and TSVs is minimized. More importantly, when the problem size is huge, i.e., over one thousand nets and more than 3 chip dies, how to solve the problem

Figure 1.5: Basic concept of High Level Synthesis.

within reasonable execution time without sacrificing the solution quality, while the current existing algorithms are not able to handle.

**Technologies:** it is first formulated by a multi-level graph, and is solved by mixed single and multiple commodity min-cost flow. To improve solution quality, the bipartite matching is adopted, which is also a method of graph theory.

#### 1.4 Preliminaries of High Level Synthesis

High-level synthesis (HLS), also referred to as behavioral synthesis, is an automated design process that interprets an algorithmic description of a desired behavior and creates digital hardware that implements that behavior<sup>2</sup>. Fig.1.5 shows the basic concept of HLS. The inputs of HLS are specifications described by languages with system-level abstractions such as ANSI C, SystemC, C++ or SystemVerilog. During synthesis process, the input codes are first compiled and analyzed, and procedures including operation scheduling, resource allocation and binding are went through. Then a register-transfer level (RTL) hardware description is generated, which is the outputs of the HLS, containing data path components including registers, multiplexers, functional units, buses, and controlling logics. Finally logic synthesis is conducted on the RTL structure.

#### 1.4.1 Necessity of High Level Synthesis

HLS technology begins to attract research interests since the late 20th century, and now is still one of the hottest topics in current EDA field. One of the reasons is, it enables IC designers to describe the design at a higher electronic system-level (ESL), and to efficiently build and verify hardware even

without specific hardware knowledge.

Another reason for HLS being strongly required is, the ESL paradigm is shifting to higher level of abstractions caused by the rise of system complexities. To be more exact, along with the integration of ICs growing rapidly in recent decades, the vary-large-scale integrated circuits (VLSI) and the ultra-large-scale integration circuits (ULSI), which have more than 1 million transistors, are being proposed and begin to put into production. The huge size of target circuits makes it impossible for manual design, especially from lower circuit levels due to the extremely huge number of circuit components. As a result, designing from higher circuit levels is an inevitable choice, that is, *fast IC scaling trend strongly calls for HLS*.

More importantly, in recent years, HLS is not only necessary for large scale designs; moreover, it is especially required for low power IC designs because of the outstanding performances that HLS technology has shown in a series of low power works, which is referred as to low power high level synthesis.

#### 1.4.2 Necessity of Low Power High Level Synthesis (HLS)

Along with the rapid growth of portable and battery-equipped devices, reducing power consumption has became the primary limiter of scaling semiconductor process technologies and adding features to integrated circuits. As a result, the IC design is undergoing a significant transition from performance oriented to power oriented, where power has became one of the first-priority design factors<sup>5</sup>. This transition invokes many researches working on low power techniques on register transfer level, such as power gating, clock gating, multiple supply or threshold voltage techniques, and recently approximate computing resources in error-tolerant applications.

However, as pointed out in<sup>5</sup>, attempting to reduce power at RT level typically requires much more efforts than at behaviourial or system level, because making decisions at higher levels usually result in larger impact on final designs. As shown in Fig.1.2, the higher abstraction level is, the less optimization effort is needed, and the higher power saving opportunity is. Consequently, reducing power from higher level imperatively calls for HLS techniques.

#### 1.4.3 Related Low Power HLS Works

#### Major Power Dissipations

There are broadly three kinds of power dissipations of a circuit: switching power (also referred to as dynamic power), static power (also called leakage power) and short-circuit power, Among the three, dynamic power, denoted as  $P_{dy}$ , and leakage power, denoted as  $P_{lk}$ , are much higher than the short-circuit power, and attract most research interests.

• Dynamic power is consumed through circuit activities, e.g. when switching takes place on logic gates, computed as:

$$P_{dy} = C_L \times V_{dd}^2 \times f \times sw \tag{1.1}$$

where  $C_L$  is the output capacitance,  $V_{dd}$  is the supply voltage, f is the clock frequency, and sw is the switching activity. Easy to see,  $P_{dy}$  is positively related to the supply voltage  $V_{dd}$  of logic gates, f and sw. Therefore, one effective way in HLS procedure to reduce dynamic power is to use multiple supply voltage (multi- $V_{dd}$ ) technology.

• Leakage power is primarily the result of unwanted subthreshold current in the transistor channels, and is consumed whenever circuit components are busy or idle. It has became more dominating than dynamic power especially in in deep sub-micron process technology (65nm and below), say more than 50% of the total IC power consumption  $^{50}$ , which makes it a top concern for current IC design. The subthreshold-driven leakage power is strongly influenced by variations in the transistor threshold voltage, denoted as  $V_{th}$ . Therefore, lowering threshold voltage, or using dual or multiple threshold voltage (multi- $V_{th}$ ), is effective to reduce leakage power.

#### Previous Low Power Technologies

There has already been a large amount of investigations on low power HLS techniques, to reduce either dynamic power or leakage power, which focus on one or several particular steps in HLS, such as operation scheduling, resource allocation or interconnection allocation. In the following several typical categories of low power technologies as well as their representative literatures are listed.

- Multiple supply voltage (multi- $V_{dd}$ ). The multiple supply voltage technology is mostly applied on operation scheduling or binding in HLS procedure, like  $^{10\,11\,12\,13\,14}$ . It shows promising results in reducing dynamic power by assigning different  $V_{dd}$  to operators. Chen et al.  $^{10}$  presented a network flow based dual- $V_{dd}$  binding algorithm for low-power resource binding with switching activity being considered. Liu et al.  $^{12}$  addressed a voltage partitioning problem arising in multiple supply voltage design during HLS. They proved it as NP-hard, and proposed an efficient approximation algorithm with linear time-complexity for practical designs, which is tens to hundreds of times faster than previous works. Jiang et al.  $^{13}$  discussed a multiple supply voltage scheduling problem in HLS to minimize the system power consumption. They formulated it as a linearly constrained separable convex optimization problem, and solved it using the integer time budgeting technique, which produced near-optimal results.

- Multiple threshold voltage (multi- $V_{th}$ ). The multiple threshold voltage technology is also applied on scheduling or binding like <sup>78923</sup>, where operations are first scheduled and are assigned to different types of functional units (FU) executed under different threshold voltages. In <sup>7</sup> a greedy method was proposed that prioritized modules with largest leakage reduction potentials for high- $V_{th}$  implementation. In <sup>8</sup> a composite constraint graph was proposed to present resource binding constraints, together with a maximum weight independent set based scheduling algorithm. In <sup>9</sup> leakage power was minimized by characterizing the bounded delay degradations for FUs with multi- $V_{th}$  values. The latest work <sup>23</sup> proposed a binding conflict

Figure 1.6: An example of 3D-IC and Through Silicon Vias (TSV).

graph based scheduling method to minimize the number of FUs. They all showed that multi- $V_{th}$  approach in HLS can significantly reduce leakage power dissipation.

- Power Reduction through Interconnection Optimization. Since the interconnections also consume a large fraction of leakage power, minimizing the interconnection complexity also reduces power consumption. For example in work <sup>39</sup>, the interconnections between functional units and registers are discussed. In other works <sup>40</sup> and <sup>41</sup>, other interconnections, for example multiplexers, are also considered.

- Other technologies like clock gating 42, power gating 44 45, d

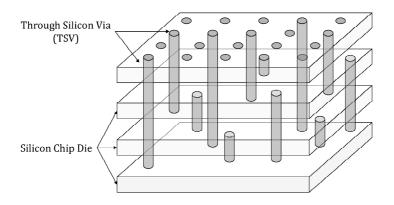

#### 1.5 Preliminaries of 3D-IC and Through Silicon Via Insertion

Three-dimensional integrated circuit (3-D IC) is a promising IC manufactural technology with stacks of dies that approaches higher density, reduced power, smaller footprint, improved performance and lower cost compared with traditional monolithic ICs, and many important works on 3-D IC technology are proposed in recent years <sup>65 66</sup>. The 3-D IC technology uses through-silicon vias (TSV) to provide vertical electrical connections passing through a silicon wafer or die. The TSV is an emerging interconnection technology that will replace the traditional wire-bonding process in chip/wafer stacking, to increase inter-die communication bandwidth, reduce form factor, and lower power consumption of stacked multi-die systems by eliminating the need of long cross-chip interconnects existing in 2-D ICs. Fig.1.6 shows an example of 3D IC die stacks with TSVs.

One of the key design challenges of 3-D IC is the optimization of the number and locations of TSVs, which is generally called the TSV assignment problem. Given a 3-D IC netlist describing the inter-die nets, TSV assignment is to decide which TSVs are used to implement the nets spanning different chip dies. After the TSV assignment, routing is applied on each die to complete the electrical connection of every net. Since the TSVs are very large compared to logic gates, say dozens to hundreds

of times the area of a standard cell, the TSV assignment is crucial to the wire length and signal delays of 3-D circuits, and it is now attracting broad interest among both academic and industrial researchers.

#### 1.6 Thesis Organization

This thesis consists five chapters. The rest of this thesis is organized as follows.

In chapter 2, [A Unified Scheduling Approach with Multiple  $V_{dd}$  or/and  $V_{th}$  in HLS], the dynamic and leakage power minimization problem using multiple  $V_{dd}$  and  $V_{th}$  technology in operation scheduling is discussed. The combined scheduling and binding method is also discussed in this chapter.

In chapter 3, [Interconnection Allocation Between Functional Units and Registers in HLS], the interconnection optimization techniques in HLS, which has not been fully investigated, is discussed in this chapter, and several algorithms are proposed for the port assignment problem between functional units and registers.

In chapter 4, [A Multi-Level Algorithm for 3D-IC TSV Assignment in Physical Synthesis], the problem of Through Silicon Via (TSV) insertion on 3D-ICs in physical synthesis is discussed, which has no practical algorithms when the problem size becomes huge. In this chapter the methodologies and graph theories used in HLS are utilized in physical synthesis stage.

In chapter 5, [Conclusions and Future Work], this thesis is concluded and some future works are given.

# 2

# A Unified Scheduling Approach with Multiple $V_{dd}$ or/and $V_{th}$ in HLS

In this chapter, the first topic, dynamic and leakage power minimization, is to be discussed, which corresponds to the scheduling and binding step in HLS. It determines the supply voltage or threshold voltage for operations and FUs, as well as the scheduling for operations, to minimize the total power consumption. The purpose is to propose algorithms to get optimum or near-optimum solutions. The problems are first formulated by Integer Linear Programming, and by relaxing to Linear Programming, the network simplex method is adopted iteratively to solve the LP problem for optimization. The detailed formulations and algorithms are discussed in the following of this chapter.

#### 2.1 Background and Contributions

Low power integrated circuit (IC) design, in the recent ten years, has been a substantial research theme because of the fast growth of portable computing devices and reliability requirements under higher operation temperature. The major power dissipation sources include leakage power, short circuit power and dynamic power, in which the leakage power and dynamic power are more dominating than short circuit power. The threshold driven leakage power is strongly influenced by the transistor threshold voltage  $V_{th}$ , and the dynamic power decreases with the decreasing of supply voltage  $V_{dd}$ . Consequently, it is promising and popular to use dual or multiple threshold voltage and/or multiple supply voltage technique for power reduction, by trading off the performance of less timing-critical logics<sup>5</sup>. For example, there are many approaches that minimize both the leakage and dynamic power in generic digital CMOS designs <sup>15 16 17 18</sup> by determining the  $V_{th}$  and  $V_{dd}$  of each module or logic gate in gate level.

Except for the CMOS level optimizations under multiple-voltage technologies, there are also many power scaling efforts have been made in the high-level synthesis (HLS) stage, because it was pointed out that power saving opportunities at behavioral and system levels are much higher than that at register-

transfer level (RTL)<sup>6</sup>. One of the most powerful techniques is multiple voltage scheduling, which allows functional units (FU) work with different threshold voltages  $V_{th}$ , or different supply voltages  $V_{dd}$ , with different execution delays.

The multiple supply voltage scheduling approaches  $^{10\,11\,12\,13\,14}$  showed promising results in reducing dynamic power by assigning different  $V_{dd}$ . Chen et al.  $^{10}$  presented a network flow based dual- $V_{dd}$  binding algorithm for low-power resource binding with switching activity being considered. Liu et al.  $^{12}$  addressed a voltage partitioning problem arising in multiple supply voltage design during HLS. They proved it as NP-hard, and proposed an efficient approximation algorithm with linear time-complexity for practical designs, which is tens to hundreds of times faster than previous works. Jiang et al.  $^{13}$  discussed a multiple supply voltage scheduling problem in HLS to minimize the system power consumption. They formulated it as a linearly constrained separable convex optimization problem, and solved it using the integer time budgeting technique, which produced near-optimal results.

The multiple threshold voltage scheduling approaches  $^{7\,8\,9\,23}$  schedule the operations and assign different threshold  $V_{th}$  voltages. In  $^7$  a greedy method was proposed that prioritized modules with largest leakage reduction potentials for high- $V_{th}$  implementation. In  $^8$  a composite constraint graph was proposed to present resource binding constraints, together with a maximum weight independent set based scheduling algorithm. In  $^9$  leakage power was minimized by characterizing the bounded delay degradations for FUs with multi- $V_{th}$  values. The latest work  $^{23}$  proposed a binding conflict graph based scheduling method to minimize the number of FUs. They all showed that multi- $V_{th}$  approach in HLS can significantly reduce leakage power dissipation.

Although a great quantity of literatures have been proposed for multiple voltage problems, further studies for multi- $V_{dd}$  and multi- $V_{th}$  scheduling are still needed. For example for multi- $V_{dd}$  problem, <sup>12</sup> fully studied voltage partitioning but not operation scheduling; <sup>13</sup> solved the scheduling problem but did not consider the resource usage. For multi- $V_{th}$  problem, <sup>9</sup> targeted in resource binding rather than scheduling, and the efficiency of the scheduling algorithm in <sup>23</sup> is a big concern. In addition, in previous works for leakage power reduction, either scheduling or binding is considered independently, but there is no work that considers two steps jointly. Accordingly, in this work, the multi- $V_{dd}$  problem and the multi- $V_{th}$  problem are first solved separately, and then discuss the impact of binding on the overall power including the interconnection power. Besides, for multi- $V_{dd}$  and multi- $V_{th}$  problems, a unified approach is proposed, which provides an opportunity that the dynamic and leakage power can be minimized simultaneously, which is believed to be worth studying.

In this paper, my previous work<sup>4</sup> is extended to propose a unified scheduling scheme that works both for leakage and dynamic power optimization, given multiple threshold or/and multiple supply voltages. In<sup>4</sup>, a dynamic power and resource co-optimization problem is solved under multiple supply voltage using Network Simplex Method; the additional contributions in this work are stated as:

• A unified scheduling scheme is proposed for three different optimization problems: (1) dynamic power and resource co-optimization; (2) leakage power optimization; (3) dynamic power and leakage power co-optimization.

- It is revealed that the three problems with multiple objectives share two common sub-problems: operation delay assignment and resource density variance minimization; the two sub-problems are simultaneously solved using **vertex potentials** proposed in this work.

- For leakage power optimization, **a post processing** is proposed to eliminate the limitation of the proposed scheduling algorithm when being utilized for leakage power.

- Functional unit and register binding is combined into operation scheduling, to reduce multiplexer and register power, thus to reduce overall power consumption.

- It is shown in the experiments that, when the proposed unified scheduling scheme is utilized for leakage power minimization, it significantly excels the latest existing work both in terms of power and execution time.

The rest of this chapter is organized as follows. Section 2.2 gives the problem formulation, Section 2.3 motivates this work, Section 2.4 solves the delay assignment problem, and Section 2.5 solves the resource density minimization problem. Section 2.7 introduces the unified scheduling scheme, and Section 2.8 utilizes it on three problems. Section 3.6 shows the experimental results, followed by conclusions in Section 2.10.

#### 2.2 Problem Formulations

In this section, the inputs, outputs, and objectives of three problems are clarified, followed by a unified Integrated Linear Programming (ILP) formulation for three problems.

#### 2.2.1 Problem Description

According to  $^{23}$ , for a FU under a fixed supply voltage  $V_{dd}$ , its leakage power decreases, and delay increases monotonously along with the increasing of threshold voltage  $V_{tb}$ ; according to  $^{13}$ , for a FU under a fixed  $V_{tb}$ , its dynamic power decreases, and delay increases monotonously along with the decreasing of  $V_{dd}$ . In this work, the schedulings under a fixed  $V_{tb}$  and multi- $V_{dd}$ , and under a fixed  $V_{dd}$  and multi- $V_{tb}$ , are mainly discussed. Since the delay-voltage curve of a FU is monotonous, to unify  $V_{dd}$  and  $V_{tb}$ , the FU delays are considered instead of their real voltage values during scheduling; after scheduling, the real voltages for FUs can be known according to their delays.

The **inputs** of the scheduling algorithm include:

- A data flow graph (DFG) G = (V, E) of a behavioral description, where V is the set of operations and E is the data dependencies. Each operation  $op \in V$  has a type  $\tau_{op} \in \Gamma$ , where  $\Gamma$  represents all operation types such as addition, multiplication, etc.

- A discrete function describing the *leakage* power of FUs under fixed  $V_{dd}$  and different  $V_{th}$ , denoted as LK (d),  $\tau \in \Gamma$ . d is the FU delay under a certain  $V_{th}$ , given in the number of clock cycles, i.e., the number of control steps, where  $d_{min} \leq d \leq d_{max}$ . LK (d) is the leakage power of a FU of type  $\tau$  and delay d.

Table 2.1: Dynamic Power-Delay Table for ADD and MUL under clock frequency of 769MHz (clock period 1.3ns)

|     | $P_{	extit{dynamic}} \ (\mu W)$ | Exec.<br>Time | $V_{DD}$ (volts) | Delay<br>(clock cycles) |

|-----|---------------------------------|---------------|------------------|-------------------------|

|     | 195.46                          | 1.2ns         | 1.1              | 1                       |

| ADD | 62.44                           | 2.0ns         | 0.9              | 2                       |

|     | 34.67                           | 2.7ns         | 0.7              | 3                       |

|     | 2259                            | 2.3ns         | 1.1              | 2                       |

| MUL | 723                             | 3.9 ns        | 0.9              | 3                       |

|     | 384                             | 5.2ns         | 0.7              | 4                       |

T .2: Leakage Power-Delay Table for ADD and MUL under clock frequency of 769M (clock period 1.3ns)

|     | $P_{leak}$ | Exec. | $V_{th}$                            | Delay          |

|-----|------------|-------|-------------------------------------|----------------|

|     | $(\mu W)$  | Time  | (volts)                             | (clock cycles) |

| ADD | 160.05     | 1.1ns | 0.18 (low- $V_{th}$ )               | 1              |

|     | 7.11       | 1.4ns | $0.32 \text{ (high-}V_{th}\text{)}$ | 2              |

| MUL | 270.71     | 2.1ns | 0.18 (low- $V_{th}$ )               | 2              |

|     | 27.40      | 3.4ns | $0.32 \text{ (high-}V_{th}\text{)}$ | 3              |

• A discrete function describing the *dynamic* power of FUs under fixed  $V_{th}$  and different  $V_{dd}$ , denoted as DY(d),  $\tau \in \Gamma$ . d is the FU delay under a certain  $V_{dd}$ , where  $d_{min} \leq d \leq d_{max}$ . DY(d) refers to the dynamic power of a FU for an *active execution*.

The **constraint** is the scheduling latency, denoted as  $T_{con}$ , which is the maximum allowable number of control steps to finish the execution of data flow.

The **outputs** include: (1) a delay assignment for each  $op \leftarrow d$ ,  $op \in V$  and (2) a scheduling for each  $op \leftarrow [t, T_{con}]$ ,  $op \in V$  such that all the dependency constraints are satisfied.

The **objectives** for three problems are separatively stated as: