超高周波用三次元高密度実装のための ダイレクト金めっきを用いた 低応力接合技術

Low stress bonding technology using direct immersion gold for ultra-high frequency and high density three-dimensional package

2018年7月

乃万 裕一 Hirokazu NOMA 超高周波用三次元高密度実装のための ダイレクト金めっきを用いた 低応力接合技術

Low stress bonding technology using direct immersion gold for ultra-high frequency and high density three-dimensional package

# 2018年7月

早稲田大学大学院 先進理工学研究科 ナノ理工学専攻 マイクロシステム研究

> 乃万 裕一 Hirokazu NOMA

目次

| 目次i                                       |

|-------------------------------------------|

| 図表一覧                                      |

| 略語一覧 ···································· |

|                                           |

| 第一章 序論                                    |

| 1.1 研究背景                                  |

| 1.1.1 「モノ」のインターネット                        |

| 1.1.2 ムーアの法則の終焉と三次元実装                     |

| 1.1.3 モバイル機器の薄型化4                         |

| 1.2 三次元実装の課題                              |

| 1.2.1 パッケージ厚さの増大                          |

| 1.2.2 チップ積層による放熱の難化6                      |

| 1.3 三次元実装の課題解決への提案                        |

| 1.3.1 低誘電率層保護                             |

| 1.3.2 パッケージ基板への両面実装                       |

| 1.3.3 チップ間接合高さの低減                         |

| 1.4 提案内容についての従来技術                         |

| 1.4.1 低誘電率層保護技術                           |

| 1.4.2 両面フリップチップ実装技術8                      |

| 1.4.3 銅の直接接合技術                            |

| 1.5 ダイレクト金めっき等の表面処理技術                     |

| 1.5.1 他の金処理手法からの優位性                       |

| 1.5.2 ダイレクト金めっきの用途の拡大提案                   |

| 1.5.3 有機防錆被膜、無電解スズめっき                     |

| 1.6 本論文の目的                                |

| 1.7 銅ピラーを用いた微細ピッチフリップチップ技術                |

| 1.8 本論文の概要                                |

| 1.9 参考文献                                  |

| 第二章 ダイレクト金めっきを用いた低応力接合                                                                                                                                                                                                                                                                                                                                  | ··· 21                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 2.1 緒言                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| 2.2 実験および数値計算······                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| 2.2.1 基板上のパッドの表面へのはんだ濡れ性                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| 2.2.2 はんだ接合部形状の数値計算                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| 2.2.3 低誘電率層への応力解析                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| 2.3 結果と考察                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

| 2.3.1 ダイレクト金めっきによる、                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| はんだの基板側銅パッドへの濡れ改善                                                                                                                                                                                                                                                                                                                                       | 29                                                                               |

| <b>2.3.2</b> 界面合金層形成による、はんだ接合高さの制限                                                                                                                                                                                                                                                                                                                      | 32                                                                               |

| 2.3.3 ダイレクト金めっきによる低誘電率層への応力低減                                                                                                                                                                                                                                                                                                                           |                                                                                  |

| 2.3.4 銅ピラーの側面にはんだが濡れ上がる閾値のはんだ体積…                                                                                                                                                                                                                                                                                                                        | 36                                                                               |

| 2.4 結言                                                                                                                                                                                                                                                                                                                                                  | 38                                                                               |

| 2.5 参考文献                                                                                                                                                                                                                                                                                                                                                | 39                                                                               |

|                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

| 第三章 ダイレクト金めっきを用いたチップ間低背接合                                                                                                                                                                                                                                                                                                                               | 43                                                                               |

|                                                                                                                                                                                                                                                                                                                                                         | -                                                                                |

| 3.1 緒言                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                         | 44                                                                               |

| 3.1 緒言                                                                                                                                                                                                                                                                                                                                                  | ··· 44<br>··· 46                                                                 |

| <ul><li>3.1 緒言 ···································</li></ul>                                                                                                                                                                                                                                                                                            | ··· 44<br>··· 46<br>··· 46                                                       |

| <ul> <li>3.1 緒言</li></ul>                                                                                                                                                                                                                                                                                                                               | 44<br>46<br>46<br>46                                                             |

| <ul> <li>3.1 緒言</li></ul>                                                                                                                                                                                                                                                                                                                               | ··· 44<br>··· 46<br>··· 46<br>··· 46<br>··· 46                                   |

| <ul> <li>3.1 緒言</li></ul>                                                                                                                                                                                                                                                                                                                               | 44<br>46<br>46<br>46<br>46<br>47                                                 |

| <ul> <li>3.1 緒言</li></ul>                                                                                                                                                                                                                                                                                                                               | 44<br>46<br>46<br>46<br>47<br>47                                                 |

| <ul> <li>3.1 緒言…</li> <li>3.2 実験…</li> <li>3.2.1 評価用試料の準備…</li> <li>3.2.2 ダイレクト金めっき前後の表面粗さ測定</li> <li>3.2.3 接合手法</li> <li>3.2.4 シェア試験での破断モードによる接合強度評価</li> <li>3.2.5 金の銅への拡散の評価方法</li> </ul>                                                                                                                                                            | 44<br>46<br>46<br>46<br>47<br>47<br>47                                           |

| <ul> <li>3.1 緒言…</li> <li>3.2 実験…</li> <li>3.2.1 評価用試料の準備…</li> <li>3.2.2 ダイレクト金めっき前後の表面粗さ測定</li> <li>3.2.3 接合手法</li> <li>3.2.4 シェア試験での破断モードによる接合強度評価</li> <li>3.2.5 金の銅への拡散の評価方法</li> <li>3.3 結果と考察</li> </ul>                                                                                                                                         | 44<br>46<br>46<br>46<br>47<br>47<br>47<br>47                                     |

| <ul> <li>3.1 緒言</li></ul>                                                                                                                                                                                                                                                                                                                               | 44<br>46<br>46<br>46<br>47<br>47<br>47<br>47<br>49                               |

| <ul> <li>3.1 緒言</li></ul>                                                                                                                                                                                                                                                                                                                               | 44<br>46<br>46<br>46<br>47<br>47<br>47<br>47<br>47<br>49<br>50                   |

| <ul> <li>3.1 緒言…</li> <li>3.2 実験…</li> <li>3.2.1 評価用試料の準備</li> <li>3.2.2 ダイレクト金めっき前後の表面粗さ測定</li> <li>3.2.3 接合手法</li> <li>3.2.4 シェア試験での破断モードによる接合強度評価</li> <li>3.2.5 金の銅への拡散の評価方法</li> <li>3.3 結果と考察</li> <li>3.3 結果と考察</li> <li>3.3.1 ダイレクト金めっき前後の表面粗さ</li> <li>3.3.2 シェア試験での破断モードの接合温度依存</li> <li>3.3.3 接合後試料の断面観察による接合状態評価</li> </ul>                 | 44<br>46<br>46<br>46<br>47<br>47<br>47<br>47<br>47<br>49<br>50<br>50             |

| <ul> <li>3.1 緒言…</li> <li>3.2 実験…</li> <li>3.2.1 評価用試料の準備…</li> <li>3.2.2 ダイレクト金めっき前後の表面粗さ測定</li> <li>3.2.3 接合手法</li> <li>3.2.4 シェア試験での破断モードによる接合強度評価</li> <li>3.2.5 金の銅への拡散の評価方法</li> <li>3.3 結果と考察</li> <li>3.3.1 ダイレクト金めっき前後の表面粗さ</li> <li>3.3.2 シェア試験での破断モードの接合温度依存</li> <li>3.3.3 接合後試料の断面観察による接合状態評価</li> <li>3.3.4 ダイレクト金めっきによる低背接合の実現</li></ul> | 44<br>46<br>46<br>46<br>47<br>47<br>47<br>47<br>47<br>49<br>50<br>50<br>52       |

| <ul> <li>3.1 緒言…</li> <li>3.2 実験…</li> <li>3.2.1 評価用試料の準備</li></ul>                                                                                                                                                                                                                                                                                     | 44<br>46<br>46<br>46<br>47<br>47<br>47<br>47<br>47<br>49<br>50<br>50<br>52<br>54 |

| 第四章 銅パッド表面処理の最適化による両面実装           |

|-----------------------------------|

| 4.1 緒言                            |

| 4.2 実験                            |

| 4.2.1 両面実装のプロセスフロー60              |

| 4.2.2 はんだ濡れ評価                     |

| 4.2.3 温度サイクル信頼性評価64               |

| 4.2.4 ダイレクト金めっき等の表面処理65           |

| 4.2.5 評価用基板                       |

| 4.3 はんだ濡れ性の結果と考察                  |

| 4.3.1 有機防錆被膜での濡れ不良の薬品種・厚みへの依存68   |

| 4.3.2 無電解スズでの濡れ不良の熱履歴への依存69       |

| 4.3.3 ダイレクト金めっきでの濡れ不良の膜厚への依存69    |

| 4.3.4 微細ピッチの両面実装へのダイレクト金めっきの有望性70 |

| 4.4 濡れ不良の無い両面実装パッケージでの            |

| 温度サイクル信頼性評価                       |

| 4.5 結言74                          |

| 4.6 参考文献                          |

|                                   |

| 第五章 結論と今後の展望                      |

| 5.1 結論                            |

| 5.2 今後の展望                         |

| 5.2.1 ミリ波通信                       |

| 5.2.2 チップ間のリフロー接合                 |

| 5.2.3 高性能サーバー                     |

| 5.2.4 磁界結合メモリ                     |

| 5.3 参考文献                          |

|                                   |

| 謝辞                                |

| 業績一覧                              |

# 図表一覧

## 図一覧

#### 第一章

- 図 1.1 自動車間通信を中心とした

|       | (a)は 90 nm、(b)は 45 nm 世代の Cell Broadband Engine。 | 4  |

|-------|--------------------------------------------------|----|

| 図 1.3 | 三次元方向へのチップ積層                                     | 4  |

| 図 1.4 | パッケージ基板上の三次元実装パッケージの断面                           | 5  |

| 図 1.5 | 三次元実装部の外気との温度差                                   | 6  |

| 図 1.6 | 三次元実装の厚みと放熱の課題への提案内容                             | 8  |

| 図 1.7 | ニッケル・金めっきとダイレクト金めっき工法                            | 11 |

| 図 1.8 | ダイレクト金めっきの用途拡大                                   | 11 |

| 図 1.9 | 微細ピッチフリップチップ向けのチップ・基板構造                          |    |

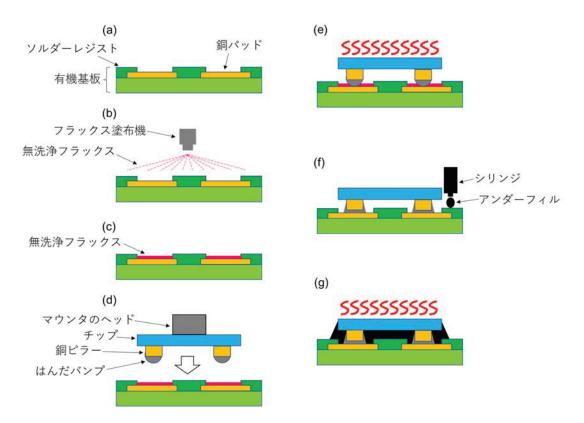

左はチップ、右は基板。上は上面図、下は断面図。 ……………… 13 図 1.10 無洗浄フラックス・リフロー・後入れアンダーフィル

による実装工法。(a)パッケージ基板、(b)フラックス塗布、

(c)塗布後の基板、(d)チップ搭載、(e)リフローはんだ付け、

(f)アンダーフィル塗布、(g)オーブンで硬化。………………13

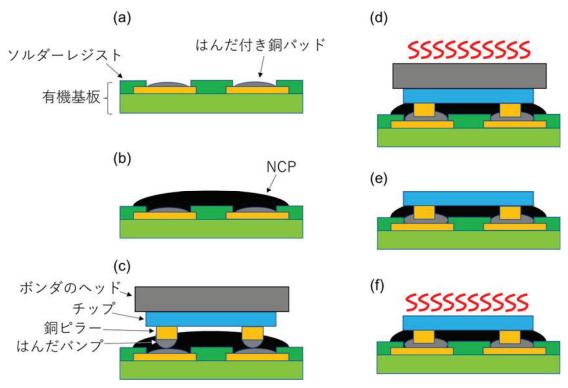

図 1.11 Nonconductive paste を用いた Thermal compression bonding

による実装工法。(a)パッケージ基板、(b)NCP 塗布、

(c)ボンダで位置合わせ、(d)ボンダではんだ付け、

- (e)ボンダから取り出し、(f)オーブンで最終硬化。………………14

#### 第二章

| 図 2.1 | TV 基板の拡大図 (チップの角に対応する部分)2   | 3 |

|-------|-----------------------------|---|

| 図 2.2 | 光学顕微鏡による断面観察箇所の上面図          | 3 |

| 図 2.3 | はんだ形状計算結果。表面処理は OSP で、      |   |

|       | はんだ接合高さは9μm。(a)初期条件。はんだ表面は  |   |

|       | 平面の組み合わせ。(b)計算結果。ラプラスの式を解き、 |   |

|       | 表面形状が収束した状態。2               | 5 |

リフロー後の断面の、右側の接合部(赤囲み)の解析。

上から二段目にコンター図は、Low-k層応力分布の上面図。

下段は、左上図の赤囲み部の拡大図。

下段図中の矢印はリフロー後冷却時にかかる歪み方向。………35 図 2.13 はんだ体積閾値でのはんだ接合部形状の模式図…………37 図 2.14 はんだのチップ側銅ピラーへの濡れ上がりの閾値…………38

第三章

図 3.1 DIG を中間層として用いた銅の直接接合のコンセプト ……… 45

図 3.2 接合サンプル断面模式図 ………… 46

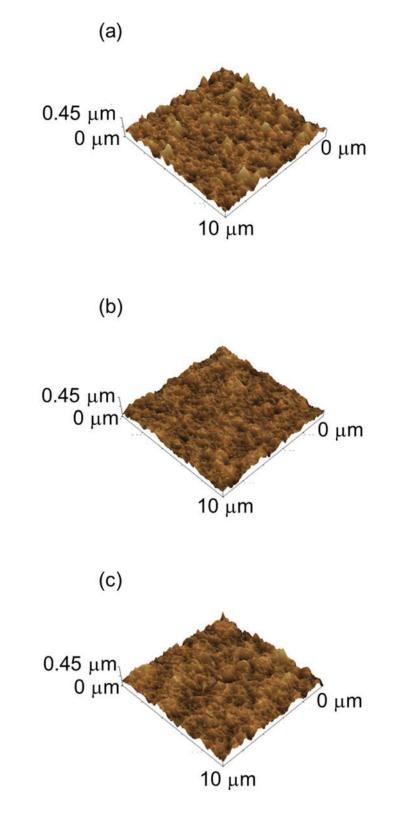

図 3.3 DIG 処理前後での AFM 結果。(a)DIG 前の銅表面、

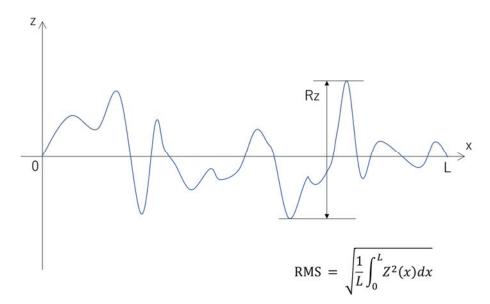

(b)0.1 μm 厚さの DIG 処理後、(c)0.2 μm 厚さの DIG 処理後…48 図 3.4 Rz と RMS の定義

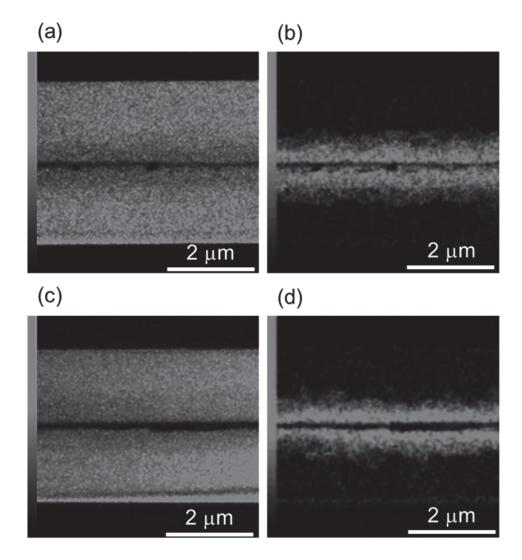

(x は面内方向の距離。z は高さ。L は測定長さ)………49図 3.5 接合後断面の TEM-EDX マッピング。

(a)  $\geq$  (b)  $\wr$ t DIG t0.2  $\mu$ m、 (c)  $\geq$  (d)  $\wr$ t DIG t0.1  $\mu$ m 。

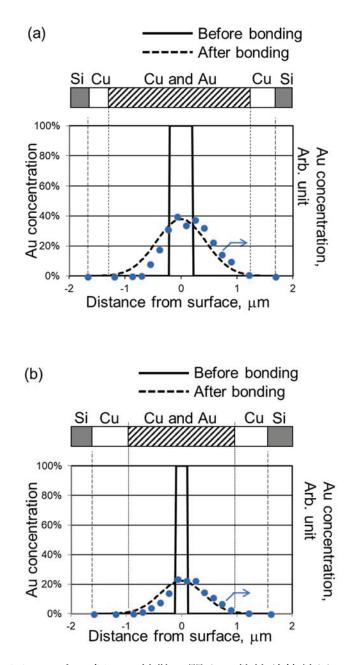

図 3.7 金の銅への拡散に関する数値計算結果。

実線はボンディング前の金濃度、点線はフィッティングに

より求めた拡散係数での接合後の金濃度。

(a)は DIG t0.2 µm サンプル(拡散係数 1.0×10<sup>-16</sup> m<sup>2</sup>/s)、

(b)は DIG t0.1 µm サンプル(拡散係数 8.3×10<sup>-17</sup> m<sup>2</sup>/s)。…… 53

図 3.8 金による表面粗さ吸収の推定メカニズム……55

第四章

# 表一覧

## 第二章

- 表 2.1 構造解析に用いた機械特性一覧。

- (a) はんだ以外の、弾性解析を用いた材料

- (b) はんだ材料のノートン則 $d\varepsilon / dt = A\sigma^n$ の温度ごとの定数。

ここで、*ε*はクリープ歪み、*A*は定数、*σ*は応力、*n*は指数。…27 表 2.2 構造解析結果 (Low-k 層応力およびはんだ接合部の歪み)……35

#### 第三章

| 表 3.1 | 接合条件         | 47 |

|-------|--------------|----|

| 表 3.2 | 表面粗さの測定値     | 49 |

| 表 3.3 | シェア試験での破断モード | 50 |

#### 第四章

| プルに対する熱履歴6                                  | 表 4.1 |

|---------------------------------------------|-------|

| i性評価条件 ···································· | 表 4.2 |

| 評価に用いた表面処理6                                 | 表 4.3 |

| 評価結果                                        | 表 4.4 |

| i<br>性評価結果                                  | 表 4.5 |

# 略語一覧

| 5G | Fifth | generation |

|----|-------|------------|

|----|-------|------------|

- AFM Atomic force microscope

- BGA Ball grid array

- C2 Chip connection

- C4 Controlled collapse chip connection

CMOS Complementary metal oxide semiconductor

- CMP Chemical mechanical polishing

- CPI Chip package interaction

- CTE Coefficient of thermal expansion

- CUF Capillary underfill

- DIG Direct immersion gold

- E-less Electroless

- EDX Energy dispersive X-ray spectrometry

- FEM Finite element method

- IMC Intermetallic compounds

- ICF Inter-chip fill

- IoT Internet of things

- NCP Nonconductive paste

- OSP Organic solderability preservative

- PoP Package on package

- RMA Rosin mildly activated

- RMS Root mean square

- Rz Peak-to-peak surface roughness

- SAB Surface activated bonding

- SEM Scanning electron microscope

- SMT Surface mount technology

- TC Temperature cycle

- TCB Thermal compression bonding

- TEM Transmission electron microscope

- THB Temperature humidity bias

- TSV Through silicon via

- TV Test vehicle

- VUV Vacuum ultra violet

# 第一章 序論

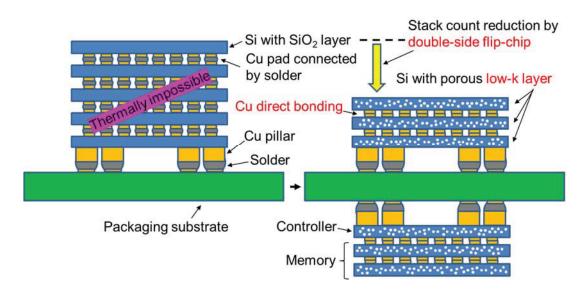

近年、ムーアの法則による半導体集積密度の向上は終焉したと言われている。 それに代わり、貫通シリコン電極を用いた三次元実装が実用化されている。三 次元実装の課題として、放熱とパッケージ厚みが挙げられる。

放熱については、チップ内の絶縁材料に低誘電率材料を用いることにより消 費電力を減らすことや、両面実装により片面あたりのチップ積層数を減らすこ とが考えられる。

しかし、低誘電率材料の利用にあったっては、接合時の熱によるチップとパ ッケージの相互作用に起因するチップへのダメージが課題となる。さらに、パ ッケージ基板の両面にチップを接合する際は、一面目を接合する際に二面目の 基板側銅パッドの表面が酸化するという問題が存在する。

パッケージ厚みについては、チップ自体の厚みを減らすだけでなく、チップ 間の接合距離を縮めることも重要である。それには銅の直接接合が有効である ものの、表面のナノメートルレベルでの平坦化と、表面の酸化防止の課題が残 っている。

本章では、低誘電率材料の利用、両面実装、銅の直接接合に関する課題を、 基板側の銅パッドの上に直接金を置換還元めっきするダイレクト金めっきに着 目して解決することを提案する。

なお、本章の図のうち IEEE が著作権を保有しているものに関する注意点は以下の通り。 In reference to IEEE copyrighted material which is used with permission in this thesis, the IEEE does not endorse any of WASEDA University's products or services. Internal or personal use of this material is permitted. If interested in reprinting/republishing IEEE copyrighted material for advertising or promotional purposes or for creating new collective works for resale or redistribution, please go to http://www.ieee.org/publications\_standards/publications/rights/rights\_link.ht ml to learn how to obtain a License from RightsLink.

1.1 研究背景

1.1.1 「モノ」のインターネット

「モノ」のインターネット(Internet of things, IoT)というコンセプトが提唱 されている[1]。あらゆるものにセンサーをつけ、そこから上がってくる情報を リアルタイムに処理しフィードバックするコンセプトである。IoT を支える通信 技術としてミリ波という超高周波が期待される[2-4]。それは、第五世代通信 (Fifth Generation, 5G)では 28 GHz[2]、自動車間通信では 77 GHz[3, 4]の周波 数である。そして、IoT を支える通信デバイスには小型化が求められる。さらに、 IoT のための高速情報処理には、現在以上に高性能なサーバーが必要である。以 上をまとめると、IoT には、超高周波、高密度、高性能が求められる。

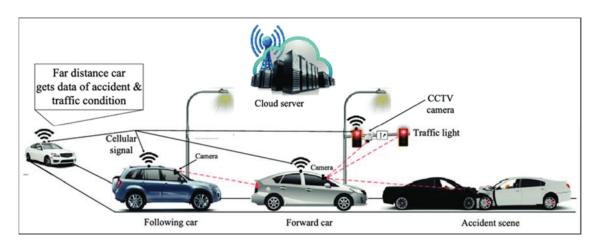

図 1.1 に、IoT の一例を示す[3]。これは、ミリ波による自動車間通信や信号 機により得られたデータを高速サーバーで処理するコンセプトである。

図 1.1 自動車間通信を中心とした「モノ」のインターネットのコンセプト[3] © The Author(s) 2018

1.1.2 ムーアの法則の終焉と三次元実装

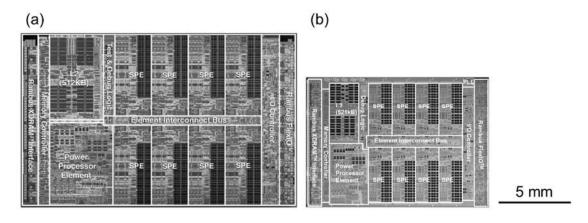

前述のムーアの法則によるトランジスタの集積化[5,6]に代わり、貫通シリコ ン電極 (Through silicon via, TSV)を用いた三次元実装がメモリ分野などで実用 化されている[7-10]。三次元実装では、単に TSV を形成するだけでなく、チッ プ同士などでの、接合技術も重要となる。図 1.2 に、同じ性能の半導体チップが、 半導体設計ルールの微細化によって小さくなった、つまり、トランジスタの単 位面積あたりの密度が高くなった事例を示す。トランジスタが、チップの面内 に集積されている様子がわかる[11, 12]。さらに、図 1.3 に、チップが縦方向に 集積された、三次元実装の例を示す[10]。

図 1.2 二次元的なチップ内でのトランジスタの集積化[11, 12] (a)は 90 nm、(b)は 45 nm 世代の Cell Broadband Engine。 (a)は© 2006 IEEE、(b)は© 2008 IEEE、スケールは筆者。

図 1.3 三次元方向へのチップ積層[10] © 2012 IEEE

#### 1.1.3 モバイル機器の薄型化

三次元にチップを積層すると、パッケージが厚くなってしまう課題がある。 携帯電話の厚みが年々薄くなってきており、この傾向は今後も続くと予想でき る[13]。そのとき、パッケージの厚さも、製品と同時に薄くなる必要がある。 1.2 三次元実装の課題

三次元にチップを積層することにより新たな課題が出ている。本節はそれら の課題を解説する。

1.2.1 パッケージ厚さの増大

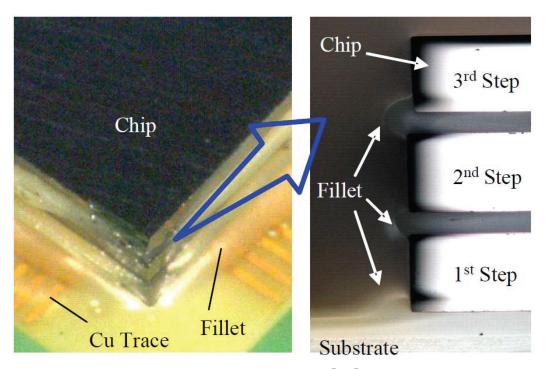

図 1.4 は、パッケージ基板の上にシリコンが積層された三次元実装構造の断面 である[14]。シリコンの積層構造が、パッケージ基板よりも厚く、支配的にな っていることがわかる。シリコンチップが 1 枚だけパッケージ基板へと搭載さ れた構造ではパッケージ基板の厚みが支配的であったのとは、状況が異なって いる。

図 1.4 パッケージ基板上の三次元実装パッケージの断面[14] © 2015 IEEE

1.2.2 チップ積層による放熱の難化

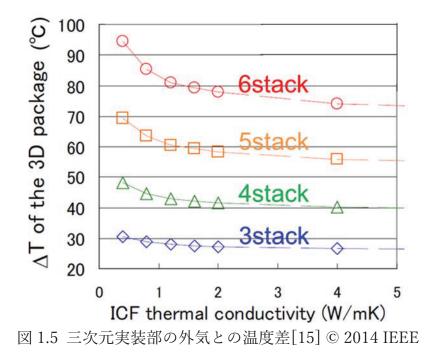

図 1.5 は、横軸に Inter-chip fill (ICF) というチップ間の樹脂材料の熱伝導率 を、縦軸に外気との温度差を示したものである[15]。チップの積層数が 3 段で あれば 30 ℃であった温度差が、6 段になると 100 ℃近くにも到達することがわ かる。仮にチップの動作温度を 85 ℃[16]、外気温度を 30 ℃とすれば、積層数 は最大で 4 段までとなる。この課題を解決するには、単に ICF の熱伝導率を上 げるだけでなく、チップの発熱自体を減らしたり、積層数を抑制したりする必 要がある。

CMOS (Complementary metal oxide semiconductor) チップの消費電力を式 1.1 に示す[17]。

$$P = n \times (CV^2 f + I_L V) \tag{1.1}$$

ここで、Pは発熱、nはトランジスタ数、Cは容量、Vは電源電圧、fは周波数、 Lはリーク電流である。従来であればスケーリングによって、二乗で効いている 電圧を下げていたが、現在は、性能である周波数 fを犠牲にせずに消費電力を減 らすには、容量 Cを減らす、つまり、配線間の絶縁材料の誘電率を減らすこと が考えられている。

1.3 三次元実装の課題解決への提案

図 1.6 を用いて本論文での提案内容を説明する。

1.3.1 低誘電率層保護

熱の課題について、配線容量を減らすためには、今までのシリコン酸化膜よ りも誘電率の低い Low-k 層を絶縁膜として使う必要がある。そのためには、一 般的に脆い機械特性を持つ Low-k 層を保護する必要がある。

1.3.2 パッケージ基板への両面実装

両面実装により積層数を低減することも、放熱上の対策となる。仮に積層メ モリチップを考えた場合、今まではメモリコントローラーの上にメモリを4段 以上積むことは、放熱の観点で不可能であった。それが、両面実装により、メ モリを片面2段ずつに減らすことが可能である。その結果として、メモリコン トローラーを含めて、合計3段ずつに積層数を減らせ、放熱が可能になる。

1.3.3 チップ間接合高さの低減

厚さについては、単にチップの厚みを薄くするだけでなく、はんだを用いな い銅の直接接合によって、接合高さも減らすことも重要である。

図 1.6 三次元実装の厚みと放熱の課題への提案内容

#### 1.4 提案内容についての従来技術

1.4.1 低誘電率層保護技術

チップに Low-k 層が使われ、それをリフローで有機基板へ接合する場合は、 実装時の信頼性の確保が重要である。それは、シリコンと有機基板との熱膨張 係数(Coefficient of thermal expansion, CTE)差に起因する歪みが接合部に集 中し、結果として、Low-k 層のうち接合部近傍の箇所へと局所的に応力がかか るためである。研究例としては、銅ピラー径などの設計寸法を最適化するもの [18]や、リフローの温度プロファイルという工程条件を最適化するもの[19]があ る。なお、リフローとは、窒素で満たされたベルトコンベア式の炉の中にサン プルを次々に入れ、複数のサンプルを高い生産性ではんだ接合するための工程 である。

しかし、究極的な低誘電率層であるエア・ギャップ技術[20]を適用するには依 然として技術開発が必要である。

1.4.2 両面フリップチップ実装技術

両面実装は、BGA (Ball grid array)を用いたマザーボードへの二次実装分野 に応用されてきた。その際、端子ピッチは 1 mm と広いものであるため、強力 なフラックスを用いて、後からフラックス洗浄をすることが可能である。この ことは、一面目を実装する時のリフローなどの熱履歴により反対面のパッドが 酸化したとしても、フラックスによる還元効果が十分に期待できることを意味 している。熱履歴による表面の酸化という意味では、Package on package (PoP) の実装でも同様のことが起きるものの、端子ピッチは 0.5 mm であり、洗浄が必 要なフラックスが利用されている[21]。三次元実装においても、端子ピッチが 0.1 mm であれば、熱履歴がかかった面に対して洗浄が必要なフラックスが利用 された例がある[22]。

しかし、61 µm 以下の微細なピッチでは、熱履歴がかかった場合にはフラッ クスの洗浄が必要ない工程が研究されている。それは、そもそもフラックスを 利用しないマイクロスクラブ [23]などの工法や、無洗浄フラックスを利用する 工法[24]である。

1.4.3 銅の直接接合技術

銅の直接接合は、はんだを用いるリフローと比べ生産性が低いものの、はん だ接合よりも低背化できる。その理由は、接合にはんだが必要なく、低融点で ある Sn を含む Cu-Sn 系の界面合金層(Inter-metallic compound, IMC)が急速 に形成されること[25]による銅表面の浸食が少ないことである。銅の直接接合 については多数の研究がされてきた。過去の研究での鍵となるのは、非常に平 坦な表面が必要になることである。一般的には CMP (Chemical mechanical polishing) [26]が用いられるものの、スラリーなどのコストが高い課題がある。 また、直接接合と樹脂同士の接合を同時に実現するため、ダイヤモンドバイト による超精密切削を行う研究例もある[27]。上記文献の両方で、ナノメートル レベルで平坦な表面が接合の前に求められており、工程上の課題となっている。

銅の直接接合の先行研究のもう一つの課題として、銅表面の酸化防止が挙げ られる。蟻酸の蒸気下で酸化銅を還元し加熱・加圧により接合を行う蟻酸接合 [28]や、表面活性化接合(Surface activated bonding, SAB)[29]がある。蟻酸接 合では沸点の低い酸を使うことによる安全面での課題、SAB には超高真空が必 要であるという工程上の問題がある。

また、将来顕在化が予想される課題として、超高周波への対応がある。銅の 直接接合は、はんだを用いた場合よりも接合部の抵抗が低く超高周波に適する

利点もある。

1.5 ダイレクト金めっき等の表面処理技術

1.3 で述べた従来技術の課題を解決するために、ダイレクト金めっき(Direct immersion gold, DIG)技術[30]に着目した。本節では、DIG をはじめとした、 銅パッドの表面処理技術を紹介する。

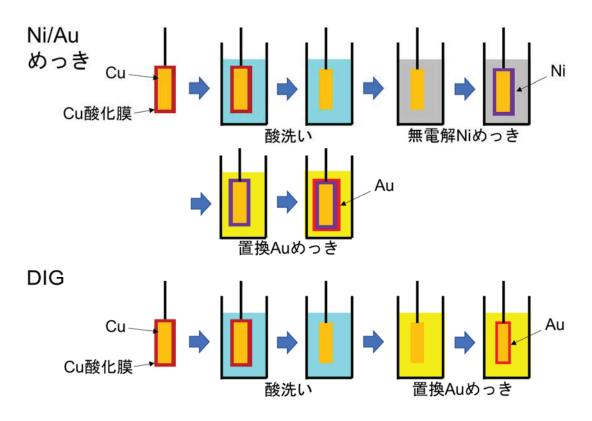

1.5.1 他の金処理手法からの優位性

DIG の概要を従来のニッケルバリア層を介した Ni/Au めっき[31]と比較し図 1.7 に示す。銅に対してニッケルバリア層を介することなく、置換還元金めっき を直接行うものである。そのため、微細なピッチの接合に適していることや、 銅表面の酸化膜を酸洗いによって除去してから直ちに金めっき浴へと試料を移 すため、自然酸化膜は極薄くしか形成されず、実用上は酸化膜の除去が必要な いという特長もある。さらに、金表面へははんだが濡れ広がりやすいため、従 来の銅表面の処理方法とは実装後のはんだ形状が異なるという特長もある。

1.5.2 ダイレクト金めっきの用途の拡大提案

今まで DIG は、マザーボードへの二次実装におけるはんだ接合部信頼性の向 上の目的で用いられてきた[32]。本論文では、DIG が微細なピッチにも適用可 能であることに注目し、図 1.8 に示すように、チップと基板間の接合、さらには チップ間の接合にまで、DIG を応用する。

1.5.3 有機防錆被膜、無電解スズめっき

従来から表面処理として使われている有機防錆被膜(Organic soldering preservative, OSP)は、銅の上に有機物の錯体結合を形成し銅の酸化を抑制するものである[33]。また、無電解スズめっきははんだプリコート[34]に替わる表面処理の技術候補である[33]。

図 1.7 ニッケル・金めっきとダイレクト金めっき工法[30,31]

Red lines: DIG surface

図 1.8 ダイレクト金めっきの用途拡大

#### 1.6 本論文の目的

超高周波用三次元高密度実装構造における課題を、DIGの表面処理によって 解決することを本論文の目的とした。

先ず、超高周波向け三次元チップ積層の課題である放熱について、Low-k 層

を保護するはんだ接合部の構造を提案する。それは、Low-k 層を利用できれば、 超高周波動作においても消費電力を抑制できるためである。次に、放熱をしや すくするための両面実装を提案する。それは、両面に実装を行い、片面あたり のチップ積層数を半減できれば、積層チップ構造に熱が蓄積しにくくなるため である。

さらに、三次元高密度実装構造の課題であるパッケージの厚さについて、接 合高さの低減を提案する。具体的には、銅の直接接合に着目し、はんだを使わ ないことで接合高さの低減を目指した。

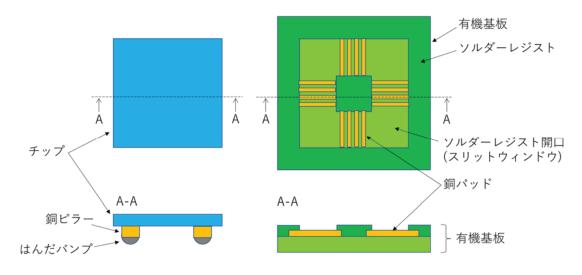

1.7 銅ピラーを用いた微細ピッチフリップチップ技術

本節では、本論文で利用した C2 (Chip Connection) 技術[24]を中心に、フリ ップチップ技術について述べる。

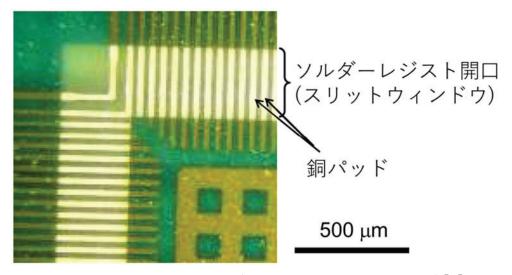

チップを有機パッケージ基板へと実装するには、50 μm 程度の微細なピッチ でのフリップチップ実装が求められる。そのような微細なピッチでのフリップ チップ実装を実現するには、チップ側に銅ピラー/はんだバンプ構造を形成し、 基板側にスリットウィンドウ状のソルダーレジスト開口を設けることが多い [24,35]。これらの構造を図 1.9 に示す。ソルダーレジストとは、パッド表面で のはんだ(ソルダー)の流れを防ぐ(レジスト)ための材料であり、パッケージ 基板の最表面に用いられる。

実装工程としては、無洗浄フラックス・リフロー・後入れアンダーフィル (Capillary underfill, CUF)の組み合わせを用いた工法[24]や、Nonconductive paste (NCP)などと組み合わせた Thermal compression bonding (TCB)により、 はんだ接合とアンダーフィルとを一括して行う工法[36]が一般的である。これ らの工法の概略を図 1.10と図 1.11に示す。本論文では、銅の直接接合について、 はんだの利用の有無にかかわらず適用できる TCB を用いた。また、はんだを用 いた接合については、多数のパッケージをリフローで同時に接合できるという 意味で生産性が高い、IBM が開発した C2 技術[24]を用いている。この技術で は、チップ側の銅については「ピラー」、有機基板側の銅については「パッド」 の語を用いて区別する。

図 1.9 微細ピッチフリップチップ向けのチップ・基板構造 左はチップ、右は基板。上は上面図、下は断面図。

図 1.10 無洗浄フラックス・リフロー・後入れアンダーフィルによる実装工法。 (a) パッケージ基板、(b)フラックス塗布、(c)塗布後の基板、(d)チップ搭載、 (e) リフローはんだ付け、(f)アンダーフィル塗布、(g)オーブンで硬化。

図 1.11 Nonconductive paste を用いた

Thermal compression bonding による実装工法。

(a)パッケージ基板、(b)NCP 塗布、(c)ボンダで位置合わせ、

(d)ボンダではんだ付け、(e)ボンダから取り出し、(f)オーブンで最終硬化。

#### 1.8 本論文の概要

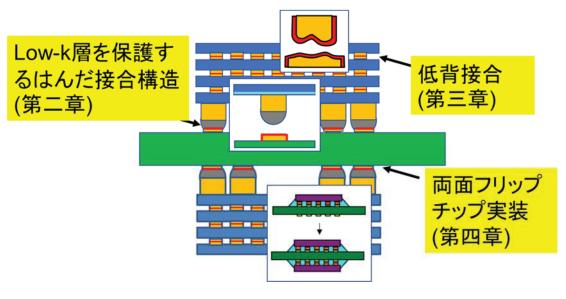

本論文の概要を図 1.12 に示す。

第一章「序論」では、超高周波用三次元高密度実装の必要性の背景、従来の 三次元積層化技術、及び後工程の要素技術の有効性とその課題を纏め、本研究 の目的について述べた。

第二章では、銅ピラーを用いたシリコンチップと有機基板間のフリップチップ接合において Low-k 層を保護できるよう、はんだ接合部形状を最適化する。

第三章では、シリコンチップ同士の接合において、銅の直接接合に着目した。 それは、高さ方向の集積化を実現する目的と、超高周波特性の向上を実現する 目的である。その手段として DIG を中間層に用いることを提案する。

第四章では、半導体実装構造全体の性能向上に求められるフリップチップ両 面実装において、DIG を含めた各種表面処理を提案し、最適な表面処理手法を 評価する。

第五章「結論と今後の展望」では、本研究の成果を総括し、今後の応用も含めた展望について述べる。

図 1.12 本論文の概要図

- 1.9 参考文献

- S. Dieter et al., "Towards the Implementation of IoT for Environmental Condition Monitoring in Homes," IEEE Sensors Journal 13, 3846 (2013).

- [2] K. Kibaroglu et al., "A Low-Cost Scalable 32-Element 28-GHz Phased Array Transceiver for 5G Communication Links Based on a 2 × 2 Beamformer Flip-Chip Unit Cell," IEEE Journal of Solid-State Circuits 53, 1260 (2018).

- [3] A. Islam et al., "Convolutional Neural Networkscheme-based Optical Camera Communication System for Intelligent Internet of Vehicles," International Journal of Distributed Sensor Networks 14, 1 (2018).

- [4] Y. Yu et al., "Optimization and Implementation of SIW Slot Array for Both Medium and Long Range 77GHz Automotive Radar Application," IEEE Transactions on Antennas and Propagation, in press (2018).

- [5] G. Moore, "Cramming More Components onto Integrated Circuits," Proceedings of the IEEE 86, 82 (1998).

- [6] T. N. Theis et al., "The End of Moore's Law: A New Beginning for Information Technology," Computing in Science & Engineering 19, 41 (2017).

- [7] M. Koyanagi et al., "Future System-on-Silicon LSI chips," IEEE Micro 18, 17 (1998).

- [8] K. Sakuma et al., "3D Chip-Stacking Technology with Through-Silicon Vias and Low-Volume Lead-Free Interconnections," IBM Journal of Research and Development 52, 611 (2008).

- [9] J-S. Kim et al., "A 1.2 V 12.8 GB/s 2 Gb Mobile Wide-I/O DRAM With 4 × 128 I/Os Using TSV Based Stacking," IEEE J. Solid-State Circuits 47, 107 (2012).

- [10] K. Honda et al., "NCF for Pre-Applied Process in Higher Density Electronic Package Including 3D-Package," Proceedings of Electronic Components and Technology Conference, 385 (2012).

- [11] J. Warnock et al., "Circuit Design Techniques for a First-Generation Cell Broadband Engine Processor," IEEE Journal of Solid-State Circuits 41, 1692

(2006).

- [12] O. Takahashi et al., "Migration of Cell Broadband Engine from 65nm SOI to 45nm SOI," Proceedings of IEEE International Solid-State Circuits Conference, 86 (2008).

- [13] TechSearch International, "The Future of Packaging and Assembly Technology," https://www.smta.org/chapters/files/Central-Texas\_CTEAVardaman2016. pdf

- [14] S. Iyer et al., "Three-Dimensional Integration: A Tutorial for Designers," IEEE Solid-state circuits magazine 7, 63 (2015).

- [15] K. Matsumoto et al., "High Thermal Conductivity Underfill for the Thermal Management of Three-dimensional (3D) Chip Stacks," Proceedings of SEMI-THERM Symposium, 219 (2014).

- [16] T. Hamamoto et al., "A Floating-Body Cell Fully Compatible With 90-nm CMOS Technology Node for a 128-Mb SOI DRAM and Its Scalability," IEEE Transactions of Electron Devices 45, 1300 (1998).

- [17] A. P. Chandrakasan et al., "A 180-mV Subthreshold FFT Processor Using a Minimum Energy Design Methodology," IEEE Journal of Solid-state Circuits 27, 473 (1992).

- [18] K. M. Chen et al., "Copper Pillar Bump Design Optimization for Lead Free Flip-Chip Packaging," Journal of Materials Science: Materials in Electronics 21, 278 (2010).

- [19] J. Sylvestre et al., "The Impact of Process Parameters on the Fracture of Device Structures during Chip Joining on Organic Laminates," Proceedings of Electronic Components and Technology Conference, 82 (2008).

- [20] R. J. O. M. Hoofman et al., "Self-Aligned Multi-Level Air Gap Integration," Microelectronic Engineering 83, 2150 (2006).

- [21] A. Yoshida et al., "A Study on Package Stacking Process for Package-on-Package (PoP)," Proceedings of Electronic Components and Technology Conference, 825 (2006).

- [22] K. Y. Au et al., "3D Chip Stacking & Reliability Using TSV-Micro C4 Solder Interconnection," Proceedings of Electronic Components and Technology Conference, 1376 (2010).

- [23] K. Sakuma et al., "Fluxless Bonding Process Using Thermo-compression Micro-scrub for 61 μm Pitch SnAg Solder 3-D Interconnections," Proceedings of Electronic Components and Technology Conference, 329 (2016).

- [24] Y. Orii et al., "Micro Structure Observation and Reliability Behavior of Peripheral. Flip Chip Interconnections with Solder-Capped Cu Pillar Bumps," Transactions of the Japan Institute of Electronics Packaging 4, 73 (2011).

- [25] H. Ma et al., "Effect of Initial Cu Concentration on the IMC Size and Grain Aspect Ratio in Sn-xCu Solders during Multiple Reflows," Journal of Materials Science: Materials in Electronics 29, 602 (2018).

- [26] F. B. Kaufman et al., "Chemical Mechanical Polishing for Fabricating Patterned W Metal Features as Chip Interconnects," Journal of the Electrochemical Society 138, 3460 (1991).

- [27] T. Sakai et al., "A New Flip-Chip Bonding Method Using Ultra-Precision Cutting of Metal/Adhesive Layers," Journal of the Japan Institute of Electronics Packaging 11, 217 (2008).

- [28] K. Sakuma et al., "Fluxless Bonding for Fine-Pitch and Low-Volume Solder 3-D Interconnections," Proceedings of Electronic Components and Technology Conference, 7 (2011).

- [29] T. H. Kim et al., "Room Temperature Cu-Cu Direct Bonding Using Surface Activated Bonding Method," Journal of Vacuum Science & Technology A 21, 449 (2003).

- [30] S. Hashimoto et al., "Direct Immersion Gold (DIG) as a Final Finish," Circuit World 32, 16 (2006).

- [31] K. Yokomine et al., "Development of Electroless Ni/Au Plated Build-up Flip Chip Package with Highly Reliable Solder Joints," Proceedings of

Electronic Components and Technology Conference, 1384 (2001).

- [32] D. Kin et al., "Evaluation of DIG (Direct Immersion Gold) as a New Surface Finishes for Mobile Applications," Proceedings of Electronic Components and Technology Conference, 258 (2006).

- [33] C. Ryu et al., "Novel Approaches to Current BGA Packaging Challenges," Proceedings of Electronics Packaging Technology Conference, 1258 (2008).

- [34] H. Noma et al., "Flip Chip Assembly on 50-µm-pitch Pads Soldered with Precoat by Powder Sheet," Proceedings of International Conference on Electronics Packaging, 386 (2009).

- [35] T. Wang et al., "Studies on a Novel Flip-Chip Interconnect Structure Pillar Bump," Proceedings of Electronic Components and Technology Conference, (2001).

- [36] Y. Shimote et al, "The Fine Pitch Cu-pillar Bump Interconnect Technology Utilizing NCP Resin, Achieving the High Quality and Reliability," Transactions of the Japan Institute of Electronics Packaging 7, 87 (2014).

# 第二章 ダイレクト金めっきを用いた低応力接合

半導体チップを有機基板へとリフロー工法で実装する際、チップの動作周波 数を向上させるために使われる Low-k 層を保護することは重要である。その目 的で、チップ側の銅ピラーなどの設計寸法やリフローの温度プロファイルとい う工程条件を最適化した例が存在する。

しかし、究極的な Low-k 層であるエア・ギャップ技術を用いるには依然とし て技術開発が必要である。そこで、はんだ形状を最適化することで Low-k 層へ の応力を低減できるのではないかとの仮説を立て、はんだの基板側のパッドへ の濡れ性を最適化することを提案した。その手段として基板側の銅パッドを DIG で表面処理することに着目した。それは、パッド表面を金というはんだが 濡れやすい材料にできることと、Ni/Au めっきのようにパッド側面に余分なニ ッケル層を形成することなくパッド表面を金にすることができることが理由で ある。

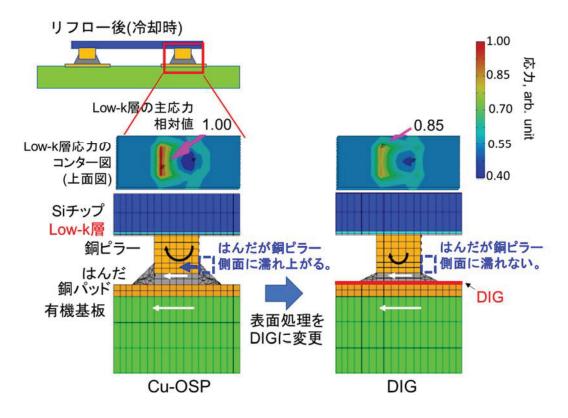

実験から、仮説通り、DIG においては OSP の場合とは異なりはんだが銅パッ ド上に広く濡れ広がり、結果としてはんだ接合部周辺に残るはんだ体積が減る ことがわかった。この結果に基づき有限要素法で構造解析を行い、接合部周辺 のはんだ体積が少ない方が Low-k 層への応力が小さくなることがわかった。そ れは、リフロー後の冷却時に銅ピラー側面がはんだにより押される力が小さく なるためと考えられる。ここから、基板側パッドの表面処理が DIG の場合、OSP の場合と同じ信頼性を保つという条件では、より誘電率の低い Low-k 層を使え、 より高周波でチップを動作できることを見出した。

なお、本章の図表で[1, 2]から転載しているものの著作権は、© 2011 The Japan Institute of Electronics Packaging である。

2.1 緒言

本章では、はんだ形状を最適化しリフロー後冷却時に Low-k 層を保護するこ とを提案する[1, 2]。フリップチップ実装には C2 技術を用いた。パッドの表面 処理には、50 µm の微細ピッチパッドに適用できる OSP および DIG を用い比 較考察した。

先ず、はんだ接合部形状のはんだの基板側銅パッド表面への濡れ依存性を明 らかにするための数値計算を実施した。次に、リフロー後冷却時の信頼性のは んだ接合部形状依存性を明らかにするための構造解析を実施した。解析に当た り、CPI (Chip package interaction)が最先端の実装技術開発における課題であ るため、はんだ接合部の歪みだけでなく Low-k 層に加わる応力も解析した。

2.2 実験および数値計算

2.2.1 基板上のパッド表面へのはんだ濡れ性

リフロー中にはんだがどのように濡れるかを調べるため、OSP および DIG の 表面処理のパッドについて実装を行った。

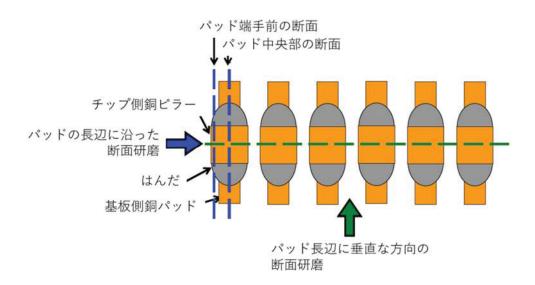

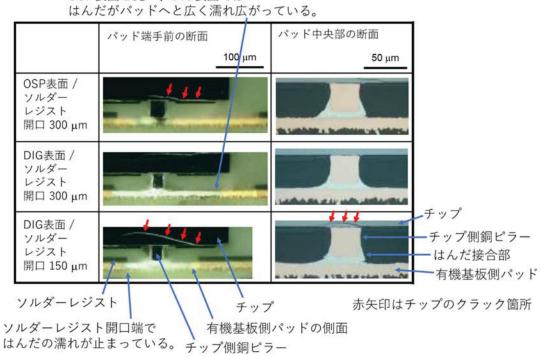

DIG の厚さは、有機基板から水分を除くプリベーク工程の熱がかかって、金 が銅の中へ拡散しても表面に金が残るように 0.06 µm とした[3, 4]。図 2.1 に示 す 50 µm ピッチの TV (Test vehicle)を実験に用いた。TV とは、評価用のチッ プおよび基板を組み合わせた総称である。基板側の銅パッドの幅は 25 µm であ る。ソルダーレジストの開口長さは 300 µm と 150 µm の二種類とした。開口長 さを 300 µm にすると、ソルダーレジスト開口の端がチップの外側になるため、 後入れアンダーフィルを導入しやすくなる。開口長さ 150 µm の場合、はんだが パッドへ過剰に濡れてもソルダーレジスト開口の端で止まる。チップ側の銅ピ ラーのサイズは 35 µm 角で、その上に形成したはんだの高さは 20 µm である[5]。

TV 基板に無洗浄フラックスを塗布し、そこに TV チップを搭載したうえで、 窒素雰囲気下のリフロー炉に投入した。図 2.2 に示した箇所でのはんだ接合部形 状を把握するため光学顕微鏡による断面観察を行った。パッドの長さ方向に対 して垂直方向と水平方向の両方の断面を観察した。

図 2.1 TV 基板の拡大図 (チップの角に対応する部分)[2]

図 2.2 光学顕微鏡による断面観察箇所の上面図[2]

2.2.2 はんだ接合部形状の数値計算

はんだ接合部形状を理論的に議論する目的で、Surface Evolver という広く使われているソフトを用いて形状を計算した[6,7]。この手法では、定常状態での はんだ形状を得ることができる。また、リフロー中のはんだ形状の動的な変化 を計算した報告例[8]もある。

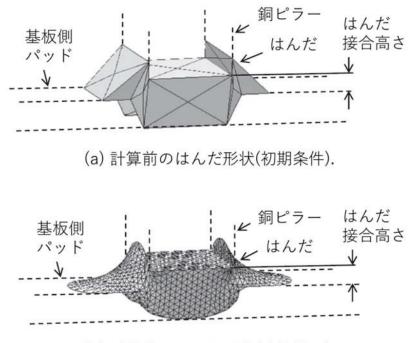

しかし、本提案では、はんだが固化した後の冷却時に Low-k にかかる応力を 求めることが重要と考えている。 計算前のはんだ接合部形状を図 2.3(a)に示す。銅ピラーの二面にはんだが濡 れ上がった形状を初期状態として設定した。はんだ形状を、表面エネルギーや 重力のポテンシャルエネルギーが最適化されるように変形し、図 2.3(b)の結果 を得た。表面エネルギーの計算は式 2.1 に示すラプラスの式を用いた。

$$\Delta p = \gamma \left( \frac{1}{R_1} + \frac{1}{R_2} \right) \tag{2.1}$$

ただし、 $\Delta p$ は、はんだ内外の圧力差、 $\gamma$ は、はんだの表面張力、 $R_1 \ge R_2$ は はんだ外形の主曲率半径つまり主曲率の逆数である。ここで、はんだの表面張 力 $\gamma$ には、Sn-3.5Agの値である 0.53 N/m を用いた[9]。

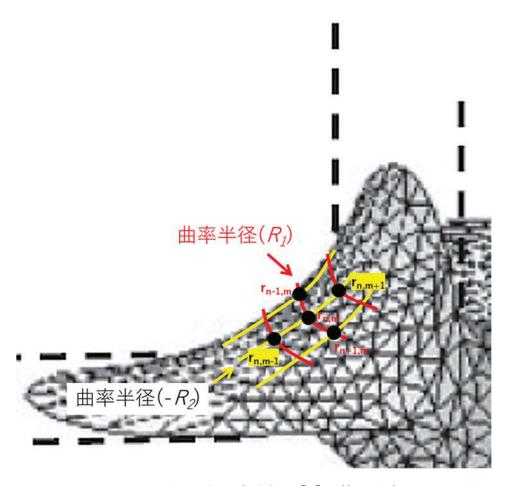

また、 $R_1 \ge R_2$ について、図 2.4 を用いて説明する。主曲率とは、計算対象の 点  $r_{n,m}$ を通る曲面の断面のうち、曲率が最大のものと最小のものである。図 2.4 を例に取れば、点  $r_{n,m} \ge \mathcal{E}$ の近傍の点  $r_{n-1,m} \ge r_{n+1,m}$ を通る円の曲率半径が ( $R_l$ )、 点  $r_{n,m} \ge \mathcal{E}$ の近傍の点  $r_{n,m-1} \ge r_{n,m+1}$ を通る円の曲率半径が ( $-R_2$ ) である。ここで、 円の中心がはんだの外側にあるため、 $R_2$ に負号を付けた。C4 (Controlled collapse chip connection) 技術で形成されるバレル型のはんだ形状についての 計算法が永田らにより提案されており、式 2.1 を用いた計算手法も詳述されてい る[10]。

なお、上記の計算では、チップや基板の位置を固定したため、はんだ接合高 さも固定されている。つまり、はんだ接合高さは別の手段で最適化する必要が ある。そこで、表面エネルギーや重力のポテンシャルエネルギーが最適となる はんだ接合高さを求めるために、3 μm から 9 μm のさまざまなはんだ接合高さ の条件で計算を実施した。

なお、上記以外の範囲において、計算結果は収束しなかった。それは、9 μm を超す範囲ではチップと基板のギャップが広くなりすぎてチップ側銅ピラーの 底面にはんだが存在しない箇所が生じてしまうためである。

(b) 計算後のはんだ形状(計算結果).

図 2.3 はんだ形状計算結果。表面処理は OSP で、はんだ接合高さは 9 µm。 (a)初期条件。はんだ表面は平面の組み合わせ。

(b)計算結果。ラプラスの式を解き、表面形状が収束した状態。[1]

図 2.4 曲面上の主曲率半径。[1]を基に改変。

2.2.3 低誘電率層への応力解析

はんだ接合部の歪みおよび Low-k 層の応力を調べる目的で、はんだ形状計算 と並行して有限要素法 (Finite Element Method, FEM) による構造解析を行っ た。解析結果に特異点が生じる問題を避けるため、はんだ内の歪みは体積平均 で求めた[11]。Low-k 層は薄いため、理想的な立方体形状と比べ、メッシュの アスペクト比が大幅に高くなっている。この場合、メッシュの最適化[12]を行 うことが望ましいものの、平面状のメッシュ形状であっても応力の相対値は正 しいと仮定した。構造解析に用いた材料特性を表 2.1 にまとめて示す[13, 14]。

| 材料               | 弾性率, GPa | 熱 膨 張 係 数 (CTE), |

|------------------|----------|------------------|

|                  |          | ppm/K            |

| Si               | 130      | 3.2              |

| SiO <sub>2</sub> | 66       | 5.7              |

| Cu               | 117      | 16.6             |

| 有機基板[13]         | 24.9     | 15.0             |

表 2.1 構造解析に用いた機械特性一覧[1]

(a) はんだ以外の、弾性解析を用いた材料

(b) はんだ材料のノートン則 $d\varepsilon / dt = A\sigma^n$ の温度ごとの定数[14]。

|--|

| 材料、温度                    | n    | <i>A</i> , MPa/h       |

|--------------------------|------|------------------------|

| Sn-3.5Cu-0.75Ag ( 20 °C) | 11.1 | $1.12 \times 10^{-17}$ |

| Sn-3.5Cu-0.75Ag (80 °C)  | 9.0  | 8.09×10 <sup>-15</sup> |

| Sn-3.5Cu-0.75Ag (140 °C) | 6.8  | 8.64×10 <sup>-13</sup> |

はんだについてはノートン則によるクリープ解析を実施し、その他の材料に ついては弾性を想定した。CTE ミスマッチによるはんだの歪みや Low-k 層の応 力は剪断変位を与えることによって求めた。その変位の大きさは、式 2.2 のよう に 6.9 µm となる。

$$\left(\frac{CS}{2}\right) \times \Delta CTE \times \Delta T$$

$$= \left(\frac{7.3 \ mm}{2}\right) \times (15 \ ppm/K - 3.2 \ ppm/K) \times \left(185 \ ^{\circ}\text{C} - 25 \ ^{\circ}\text{C}\right)$$

$$= 6.9 \ \mu\text{m}$$

(2.2)

ただし、*CS*はチップサイズ、Δ*CTE*はチップと有機基板の CTE 差、Δ*T*は、 リフロー時のはんだ凝固温度から室温までの温度差である。ここで、はんだ凝 固温度は185 ℃を仮定している[15]。

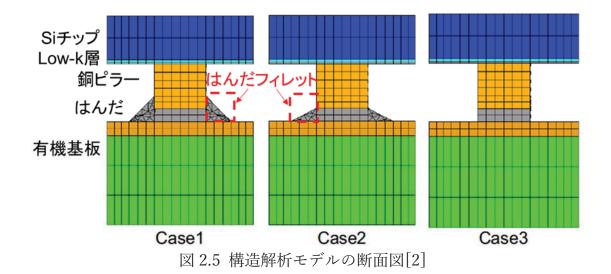

はんだ形状を図 2.5 に示す三つの場合について解析した。ここで、接合部のは んだのうち、銅ピラー真下からはみ出ている部分をはんだのフィレットと定義 する。第一のケースは、はんだが銅パッドだけでなく銅ピラーの側面に濡れて 大きなフィレットを形成した場合である。第二のケースは、はんだが銅パッド に濡れて銅ピラーの側面には濡れ上がらず小さなフィレットを形成した場合で ある。第三のケースは、はんだが銅ピラーの真下の箇所にしか濡れず、フィレ ットが形成されなかった場合である。

2.3 結果と考察

2.3.1 ダイレクト金めっきによる、はんだの基板側銅パッドへの濡れ改善

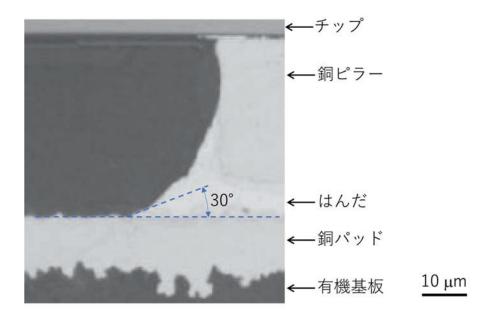

図 2.6~2.8 にはんだ接合部の断面写真を示す。図 2.7 は、図 2.6 のうち OSP 処理についてパッド中央部の断面を拡大した写真である。銅パッド表面でのはんだの濡れ角は OSP 処理の場合に 30°となった。他の研究[16,17]でははんだの銅への濡れ角が銅への表面処理やフラックスの条件に依存して大きくばらついている。はんだボールと銅板を磨き洗浄することで表面の酸化膜を取り除き、アルゴン雰囲気下フラックスなしで加熱した場合、溶融したはんだの銅板への濡れ角は約 50°であった[16]。

一方、はんだボールを、磨き洗浄された銅板へ置いてロジン系(Rosin Mildly Activated, RMA)フラックスを用いて大気雰囲気下で加熱した場合は、はんだの銅表面への接触角が約20°であった[17]。ロジン系フラックスは、無洗浄フラックスよりも活性が高いものの、リフロー後に洗浄が必要である。

本章の実験においては、活性の弱い無洗浄フラックスを用い、OSP 表面の銅 上にはんだを配置し窒素雰囲気下でリフローした。そのため、実験結果として 得た濡れ角 30°は妥当である。なお、チップにクラックが入っているのは、断面 研磨時の応力に起因するものである。

OSP表面と比べ、DIG表面では

図 2.6 実装後の断面写真(パッドの長辺に沿った断面研磨)。[2]を基に改変。

図 2.7 OSP 表面の場合の、はんだの接触角。[1]を基に改変。

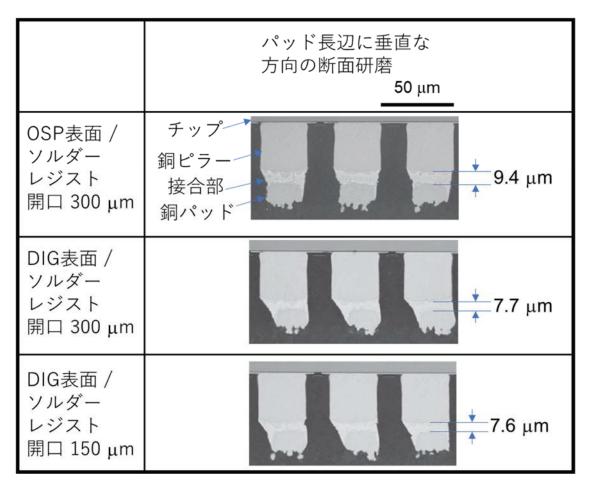

図 2.8 実装後の断面写真(パッドの長辺に垂直な断面研磨)。[1]を基に改変。

基板上の DIG 表面のパッドへははんだが広く濡れ広がった。濡れ広がったは んだの厚みは非常に薄く、halo[18]のように見えた。ここで halo とは、はんだ が元々存在した箇所から薄く広く濡れ広がり、外周部にまで光沢が見える現象 である。過剰にはんだが濡れ広がった領域でのはんだの厚みは非常に薄いが、 OSP サンプルと比べ、DIG サンプルでは銅ピラー周辺に残るはんだ体積は少な い。そのような濡れ広がりは Ni/Au めっき処理をしたライン状のパッドにおい ても報告されている[19]。

しかし、Ni/Au めっきにおける金の下地がニッケルであるのに対し、DIG に おける金の下地が銅であるため、濡れの度合いが異なる。銅のスズへの拡散係 数  $(5 \times 10^{-11} \text{ m}^2/\text{s})$ がニッケルのスズへの拡散係数  $(2 \times 10^{-12} \text{ m}^2/\text{s})$ よりも大き いため、はんだの DIG 表面への濡れは Ni/Au めっきの場合よりも軽微である [20]。DIG の場合、Ni/Au めっきの場合よりも、IMC を形成するために多くの はんだが消費され、パッドへと濡れ広がるはんだの量が少なくなるためである。

IMC 形成量については、C2 技術において銅ピラーをニッケルピラーに置き換 えて評価した結果、銅ピラーよりニッケルピラーの方がリフロー後のピラー表 面での IMC 厚さが薄いとの報告がある[21]。そのことが、DIG パッド上へのは んだの濡れが halo のように観察され、過剰なはんだの濡れが抑制されることの 原因である。

2.3.2 界面合金層形成による、はんだ接合高さの制限

OSP 表面について図 2.7 から得た接触角を基にはんだ形状の計算を行った。 その結果図 2.9 に示すように実験結果のはんだ形状と合致していることが確認 された。

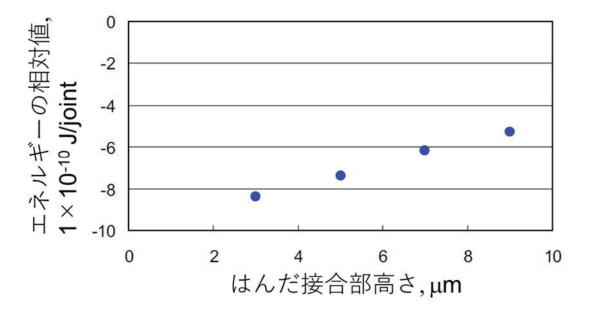

計算範囲の中では、図 2.10 に示すように、はんだ接合部高さが 3 µm のとき に最もエネルギーが安定になるとわかった。この計算結果は図 2.8 に示した実験 結果とは一致していない。実験では、はんだ接合部高さは 9 µm であった。この 条件の場合、数値計算上でエネルギーが不安定であった。この原因は、IMC 成 長に起因しているのではないかと考察した。

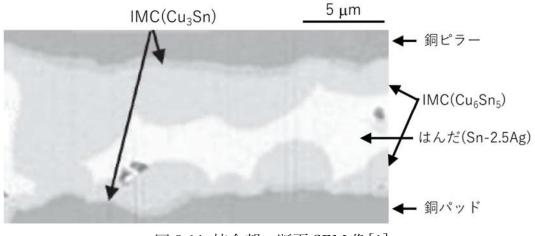

IMC の SEM 像を図 2.11 に示す。Cu<sub>5</sub>Sn<sub>6</sub> は凹凸のある形状をしていて、チッ プ側には大きな IMC も存在する。それは、はんだバンプ形成時にめっき後のは んだに金属光沢を持たせると同時に形状を半球状にするためのリフロー工程が 必要であるためである[22]。フリップチップのリフロー時にチップ側のピラー 上に形成された IMC と基板側のパッド上に形成された IMC とが接触する箇所 があり、その IMC が接合高さを計算で求まる安定な高さ(3  $\mu$ m 以下)よりも大 きくなる原因である。

32

図 2.9 はんだ形状計算結果(各メッシュの点を青でプロット)。 [2]を基に改変。

図 2.10 接合部の相対エネルギー(重力と表面張力)の接合部高さ依存。 ボンディング前のエネルギーを0と設定。[2]

図 2.11 接合部の断面 SEM 像[1]

2.3.3 ダイレクト金めっきによる低誘電率層への応力低減

図 2.12 および表 2.2 に構造解析の結果をまとめた。はんだにかかる歪み、 Low-k 層への応力それぞれについて、第一のケースを 1.00 として相対的な比率 を記載している。はんだ体積が減ると、はんだにかかる歪みが大きくなること は、他の報告と同様の傾向である[23]。一方、Low-k 層への応力は、はんだ体 積が小さくなると低減した。その理由は、はんだフィレットが銅ピラーの側面 を引っ張る力が、第一のケースには存在する一方で他のケースでは存在しない ためと考えられる。

表面処理として OSP を想定した第一のケースから、DIG を想定した第二のケ ースへと、はんだの濡れ状態を変えることにより、Low-k 層への応力は 15%低 減した。これは、信頼性を維持したまま、より誘電率の低い材料を使えること を意味する。ここで、応力が 15%減ったときに誘電率が 15%低い材料を使えた と仮定すると、第一章の式 1.1 からわかるように消費電力を維持したままで 18% 高い動作周波数を実現できる。

34

図 2.12 構造解析結果(Low-k 層応力のコンター図)。 左上に載せたリフロー後の断面の、右側の接合部(赤囲み)の解析。 上から二段目のコンター図は、Low-k 層応力分布の上面図。

下段は、左上図の赤囲み部の拡大図。

下段図中の矢印はリフロー後冷却時にかかる歪み方向。[2]を基に改変。

|             | Case1 | Case2 | Case3 |

|-------------|-------|-------|-------|

| Low-k層の主応力  | 1.00  | 0.85  | 0.71  |

| (最大値)       |       |       |       |

| Case1=1.00  |       |       |       |

| はんだの Von    | 1.00  | 1.08  | 1.11  |

| Mises クリープ歪 |       |       |       |

| み (体積平均)    |       |       |       |

| Case1=1.00  |       |       |       |

表 2.2 構造解析結果 (Low-k 層応力およびはんだ接合部の歪み)[1]

C2 技術によるはんだ接合部の温度サイクル (Temperature cycle, TC) 信頼 性は、チップ側に金スタッドバンプを有機基板側にはんだがプリコートされた パッドを用いた場合と比べ良好である[5]。それは、金とスズとの IMC 形成に 起因するカーケンダルボイドが生じず、接合部の電気抵抗上昇が少ないためで ある。はんだ体積が少ないと、基板の反りに起因するはんだの濡れ不良が生じ る可能性がある[24, 25]。はんだ接合部の信頼性や濡れ不良の可能性を考慮すべ きであり、はんだ体積を減らすのでなく、はんだのパッドへの濡れ性を高める ことは、Low-k 層への応力を減らす解となる。

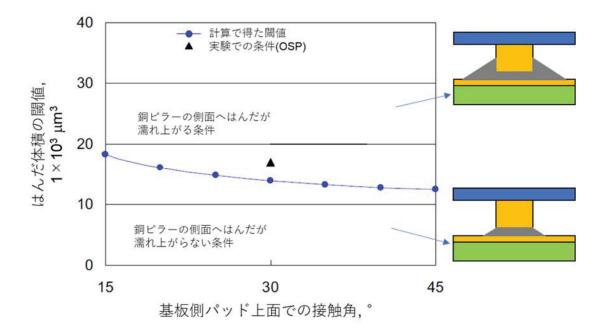

2.3.4 銅ピラーの側面にはんだが濡れ上がる閾値のはんだ体積

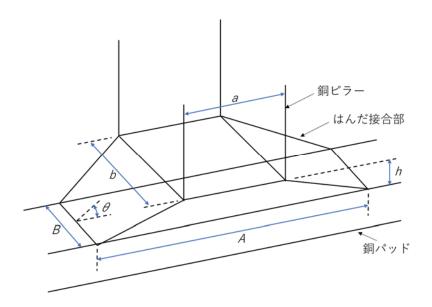

銅ピラーの側面にはんだが濡れ上がらないことは Low-k 層の保護に役立つ。 そこで、用いた TV について銅ピラーの側面にはんだが濡れ上がる閾値のはん だ体積を求めた。はんだ接合部高さは IMC 形成により制限されるため 9 μm に 固定した。

銅ピラーの側面にはんだが濡れ上がるには、はんだ体積が、ピラーの底面と パッドの上面のうちはんだが濡れた箇所とで形成される六面体(図 2.13)の体 積を上回る必要がある。図 2.13 においてははんだは銅ピラーの側面に濡れ上が っていない。はんだ体積がこれよりも大きければその分のはんだが銅ピラーの 側面へと濡れ上がると仮定している。パッド上ではんだが濡れる箇所は接触角 から求めることができる。そのため、閾値体積 Vは、以下の式 2.3 で求める。

$$V = \left(\frac{h}{6}\right) \times \{Ab + aB + 2(ab + AB)\}$$

(2.3*a*)

$$A = a + 2 \times \left(\frac{h}{\tan\theta}\right) \tag{2.3b}$$

ここでhははんだ接合部高さで、a,bはチップ側銅ピラーの辺の長さである。 Aは基板側パッドのうちはんだが濡れた箇所の長さ、Bは基板側パッドの幅、 $\theta$ は接触角である。

図 2.13 はんだ体積閾値でのはんだ接合部形状の模式図

計算結果として得た閾値を図 2.14 の曲線に示した。また、実験でのはんだ体 積を図 2.14 中に三角で記入した。はんだ体積は閾値 Vを超えていて、チップ側 銅ピラーの側面へと濡れ上がっている。このことは計算結果と一致している。 単にはんだ体積を減らすだけでなく、接触角を減らすこともはんだの銅ピラー への濡れ上がりを抑制するのに有効である。

金は銅の中へと拡散しやすいことが知られている[26]。しかし、第四章で述 べるように、リフロー前に金がパッド表面で 0.06 μm 以上残っていれば、実装 は可能である[3, 4]。基板側に DIG 表面のパッドを形成することは、単にリフ ローで実装される SMT (Surface mount technology) 部品との混載に役立つだけ でなく、CPI の改善にも役立つ。そのため、同じ信頼性であれば、前項で述べ たように、より誘電率の低い Low-k 層を用いることにより更なる高周波でチッ プを動作させることができる。

図 2.14 はんだのチップ側銅ピラーへの濡れ上がりの閾値。[2]を基に改変。

2.4 結言

Low-k層への応力を低減する目的で、パッドに DIG が表面処理された基板へ C2 技術によりチップを実装した。数値計算によりはんだ形状を議論し、構造解 析によりはんだ形状が信頼性に与える影響を評価した。その結果、以下の知見 が得られた。

- (1) DIG 表面処理では、はんだがパッド上で広く濡れるため、チップ側銅ピラー 周辺のはんだ体積は OSP の場合と比べ少なくなる。

- (2) チップ側銅ピラー周辺のはんだフィレット形成を最低限にすることが、 Low-k 層を保護する上で重要である。

- (3)はんだフィレット形成を抑制するには、微細ピッチに適した DIG によりパ ッド上へのはんだの濡れ角を低減することが有効である。

同じ信頼性であれば、より誘電率の低い Low-k 層を用い、更なる高周波でチ ップを動作できる。具体的に、本章で示したケースについては従来よりも 18% 高い周波数でのチップ動作が可能となる。

っまり、DIG は、ニッケルバリア層を介さずに微細なピッチの銅パッドへ金 表面処理ができるため、CPI 改善、さらには、高周波化の観点から重要な技術 である。

- 2.5 参考文献

- [1] H. Noma et al., "Peripheral Flip Chip Interconnection on Au Plated Pads Using Solder-Capped Cu Pillar Bumps," Transactions of the Japan Institute of Electronics Packaging 4, 95 (2011).

- [2] H. Noma et al., "C2 (Chip Connection) Assembly on Gold Plated Pads," Proceedings of International Conference of Electronics Packaging, 499 (2011).

- [3] H. Noma et al., "Wettability and Reliability for Double-Sided Assembly with Chip Connection (C2) Flip-Chip Technology," Transactions of the Japan Institute of Electronics Packaging 2, 85 (2009).

- [4] H. Noma et al., "Wettability and Reliability on Double Side Assembly with Metal Post Solder - Chip Connection Flip Chip Technology," Proceedings of International Conference on Electronics Packaging, 568 (2009).

- [5] Y.Orii et al., "Micro Structure Observation and Reliability Behavior of Peripheral Flip Chip Interconnections with Solder-Capped Cu Pillar Bumps," Transactions of the Japan Institute of Electronics Packaging 4, 73 (2011).

- [6] K. A. Brakke, "The Surface Evolver," Experimental Mathematics 1, 141 (1992).

- [7] S. C. Tower et al., "Yield Prediction for Flip-Chip Solder Assemblies Based on Solder Shape Modeling," IEEE Transactions on Electronics Packaging Manufacturing 22, 29 (1999).

- [8] S. Shojiguchi et al., "Simulation of Solder Joint and Warping of LSI Packages," The Papers of Technical Meeting on Electronic Circuits, Institute of Electrical Engineers of Japan ECT-10-107, 17 (2010) (in Japanese).

- [9] I. Kaban et al., "Surface Tension and Density of Binary Lead and Lead-free Sn-based Solders," Journal of Physics: Condensed Matter 17, 7867 (2005).

- [10] T. Nagata et al., "Prediction of Solder Joint Geometries by Rigid-Plastic Flow Analysis," Proceedings of Microjoining and Assembly Technology in

Electronics, 521 (2002) (in Japanese).

- [11] R. Darveaux, "Effect of Simulation Methodology on Solder Joint Crack Growth Correlation and Fatigue Life Prediction," ASME Journal of Electronic Packaging 124, 147 (2002).

- [12] J. Yin et al., "Constrained Mesh Optimization on Boundary," Engineering with Computers 24, 231 (2008).

- [13] K. Okamoto et al., "Material Property Modeling by Using the Thermal Deformation Measurement System," Proceedings of International Conference on Electronics Packaging, 353 (2007).

- [14] Q. Yu, "Solder Joint Reliability Analysis of Assembled Components Using ANSYS," Mechanical CAE NEWS 3, 13 (2005) (in Japanese).

- [15] J. Sylvestre et al., "The Impact of Process Parameters on the Fracture of Device Structures During Chip Joining on Organic Laminates," Proceedings of Electronic Components and Technology Conference, 82 (2008).

- [16] X. R. Zhang et al., "Wetting Behavior and Interfacial Characteristic of Sn-Ag Solder alloy on Cu Substrate," Chinese Science Bulletin 55, 797 (2010).

- [17] M. F. Arenas et al., "Contact Angle Measurements of Sn-Ag and Sn-Cu Lead-Free Solders on Copper Substrates," Journal of Electronic Materials 33, 1452 (2004).

- [18] S. V. Sattiraju et al., "Wetting Characteristics of Pb-free Solder Alloys and PWB Finishes," IEEE Transactions on Electronics Packaging Manufacturing 25, 168 (2002).

- [19] R. Pendse et al., "Low Cost Flip Chip (LCFC): An Innovative Approach for Breakthrough Reduction in Flip Chip Package Cost," Proceedings of Electronic Components and Technology Conference, 1 (2010).

- [20] D. Toyoshima et al., "Influence of UBM Layers on Electro-migration Behavior of Micro-joints using Sn-Ag Solders," Proceedings of International Conference on Electronics Packaging, 548 (2011).

- [21] K. Toriyama et al., "Bump Structure Study for Fine Pitch Flip Chip

Interconnection," Proceedings of Microelectronics Symposium, 47 (2012) (in Japanese).

- [22] Y. Orii et al., "Solder Alloy Observation and its Reliability of Ultra Fine Pitch Peripheral Flip Chip Interconnection with Cu Post Bumps," Proceedings of Microjoining and Assembly Technology in Electronics Symposium, 59 (2011) (in Japanese).

- [23] R. D. Pendse et al., "Bond-on-Lead: A Novel Flip Chip Interconnection Technology for Fine Effective Pitch and High I/O Density," Proceedings of Electronic Components and Technology Conference, 16 (2006).

- [24] H. Noma et al., "Effects of Warpage and Underfill Material on Assembly and Reliability of System-in-Package," Microelectronics Symposium, 199 (2008) (in Japanese).

- [25] V. D. Khanna et al., "Methodology for Predicting C4 Non-Wets During the Chip Attach Process," Proceedings of Electronics Components and Technology Conference, 1117 (2010).

- [26] D.B. Butrymowicz et al., "Diffusion in Copper and Copper Alloys, Part II. Copper - Silver and Copper - Gold Systems," Journal of Physical and Chemical Reference Data 3, 527 (1974).

## 第三章 ダイレクト金めっきを用いたチップ間低背接合

超高周波用三次元高密度実装に必要となる銅の直接接合について、DIG を中 間層として用いる手法を提案する。従来は、試料表面の平坦化と、試料表面か らの銅酸化膜の除去が必須であった。

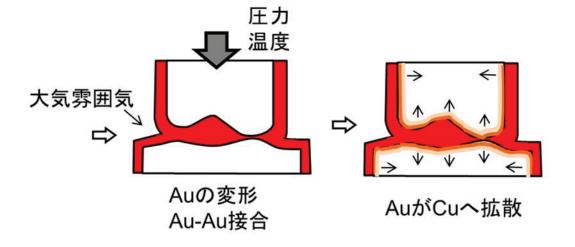

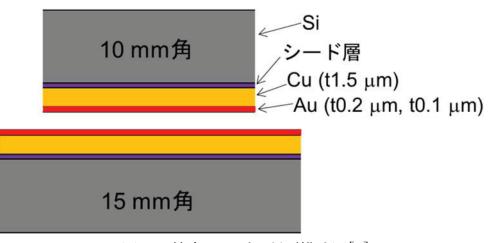

本章では、表面に銅よりも柔らかい金属である金を用いることができ、かつ 銅表面の酸化も抑止できる DIG を中間層として用いることを提案した。上側チ ップ・下側チップそれぞれ高さ 1.5 µm の平面状の銅上に厚さ 0.2 µm の DIG を 施したものを試料として用いた。上下チップの金表面同士を温度条件 350 ℃、 試料同士の加圧条件 10 MPa の、酸素を含む 1 atm の大気雰囲気下で接合した。

その結果、シェア試験ではシリコンのバルク破壊をし、透過電子顕微鏡観察 では界面に局所的なサイズ 0.2 µm のボイドがあるのみであった。DIG 後の表面 粗さ Rz は 0.4 µm であり、従来の銅の直接接合技術において必要とされていた ナノメートルレベルでの平坦性を必要としない接合工程である。

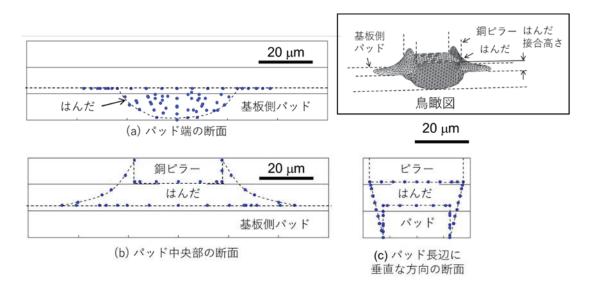

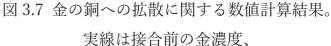

また、本工程ではニッケルやはんだも用いないため、接合高さを従来手法よ りも低くできる特長を持つ。本工程は以下の3つの段階に分けることができる。 第1段階では、加熱環境下で上下チップの銅上にある金同士が接触し、金が塑 性変形により表面粗さを吸収し平らにする。第2段階では、加熱・加圧環境下 で金同士が固相拡散接合を起こす。第3段階では、加熱環境下で金が銅の中へ と拡散し、擬似的な銅の直接接合が形成される。

第1段階で、厚さ 0.2 μm の DIG を施せば、Rz0.4 μm の表面粗さを吸収し、 接合できることが透過電子顕微鏡観察からわかった。これは、第1段階の塑性 変形が、第3段階での反応と比べ圧倒的に速く進むと考えることで説明できる。 表面粗さの凸の部分が、表面粗さの凹の部分へと全て移動すると、例えば表面 粗さ Rz の表面を平らにするにはその半分の厚さの DIG を用いれば良いためで ある。

本研究で実現した 3  $\mu$ m の接合高さは、従来のはんだリフロー工法では実現不可能なものである。また、この接合高さは、銅の厚さを薄くすることにより、 さらに低減できる。本章の図表のうち[1]から転載しているものの著作権は、© 2018 The Minerals, Metals & Materials Society である。 3.1 緒言

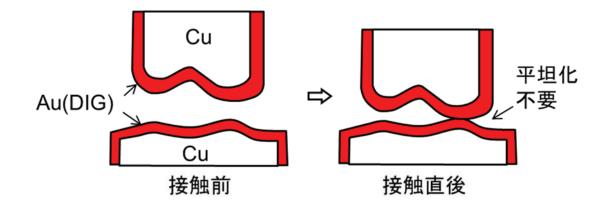

本章では、表面粗さを吸収できる柔らかい材料である金に着目した、新規か つシンプルな銅の直接接合の手法を提案する[1,2]。従来の手法よりも表面粗さ についてのプロセスウィンドウが広いため、DIG という単純なめっき工法が利 用できる。提案する手法が真空を必要としない点は、もう一つの利点である。

接合工程のコンセプトを図 3.1 に示す。DIG を銅上に形成し、金同士を接合 させる。本工程は以下の3つの段階に分けられる。第1の段階では、加熱環境 下で上下チップの銅上にある金同士が接触し、金が塑性変形により表面粗さを 吸収し平らにする。第2の段階では、加熱・加圧環境下で金同士が固相拡散接 合を起こす。第3の段階では、加熱環境下で金が銅の中へと拡散する。金薄膜 と銅バルクの界面反応がレビューされており[3]、そのデータが別の文献にまと められている[4]。その文献には、加熱温度 200 ℃、加熱時間 0.25 h から 25 h までの範囲での銅の深さ方向分布が掲載されている[4]。

他の研究では、200 ℃で4ヶ月や400 ℃で4日間の加熱を行った後の深さ方 向の元素分布が写真とともに示されている[5]。その写真では 10 µm の厚さの IMC 層が観察される。本章で提案するコンセプトにおける金の厚さは 10 µm よ り遙かに薄いため、必要とする接合時間は文献[5]よりも遙かに短いと考えられ る。上記工程において中間層の材料として金を選んだのは、柔らかく、酸化し にくく、かつ、銅と拡散する金属が、他にないためである。

金を中間層として導入するには、めっき、蒸着、スパッタなど多数の方法が ある。その中でも、めっきが最もシンプルな方法である。また銅表面の酸化膜 が金の膜形成の前に酸洗いによって除去されるため、その観点でもめっきが有 効である。めっきで銅の上に金を形成する場合、通常ニッケルがバリア層とし て用いられている。

しかし、本研究では、金を高速に銅の中へと拡散させて擬似的な銅の直接接 合を形成することを意図している。そのため、DIG という、バリア層でありか つ磁性体であるニッケルを用いないめっき手法を選択した。

金の中間層を用いた研究は複数存在する。島津らは、金を用いた原子拡散接 合を提案している[6]。しかし、その目的は銅の直接接合ではなかった。また、 Lim らは、銅へ直接金を形成し銅の直接接合を行っている[7]。その目的は単に 銅の表面の酸化を抑制することにあり、表面粗さを吸収することではなかった。 金の厚みは非常に薄く、接合は真空中で行われた。このように、従来の研究は、 本研究の主目的とする粗さの吸収を意図したものではない。

図 3.1 DIG を中間層として用いた銅の直接接合のコンセプト[1]

3.2 実験

3.2.1 評価用試料の準備

シリコンウエハ上のシード層へめっきされた銅の上に DIG を形成したサンプ ルを準備した。銅の厚さは 1.5  $\mu$ m、DIG の厚みは 0.2  $\mu$ m または 0.1  $\mu$ m である。 この場合、接合後の高さは約 3  $\mu$ m と薄くすることができる。なお、DIG の厚 み 0.2  $\mu$ m は、DIG において処理できる最も厚い条件である。接合サンプル断面 模式図を図 3.2 に示す。10 mm 角サンプルを 15 mm 角サンプルの上に載せ、加 熱・加圧の条件下でボンディングを行った。

3.2.2 ダイレクト金めっき前後の表面粗さ測定

AFM (Shimadzu SPM-9600) を用いて DIG 前後の表面粗さを定量的に把握 した。測定範囲は 10 μm×10 μm にした[8]。

3.2.3 接合手法

表 3.1 に接合条件を示す。接合には、SUSS MicroTec SB6e を用い、温度・時 間条件は先行研究[9]から引用した。圧力は先行研究[9]の 10 分の 1 である。な お、表中の圧力は、単純に接合時の荷重を 10 mm 角のサンプル面積 100 mm<sup>2</sup> で割って求めた値である。酸素存在下での VUV 照射(Vacuum ultra violet, USHIO UER 20-172)による表面洗浄を前処理として行った[9, 10]。この場合、 有機物のコンタミネーションは、酸素ラジカルや VUV 光により除去される。

図 3.2 接合サンプル断面模式図[1]

| 項目  | 条件                     |

|-----|------------------------|

| 温度  | 350 °C, 250 °C, 150 °C |

| 時間  | 900 s                  |

| 圧力  | 10 MPa                 |

| 雰囲気 | 大気 (0.10 MPa)          |

| 前処理 | 液体を使わずに有機物を除去          |

表 3.1 接合条件

3.2.4 シェア試験での破断モードによる接合強度評価

接合がどのように行われたかを調べる目的で、接合後にシェア試験を実施し、 破断モードでシェア強度を確認した。Royce650 (Royce Instruments)を試験に 用いた。シェアツールの速度は 50 μm/s とした[10]。

3.2.5 金の銅への拡散の評価方法

金と銅との分布を TEM-EDX により調べた。測定には JEOL 製の JEM-2011F と JED-2300 を用い、加速電圧を 200 kV とした。

3.3 結果と考察

3.3.1 ダイレクト金めっき前後の表面粗さ

図 3.3 に DIG 処理前後での AFM の結果を示す。表 3.2 に示すように、RMS や Rz は、0.2 µm の DIG 厚みのサンプルについて、それぞれ 46 nm と 424 nm であった。ここで、RMS は二乗平均粗さ、Rz は最大高さ粗さである。それぞれ の定義の模式図を図 3.4 に示す。

47

図 3.3 DIG 処理前後での AFM 結果。(a) DIG 前の銅表面、 (b) 0.1 μm 厚さの DIG 処理後、(c) 0.2 μm 厚さの DIG 処理後。[1]

図 3.4 Rz と RMS の定義(x は面内方向の距離。z は高さ。L は測定長さ)

| 試料        | 表面粗さ  |        |

|-----------|-------|--------|

|           | RMS   | Rz     |

| DIG 前の銅   | 51 nm | 402 nm |

| DIG0.1 µm | 38 nm | 309 nm |

| DIG0.2 µm | 46 nm | 424 nm |

表 3.2 表面粗さの測定値[1]

3.3.2 シェア試験での破断モードの接合温度依存

表 3.3 はシェアテストでの破断モードをまとめたものである。

接合温度 350 ℃では、0.2 µm、0.1 µm の DIG 厚さともに、破断モードはシ リコンの凝集破壊であった。このような良好な接合が文献の 10 分の 1 の圧力で も実現できたのは、金がこの温度では十分に柔らかかったためである[11, 12]。 対照的に、250 ℃や 150 ℃で接合したサンプルは金同士の界面での剥離が見ら れた。これは、表面粗さや前処理の条件が良好な接合を得るには不十分であっ たためと考えられる。なお、250 ℃と 150 ℃の条件では、DIG 厚さ 0.2 µm の 場合に金同士の界面剥離が生じたため、厚さ 0.1 µm の条件で測定を行った結果 については評価する必要がないと判断した。

| 接合温度   | 金の厚み      |           |

|--------|-----------|-----------|

|        | 0.2 μm    | 0.1 μm    |

| 350 °C | シリコンの凝集破壊 | シリコンの凝集破壊 |

| 250 °C | 金同士の界面剥離  | 評価せず      |

| 150 °C | 金同士の界面剥離  | 評価せず      |

表 3.3 シェア試験での破断モード[1]

3.3.3 接合後試料の断面観察による接合状態評価

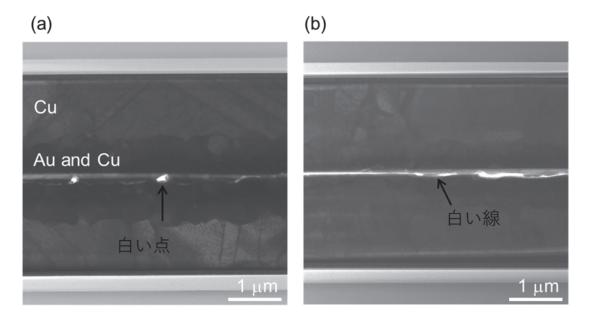

図 3.5 は接合後のサンプルで金の銅への拡散を TEM-EDX での元素マッピン グ像により調べたものである。

図 3.6 は 0.2 µm および 0.1 µm 厚さの DIG サンプルを 350 °Cで接合した後の TEM 断面を示したものである。0.1 µm 厚さのサンプルについては接合部に白い 線が観察され、接合が不十分であることがわかった。この結果は図 3.5(c), (d) の観察結果と一致するものである。図 3.5(a), (b)においても界面に暗い部分が観 察されるものの、図 3.6 で白く見える領域が白線ではなく局所的なサイズ 0.2 µm の点であるため、0.2 µm 厚さのサンプルの接合状態は 0.1 µm 厚さのサンプルの 接合状態よりも接合面積が広く良好であると考えられる。

3.3.4 ダイレクト金めっきによる低背接合の実現

図 3.6(a)から、接合高さが 3  $\mu$ m と、はんだリフローでは実現不可能な低さで あることがわかる。はんだリフローの場合、一度のリフローではんだと銅が接触する界面の片側で 2  $\mu$ m ずつ IMC が形成される[13]ため、接合の両側に IMC ができることを考えると、はんだ部分だけで接合高さが少なくとも 4  $\mu$ m になる ためである。さらに、本提案手法で銅の厚みを薄くすることにより接合高さを さらに低くすることが可能である。

50

図 3.6 接合後断面の TEM 像。(a) DIG t0.2 µm、(b) DIG t0.1 µm。[1]

3.3.5 金の銅への拡散係数の算出

金と銅との拡散についてのレビュー論文があり[3]、接合温度 350 ℃での拡散 係数 Dの値は 10<sup>-17</sup> m<sup>2</sup>/s から 10<sup>-15</sup> m<sup>2</sup>/s まで広くばらついている。本研究の系に おいても上記の拡散係数が適切かを調べる目的で、数値計算を行った。拡散方 程式を式 3.1 に基づいて数値的に解くにあたり、拡散係数をパラメーターとした フィッティングを行い、本研究の系での拡散係数を算出した。

$$\frac{\partial c}{\partial t} = D \, \frac{\partial^2 c}{\partial x^2} \tag{3.1}$$

ここで *c* は定数、*t* は時間、*x* は距離、*D* は拡散係数である。計算には差分法を 用い、空間刻みと時間刻みはそれぞれ 0.02 μm、1 s とした。境界条件としては、 金の拡散がバリア層と銅との界面で止まるという条件を用いた。

接合温度 350 ℃、900 s 後での金の分布を図 3.7 に示す。TEM-EDX で求めた 金の分布を、同じグラフに示した。図 3.7(a), (b)から求まった拡散係数はそれぞ れ 1.0×10<sup>-16</sup> m<sup>2</sup>/s、8.3×10<sup>-17</sup> m<sup>2</sup>/s であり、文献[3]の保持温度 350 ℃での値の 範囲内に入っていることから、拡散係数は適切であると考えた。このことから、 金が初期状態から、接合を経て銅の中へと拡散し、接合界面の元素の分布がな だらかになっていることがわかる。

点線はフィッティングにより求めた拡散係数での接合後の金濃度。

(a)は DIG t0.2 μm サンプル (拡散係数 1.0×10<sup>-16</sup> m<sup>2</sup>/s)、

(b)は DIG t0.1 µm サンプル(拡散係数 8.3×10<sup>-17</sup> m<sup>2</sup>/s)。[1]

3.3.6 表面粗さの吸収に必要なダイレクト金めっき厚さ

表 3.2 と図 3.6 の結果から、接合は金の厚みが Rz の半分以上のときに達成されることがわかった。

一方、Rzの半分よりも金の厚さが薄いときは、接合は不十分であった。この 点について以下に考察する。接合は表面凸部の金が凹部へと移動することによ り実現される。ここで、金の降伏強度が接合温度 350 ℃で 10 MPa 未満であり、 クリープ速度がAu-Cuの界面合金層の形成速度よりも遙かに速いと想定される。 その場合、図 3.8 に示すように、必要な金の厚みが Rzの半分以上であることが わかる。文献[14, 15]によれば、試験温度 340 ℃、歪み速度 2.0×10<sup>-5</sup> s におい て金の流動応力は 31 MPa であり[14]、歪み速度 20 /s と 9×10<sup>-6</sup> /s での引張強 度の違いは 26%である[15]。そのため、接合温度 350 ℃において 31 MPa より 26%高い 39 MPa の圧力があれば、 歪み速度 20 /s という高速で金が塑性変形す ると予想できる。さらに、二つの表面が最初に接する箇所は、図 3.8 に示す上下 の表面の頂点部分のみであり、その面積は、接合評価に用いた 10 mm 角のサン プルの面積である 100 mm<sup>2</sup>よりも遙かに狭い。そのため、接合時にかかった圧 力は、単純に接合時の荷重をサンプル面積 100 mm<sup>2</sup>で割って求めた 10 MPa よ り高い。前節で議論したように、本研究の系での拡散係数は 1.0×10<sup>-16</sup> m<sup>2</sup>/s で ある。仮に金の変形とともに拡散が生じたとしても、金の中の銅の濃度が 34.1% までの範囲では、ヤング率は増えない[16]。以上のことから、接合に必要な金 の厚みが Rz の半分以上であることがわかる。

高橋らは、接合は低温では界面拡散に支配される一方、高温ではクリープに より支配されると提案した[17]。本研究において 350 ℃の接合条件では、クリ ープが支配的な機構になっていると考えられる。その理由は、もし界面拡散が 支配的であれば、金の銅内部への拡散が同時に起こり表面粗さを吸収するのに 必要な純粋な金の量を減らしてしまうためである。

54

図 3.8 金による表面粗さ吸収の推定メカニズム[1]

3.4 結言

銅の直接接合において、柔らかく、酸化を防ぎ、かつ、接合後に銅と拡散す る金属を中間層として用いることを提案した。そのための唯一の材料である金 を銅表面に施す手段として、シンプルなめっき工程である DIG を選択した。そ の結果、金がサンプルの表面粗さを吸収し、予想通り提案した接合手法を実証 することができた。本手法により、Rz が 0.4 µm と粗い表面であっても従来の 平坦化の必要なく接合することが可能となった。ここでは、高さ 3 µm という低 背チップ間接合を達成した。この接合高さは、従来のはんだを用いたリフロー 工法では不可能である。さらに、本提案手法では、銅の厚みを薄くすることに より、接合高さをさらに低減できる。

## 3.5 参考文献

- [1] H. Noma et al., "Compensation of Surface Roughness Using an Au Intermediate Layer in a Cu Direct Bonding Process," Journal of Electronic Materials, published online (2018). doi: 10.1007/s11664-018-6428-x

- [2] H. Noma et al., "Cu-Cu Direct Bonding by Introducing Au Intermediate

Layer," Proceedings of International Workshop on Low Temperature Bonding for 3D Integration, 70 (2017).

- [3] D.B. Butrymowicz, et al., "Diffusion in Copper and Copper Alloys, Part II. Copper-Silver and Copper-Gold Systems," Journal of Physical and Chemical Reference Data 3, 527 (1974).

- [4] P.M. Hall et al., "Interdiffusion in the Cu-Au Thin Film System at 25 °C to 250 °C," Thin Solid Films 41, 341 (1977).

- [5] M.R. Pinnel et al., "On the Formation of the Ordered Phases CuAu and Cu<sub>3</sub>Au at a Copper/Gold Planar Interface," Metallurgical Trans. 10A, 741 (1979).

- [6] T. Shimatsu et al., "Atomic Diffusion Bonding of Wafers in Air with Thin Au Films and Its Application to Optical Devices Fabrication," Proceedings of IEEE International Workshop on Low Temperature Bonding for 3D Integration, 103 (2012).

- [7] D.F. Lim et al., "Surface Passivation of Cu for Low Temperature 3D Wafer Boding," ECS Solid State Letters 1, 11 (2012).

- [8] K. Sakuma et al., "Effects of Vacuum Ultraviolet Surface Treatment on the Bonding Interconnections for Flip Chip and 3-D Integration," IEEE Transactions on Electronics Packaging Manufacturing 33, 212 (2010).

- [9] N. Unami et al., "Effects of Excimer Irradiation Treatment on Thermocompression Au-Au Bonding," Japanese Journal of Applied Physics 49, 06GN12 (2010).

- [10] A. Okada et al., "Vacuum Ultraviolet Irradiation Treatment for Reducing Gold-Gold Bonding Temperature," Materials Transactions 54, 2139 (2013).

- [11] H. Petrova et al., "On the Temperature Stability of Gold Nanorods: Comparison Between Thermal and Ultrafast Laser-induced Heating," Physical Chemistry Chemical Physics 8, 814 (2006).

- [12] D. S. Liu et al., "Effects of Dopant, Temperature, and Strain Rate on the Mechanical Properties of Micrometer Gold-Bonding Wire," Journal of Electronic Materials 32, 159 (2003).

- [13] H. Ma et al., "Effect of Initial Cu Concentration on the IMC Size and Grain Aspect Ratio in Sn-xCu Solders during Multiple Reflows," Journal of Materials Science: Materials in Electronics 29, 602 (2018).

- [14] G-D. Sim et al., "High-temperature Tensile Behavior of Freestanding Au Thin Films," Scripta Materialia 75, 34 (2014).

- [15] K. Jonnalagadda et al., "Strain Rate Sensitivity of Nanocrystalline Au Films at Room Temperature," Acta Materialia 58, 4674 (2010).

- [16] J. Lohmiller et al., "Microstructure-property Relationship in Highly Ductile Au-Cu Thin Films for Flexible Electronics," Materials Science and Engineering A 527, 7731 (2010).

- [17] K. Takahashi et al., "Governing Mechanisms of the Joining procedure Without Heating and Pressuring and Effects of Surface Roughness on the Procedure," Journal of High Pressure Institute of Japan 35, 45 (1997) (in Japanese).

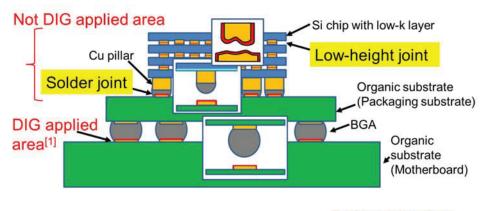

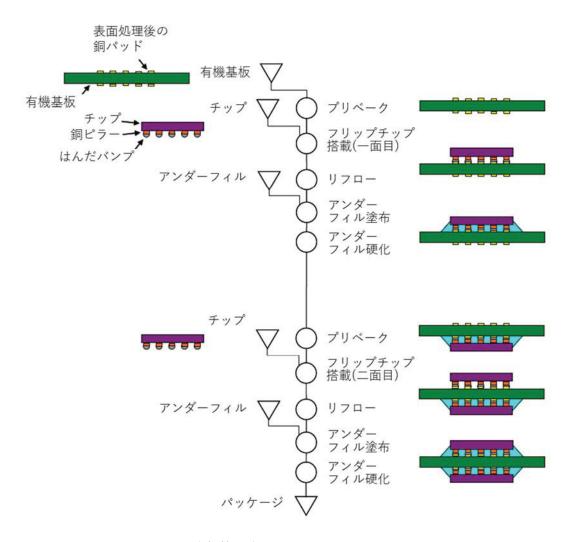

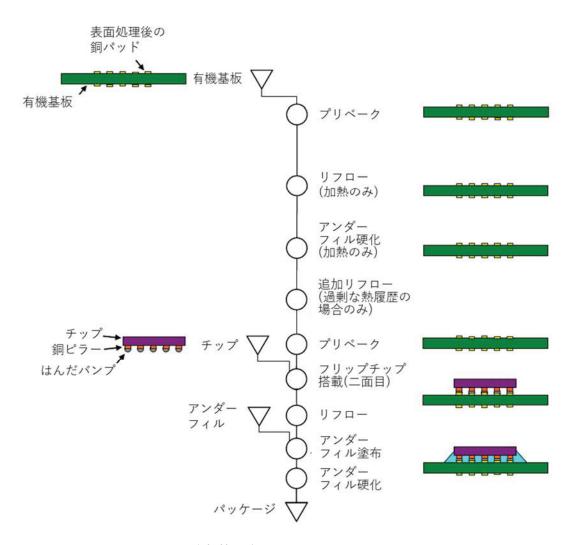

## 第四章 銅パッド表面処理の最適化による両面実装

本章は、OSP と、無電解スズめっきと DIG という金属の表面処理を用い、微 細ピッチのフリップチップにおける両面実装を検証した。両面実装の工程は図 4.1 に示す通りである。つまり、一面目の実装時の熱が二面目にもかかる。その ため、先ず、OSP の課題として、表面の酸化、OSP の銅への結合状態の変化、 および OSP が実装時にフラックスにより除去されるかが挙げられる。

次に、金属の表面処理の課題として、表面の酸化、表面処理した金属と銅と の拡散がある。OSP 処理では、厚みが分子層レベルで分解温度がリフロー温度 以下のものと、厚さ 0.3 μm で分解温度がリフロー温度以上のものとを用いた。 並行して、金属表面処理において、1.2 μm 厚さのスズめっきと、0.03 μm およ び 0.06 μm の DIG を実施した。その結果、OSP のうち、分解温度がリフロー温 度以下のものでは断面光学顕微鏡観察においてはんだが銅パッド表面に濡れて いることがわかった。これは、OSP が一面目のリフロー接合熱で分解したとし ても二面目を接合する際のフラックスがその酸化膜を還元できるためである。

一方、分解温度がリフロー温度以上のものでは、はんだが銅パッド表面に濡 れない箇所が観察された。これは、OSP の銅パッド表面への結合が一面目の実 装時の熱で強くなり、二面目の実装時のフラックスに溶けなくなったためであ る。金属を表面処理として用いた場合、先ず、スズめっきについては、はんだ が銅パッドへ濡れていない箇所があると確認できた。これは、一面目の実装時 の熱で界面合金層が成長し、リフロー時に溶融しない表面になったためである。

次に、DIG を用いた場合、厚さ 0.03 µm の DIG でははんだ接合が取れていな い箇所があることが電気的な導通試験から明らかになった。厚さ 0.06 µm の DIG では電気的な導通が確保されており、かつ、パッド表面へのはんだの濡れ 不良が無いことが断面の光学顕微鏡観察でわかった。ダイレクト金めっきの場 合は、0.2 µm に厚さを増し、加熱処理に関するプロセスマージンを十分に確保 することが重要であると考えられる。更なる微細なフリップチップ両面実装に おいては、微細なピッチでも、はんだブリッジを生じにくい DIG が OSP より 有利になる。本章の図表で[1, 2]から転載しているものの著作権は© 2009 The Japan Institute of Electronics Packaging である。 4.1 緒言

両面実装により、三次元実装パッケージのチップ積層数を減らせ、パッケージの放熱を効果的に行える。しかし、両面実装は片面実装と比べ二つの面で異なっている。第一に、第一面を実装するときの熱がもう片方の面にもかかることである。そのため、第一面を実装するときの熱が第二面のはんだ濡れ性を低減させる可能性がある。これは熱によりパッドが酸化する可能性があるためである。第二に、両面実装パッケージの温度サイクル(Temperature cycle, TC)信頼性は片面実装パッケージよりも悪くなる傾向にあることである。これは、はんだ接合部にかかる歪みが片面実装と両面実装とで異なるためである。

微細ピッチのフリップチップ実装向けの C2 技術では、無洗浄フラックスを用いる。これは、チップと基板間の隙間が狭く、フラックス洗浄が困難なためである。接合端子ピッチが 1 mm の BGA 両面実装では、洗浄が必要となる高い活性のフラックスを使うことができる。しかし、高い活性のフラックスは微細ピッチのフリップチップ接合には前述の理由で使えない。そのため、両面フリップチップ実装は両面 BGA 実装と比べて困難である。

本章では、三次元実装パッケージの放熱を目的とし、基板側の銅パッドへの 表面処理を複数調べ、微細ピッチ両面実装時のはんだ濡れ性や信頼性を評価した[1,2]。

## 4.2 実験

4.2.1 両面実装のプロセスフロー

両面実装には C2 技術[3]を応用した。図 4.1 に両面実装のプロセスフローを 示す。

先ず、片面(第一面)をフリップチップ実装しアンダーフィルを行う。次に、 もう片面(第二面)をフリップチップ実装しアンダーフィルを行う。信頼性評価 にあたっては、このプロセスを用いた。

信頼性評価に先立ち、はんだ濡れ性を調べた。その目的で、チップ実装の代わりに第一面実装時と同じ熱履歴をかけた。そのプロセスフローを図 4.2 に示す。

図 4.1 両面実装評価サンプルのプロセスフロー (信頼性評価サンプル)[2]

図 4.2 両面実装評価サンプルのプロセスフロー (はんだ濡れ性評価サンプル)[2]

はんだ濡れ性のマージンを見る目的で、二つの条件の熱履歴をかけた。

- (1) C2 技術における標準的な熱履歴(標準熱履歴)

- (2) マージン評価のための過剰な熱履歴(過剰熱履歴)

標準熱履歴と過剰熱履歴との違いを表 4.1 に示した。プロセス中で熱が加わる のは、基板プリベーク、リフロー、アンダーフィル硬化である。そのうち、最 も高温になるのはリフローで、次がアンダーフィル硬化である。標準熱履歴で は、上記三工程のどれも、C2 技術における標準的な温度・時間をかけた。それ に対し、過剰熱履歴においては、プリベーク、アンダーフィル硬化について時 間を延ばし、また、リフローについては余分に工程を通すことによって、加熱 処理についてのプロセスマージンを評価できるようにした。

過剰熱履歴において、二面目を実装する前に二度リフローを行っており、また、アンダーフィル硬化の熱は標準条件の2倍の時間をかけた。プリベークは 有機基板のブリスターを防止するために湿気を取り除く工程である。過剰熱履 歴において、基板が複数回ベークされたときのことを想定して、標準条件の6 倍の時間をかけた。

| 工程        | 信頼性評価 | はんだ濡れ性評価 |            |

|-----------|-------|----------|------------|

|           | 標準熱履歴 | 標準熱履歴    | 過剰熱履歴      |

| 基板プリベーク   | 標準条件  | 標準条件     | 標準条件の6倍の時間 |

| 一面目チップ搭載  | 標準条件  | なし       | なし         |

| リフロー      | 標準条件  | 標準条件     | 標準条件       |

| アンダーフィル塗布 | 標準条件  | なし       | なし         |

| アンダーフィル硬化 | 標準条件  | 標準条件     | 標準条件の2倍の時間 |

| 追加リフロー    | なし    | なし       | 標準条件で1回    |

| 基板プリベーク   | 標準条件  | 標準条件     | 標準条件の6倍の時間 |

| 二面目チップ搭載  | 標準条件  | 標準条件     | 標準条件       |

| リフロー      | 標準条件  | 標準条件     | 標準条件       |

| アンダーフィル塗布 | 標準条件  | 標準条件     | 標準条件       |

| アンダーフィル硬化 | 標準条件  | 標準条件     | 標準条件       |

表 4.1 サンプルに対する熱履歴[1]

4.2.2 はんだ濡れ評価

はんだの濡れ性を下記の手法で評価した。

(1) 電気的な導通

二面目を実装した後に、チップと基板間の電気的な導通をテスターを用い て評価した。1 MΩ以上の抵抗を示したサンプルを不良と見なした。

(2) 断面観察

二面目のアンダーフィル硬化後に断面研磨を行い、はんだがパッド上に良 好に濡れているかを光学顕微鏡で確認した。表面処理が無電解スズ以外の場 合は、パッド表面の一部領域ではんだも IMC も見つからない箇所があれば、 それをはんだの濡れ不良と判断した。表面処理が無電解スズの場合は、チッ プ側のはんだと基板側の無電解スズの間に黒い筋が観察されれば、それを濡 れ不良と判断した。一つの断面の中にある接合部の個数は、80 µm ピッチの 評価基板では 82 個、50 µm ピッチの評価基板では 136 個であった。

4.2.3 温度サイクル信頼性評価

信頼性評価は、表 4.2 に示す条件で行った。信頼性評価は、使用環境条件より も厳しい条件において短期間で評価を行う加速試験を用いた。その項目として、 温度サイクルテスト(Temperature cycle, TC)と温湿度バイアステスト (Temperature humidity bias, THB)がある。先ず、TC は、電気製品のスイッチ を ON/OFF したときにパッケージ温度が上下することを模擬したものである。 温度が上下すると、パッケージを構成する材料同士の熱膨張係数差に起因する 応力が発生し、配線や接合部のクラックや破断の原因となる。その結果として 起こる抵抗上昇の度合いを調べた。

次に、THB では、湿度のある環境下で電気製品を動作させたときにパッケー ジ内部でエレクトロケミカルマイグレーション[4]に起因する配線間や接合部間 の絶縁不良が生じないかを調べた。

また、信頼性試験の前処理として、パッケージを吸湿させた後にリフローを 行った。その条件は、JEDEC 規格[5]に従い、民生品用途で一般的な JEDEC Level3 (125 ℃ベークを 24 時間行い乾燥させた後、30 ℃/60%RH での吸湿を 192 時間行い、最後に 260 ℃ピークのリフローを 3 回実施)相当を実施した。

| 項目               | 条件                     |

|------------------|------------------------|

| 信頼性試験前処理         | JEDEC Level3 相当        |

| 温度サイクルテスト (TC)   | -55 ℃から 125 ℃、2 サイクル/h |

| 温湿度バイアステスト (THB) | 85 °C、85 %RH、3.7 V     |

表 4.2 信頼性評価条件[1]

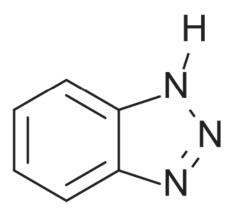

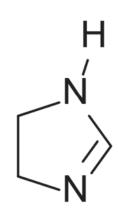

4.2.4 ダイレクト金めっき等の表面処理

評価に用いた表面処理を表 4.3 にまとめた。OSP[6]、無電解スズめっき[6]、 DIG[7]を評価した。OSP は銅表面を酸化から防止する工程であり、C2 技術で 用いられる。ベンゾトリアゾールとイミダゾールの化学式を図 4.3 に示す。それ ぞれの分子中の N が銅と錯体結合することにより、銅が酸化から保護される。

実験において OSP で濡れ不良が見つかった際に、無電解スズめっき (Electroless Sn, E-less Sn) や DIG を評価した。スズは銅よりもイオン化傾向が 大きいため酸化が懸念点ではあるが、リフロー時に溶融して良好なはんだ濡れ 性を示すことを期待した。スズのウィスカもスズめっきにおける懸念点である [8,9]。

実装前に40倍の光学顕微鏡でパッド表面を観察したところ、スズめっきされ たパッド上にウィスカは観察されなかった。ウィスカは長さ0.1 mm 程度と、光 学顕微鏡で観察できるサイズにまで成長することが知られており[9]、本研究に おいてもウィスカの有無を判断するには光学顕微鏡観察で十分と判断した。

DIG は銅のパッドを、銅よりも遙かにイオン化傾向の低い金で覆うことによ り酸化を抑制するプロセスである。無電解 Ni/Au めっき[10]は、Ni の厚みが 3 µm あるため微細ピッチには適さないと判断した。DIG は、Ni を用いないため、 微細ピッチに用いることができる。

65

| 表面処理  | 形成される物質   | 厚み      | パッドピッチ |

|-------|-----------|---------|--------|

| OSP-A | ベンゾトリアゾール | 単分子層    | 80 µm  |

| OSP-B | イミダゾール錯体  | 0.2 μm  | 80 µm  |

| OSP-C | イミダゾール錯体  | 0.2 μm  | 80 µm  |

|       |           | 0.3 μm  | 80 µm  |

| OSP-D | イミダゾール錯体  | 0.2 μm  | 80 µm  |

| 無電解スズ | Sn        | 1.2 μm  | 80 µm  |

| DIG   | Au        | 0.03 μm | 50 µm  |

|       |           | 0.06 µm | 50 µm  |

表 4.3 実装評価に用いた表面処理[1]

(a)

図 4.3 OSP 構成材料の化学式。 (a)ベンゾトリアゾール、(b)イミダゾール。

4.2.5 評価用基板

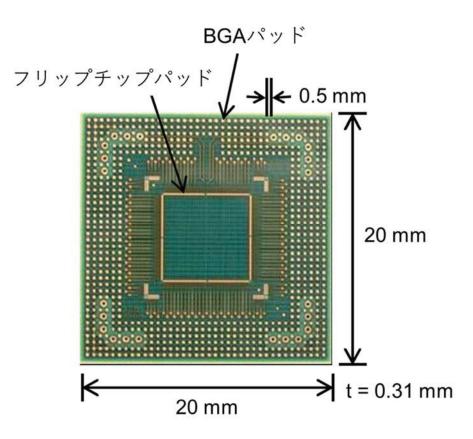

図 4.4 に TV (Test vehicle) 基板の全体写真を示す。基板サイズは 20 mm×20 mm×t0.31 mm、チップサイズは 7.3 mm×7.3 mm×t0.725 mm である。ピッチ の異なる、80  $\mu$ m ピッチと 50  $\mu$ m ピッチの二種類の TV を用いた。フリップチ ップ用のパッドはチップの周辺部に対応するように並んでいる。パッド数は 80  $\mu$ m ピッチの場合は 328 個 (一辺あたり 82 個)、50  $\mu$ m ピッチの場合は 544 個 (一 辺あたり 136 個) である。

図 4.4 TV 基板の全体写真(80 µm パッドピッチ)[2]

4.3 はんだ濡れ性の結果と考察

評価結果を表 4.4 に示す。OSP-A および OSP-B については、過剰熱履歴にお いても断面観察で濡れ不良が観察されなかった。また、DIG t0.06 μm の場合は、 標準熱履歴において、断面観察で濡れ不良は観察されなかった。ここから、Au は Cu へ速く拡散すると言われる[11]ものの、片面実装の熱履歴であれば、表面 に金が残ることがわかる。つまり、微細化への障害となるニッケルバリア層を 介さずに銅パッド上に金を処理しても、両面実装できるということが確認でき た。

なお、OSP-C と OSP-D は、標準熱履歴サンプルの断面観察にて、はんだの 濡れ不良が存在した。そのため、過剰熱履歴の評価は必要ないと判断した。ま た、DIG は、t0.03 μm の水準にて、電気的な導通が確認できなかったため、断 面観察は必要ないと判断した。さらに、DIG t0.06 μm であっても、複数回のリ フローを行う過剰熱履歴には耐えないと判断し、t0.03 μm だけでなく t0.06 μm の水準についても過剰熱履歴の評価は行わなかった。この点について、今後、 DIG 厚みの更なる最適化を行う必要があるが、現在の DIG 技術で形成可能な最 大の厚みである 0.2 μm とするのが適切と考えている。

4.3.1 有機防錆被膜での濡れ不良の薬品種・厚みへの依存

(1) 電気的な導通

電気的な導通はどの水準でも確認できた。しかし、接合部が局所的に接し ていれば、残りの部分が濡れ不良があったとしても電気的な導通は確認でき る。そのため、断面観察による濡れ不良の評価も実施した。

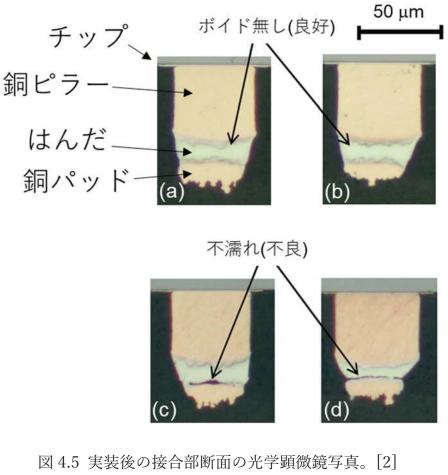

(2) 断面観察

図 4.5 に示すように、はんだは OSP-A や OSP-B の場合には、はんだはボ イド無く濡れていた。標準熱履歴だけでなく過剰熱履歴においても、ボイド は観察されなかった。対照的に、OSP-C や OSP-D でははんだの濡れ不良が 見つかった。それは、パッド表面のうちはんだも IMC も見つからない箇所 である。

OSP は表面の酸化を抑制する目的で実施される。しかし、耐熱性のある OSP-B, C, D については、OSP の銅パッド表面への結合が一面目の実装時の熱 で錯体結合から共有結合へと変化し、二面目の実装時のフラックスに溶けなく なったと考察している。有機物である OSP がリフローでのはんだ溶融時にパッ ド上に残っていると、はんだの濡れを阻害しボイドの原因となる。OSP の中で、 OSP-B は無洗浄フラックスに溶けやすかったと考えられる。

一方、一面目の実装時の熱で分解する OSP-A も良好な結果を示したのは、 OSP が一面目のリフロー接合熱で分解したとしても二面目を接合する際のフラ ックスがその酸化膜を還元できるためである。

4.3.2 無電解スズでの濡れ不良の熱履歴への依存

(1) 電気的な導通

電気的な導通は標準熱履歴、過剰熱履歴どちらの水準でも確認できた。

(2) 断面観察

無電解スズめっきは、標準熱履歴において良好なはんだ濡れ性を示した。し かし、過剰熱履歴においては図 4.5 に示すように濡れ不良が見つかった。

電解スズが過剰熱履歴において濡れ不良を示した原因として、(1)スズが酸化 しすぎて無洗浄フラックスの還元効果では酸化膜が除去されなかったこと、(2) IMC が成長しすぎて表面に到達し、その IMC が酸化してフラックスでは還元さ れなくなったことが考えられる。(2)の理由は、Cu-Sn 化合物の酸化物が、Cu 酸化物や Sn 酸化物よりも電気化学的に安定であるためである[12]。

4.3.3 ダイレクト金めっきでの濡れ不良の膜厚への依存

(1) 電気的な導通

電気的なオープン(接続不良)は t0.03 μm の DIG についてのみ見つかっ た。これは、一面目の実装時の熱をかけた際に金が銅の中へと拡散し、表面 に露出した銅が酸化し、さらに、その酸化銅がフラックスの還元力では還元 されなかったためであり、はんだ濡れ性の点で問題がある。一方 DIG t0.06 μm の場合は、電気的な導通が確認できた。

(2) 断面観察

DIG t0.03 μm は濡れ不良を示した一方で、DIG t0.06 μm は良好な濡れ性 を示した。 DIG t0.03 µm の導通不良の結果は、金が銅の中へと拡散し、銅表面が酸化し たためである。この点を以下に考察する。先ず、銅表面が一面目の実装時の熱 で露出する点は、OSP-A も DIG t0.03 µm のときも同様である。しかし、OSP-A の場合は表面が Cu のみであるのに対し、DIG t0.03 µm の場合は表面に Au と Cu とが共存する。このとき、表面が熱酸化すると、Au-Cu 化合物の酸化物が形 成される。この酸化物が、上記 Cu-Sn 酸化物の場合と同様、Cu 酸化物よりも電 気化学的に安定であると考えている。

つまり、DIG を使う場合は、熱履歴がかかったとしてもパッド表面に Cu が 露出しない、と考えられるが、その際 DIG を十分な厚みにする必要がある。こ のため、現時点で処理可能な最大の膜厚である t0.2 μm にするのが適切であると 考えている。

4.3.4 微細ピッチの両面実装へのダイレクト金めっきの有望性

第二章の図 2.6 に示したように、DIG 表面のパッドは OSP 表面のパッドより も、はんだの濡れ性が良い。これは、はんだが隣り合う接合部へと広がる可能 性が低いことを意味している。そのため、将来的にパッドピッチが、今回評価 した 50 μm より更に微細になったとしても、はんだブリッジが生じにくい。つ まり、DIG は更なる微細ピッチの両面実装に向けた最有力の技術である。

| 実験条件      |      | 結果  |       |     |       |     |

|-----------|------|-----|-------|-----|-------|-----|

| 表面処理      | 評価手法 | 単位  | 標準熱履歴 |     | 過剰熱履歴 |     |

|           |      |     | 不良数   | 評価数 | 不良数   | 評価数 |

| OSP-A     | 電気導通 | チップ | 0     | 3   | 0     | 2   |

| 単分子層      | 断面観察 | 接合部 | 0     | 82  | 0     | 82  |

| OSP-B     | 電気導通 | チップ | 0     | 4   | 0     | 1   |

| t0.2 μm   | 断面観察 | 接合部 | 0     | 82  | 0     | 82  |

| OSP-C     | 電気導通 | チップ | 0     | 4   | 評価せず  |     |

| t0.2 μm   | 断面観察 | 接合部 | 13    | 82  |       |     |

| OSP-C     | 電気導通 | チップ | 0     | 5   | 評価せず  |     |

| t0.3 μm   | 断面観察 | 接合部 | 19    | 82  |       |     |

| OSP-D     | 電気導通 | チップ | 0     | 5   | 評価せず  |     |

| t0.2 μm   | 断面観察 | 接合部 | 11    | 82  |       |     |

| E-less Sn | 電気導通 | チップ | 0     | 5   | 0     | 2   |

| t1.2 μm   | 断面観察 | 接合部 | 0     | 82  | 35    | 82  |

| DIG       | 電気導通 | チップ | 1     | 4   | 評価せず  |     |

| t0.03 µm  | 断面観察 | 接合部 | 評価せず  |     |       |     |

| DIG       | 電気導通 | チップ | 0     | 3   | 評価せず  |     |

| t0.06 µm  | 断面観察 | 接合部 | 0     | 136 |       |     |

表 4.4 実装評価結果。[1]を基に改変。

(a) OSP-A、単分子層、標準熱履歴。

(b) OSP-B、t0.2 μm、標準熱履歴。

(c) OSP-C、t0.3 μm、標準熱履歴。

(d) 無電解スズ、t1.2 μm、過剰熱履歴。

4.4 濡れ不良の無い両面実装パッケージでの温度サイクル信頼性評価

OSP-A と OSP-B について信頼性試験を実施した結果を表 4.5 に示す。OSP-A と OSP-B はともに、TC 試験、THB 試験において良好な信頼性を示した。

ここで、TC3,250 サイクルは、一般的な評価で行われる 1,000 サイクル[13] の 3 倍を超すサイクル数である。この評価の対象である両面実装パッケージは 対称構造であり、パッケージ基板が反りにくいため、はんだ接合部の信頼性は 片面実装よりも不利になると予想された。それは、片面実装において、チップ が 150 µm と薄い場合の方が、775 µm の場合よりもパッケージ基板が反りやす く、結果として TC 試験での電気抵抗上昇率が低いというデータがあったため である[14]。今回の両面実装での TC 信頼性評価結果は、その懸念を取り除くも のである。表面処理が DIG の場合も、DIG 厚みが十分で濡れ不良無く試料を作 れれば、信頼性試験において同様に良好な結果を示すと考えられる。

THB1,000 h は、この試験において一般的に行われる時間である[13]。両面実装と片面実装のいずれもエレクトロケミカルマイグレーション性で不利になる 点は予想されなかった。そのため、本試験は一般的な評価時間で行った。

| 表面処理    | 信頼性評価結果    |           |  |

|---------|------------|-----------|--|

|         | ТС         | THB       |  |

| OSP-A   | 3,250 サイクル | 1,000 h   |  |

| 分子層厚さ   | 30/30 個パス  | 16/16 個パス |  |

| OSP-B   | 3,250 サイクル | 1,000 h   |  |

| t0.2 μm | 26/26 個パス  | 15/15 個パス |  |

表 4.5 信頼性評価結果[1]

4.5 結言

両面実装においては、一面目の実装時の熱が二面目にもかかるため、表面の 酸化や、表面処理と下地の銅が反応する課題がある。

そこで、両面実装を OSP および金属表面処理をした銅パッドへ行い、はんだ 濡れ性を調べた。OSP については、一面目のリフローを行っても残る耐熱性を 持つものと、一面目の実装時に分解する種類のものを選択した。また、金属表 面処理として、はんだの主成分であるスズと、酸化しにくい金とを用意した。 その手段として、無電解スズと DIG に着目し提案した。

OSP については、耐熱性だけでなく、フラックスへの溶解性も重要であるこ とがわかった。それは、リフロー時に OSP が残存していると、有機物である OSP が、はんだの濡れ不良の原因となるためである。さらに、良好なはんだ濡 れ性を示した OSP について信頼性評価を行った。両面実装パッケージにおいて、 TC、THB 試験ともに良好な信頼性データが得られた。

無電解スズめっきにおいては、表面の酸化や IMC 成長があるため、一面目実 装時に熱履歴が過剰にかかると、はんだの濡れ不良が生じることがわかった。

DIG については、t0.06 μm であれば、はんだの濡れ不良の無い実装結果を得ることを確認することができた。さらに DIG 膜の厚さを厚く、例えば、t0.2 μm にすることにより安定した両面実装技術を確立できると考えている。

以上、提案した表面処理のうち更なる微細ピッチの両面実装には DIG を用いる手法が最有力であることを示した。

4.6 参考文献

- H. Noma et al., "Wettability and Reliability for Double-Sided Assembly with Chip Connection (C2) Flip-Chip Technology," Transactions of the Japan Institute of Electronics Packaging 2, 85 (2009).

- [2] H. Noma et al., "Wettability and Reliability on Double Side Assembly with Metal Post Solder - Chip Connection Flip Chip Technology," Proceedings of International Conference on Electronics Packaging, 568 (2009).

- [3] Y. Orii et al., "Micro Structure Observation and Reliability Behavior of Peripheral. Flip Chip Interconnections with Solder-Capped Cu Pillar

Bumps," Transactions of the Japan Institute of Electronics Packaging 4, 73 (2011).

- [4] S. Yang et al., "Failure Model for Silver Electrochemical Migration," IEEE Transactions on Device and Materials Reliability 7, 188 (2007).

- [5] JEDEC Solid State Technology Association, "Sensitivity Classification for Nonhermetic Surface Mount Devices," IPC/JEDEC J-STD-020D.1 (2008).

- [6] C. Ryu et al., "Novel Approaches to Current BGA Packaging Challenges," Proceedings of Electronics Packaging Technology Conference, 1258 (2008).

- [7] S. Hashimoto et al., "Direct immersion gold (DIG) as a final finish," Circuit World 32, 16 (2006).

- [8] J. Lee, "The Sn Whisker Growth Evolution of IC Packaging on the PC Board Assembly," Proceedings of Electronic Components and Technology Conference, 1964 (2007).

- [9] K. N. Tu, "Interdiffusion and Reaction in Bimetallic Cu-Sn Thin Films," Acta Metalluragica 21, 347 (1973).

- [10] K. Yokomine et al., "Development of Electroless Ni/Au Plated Build-up Flip Chip Package with Highly Reliable Solder Joints," Proceedings of Electronic Components and Technology Conference, 1384 (2001).

- [11] D.B. Butrymowicz et al., "Diffusion in Copper and Copper Alloys, Part II. Copper - Silver and Copper - Gold Systems," Journal of Physical and Chemical Reference Data 3, 527 (1974).

- [12] H. Takao et al., "Wettability of Cu and Cu-Sn Intermetallic Compound by Sn-Pb Solder Alloy," Quarterly Journal of the Japan Welding Society 15, 623 (1997) (in Japanese).

- [13] T. Hisada et al., "Fine Pitch Wirebonds on Ultra Low-k Device," Transactions of the Japan Institute of Electronics Packaging 4, 17 (2011).

- [14] K. Toriyama et al., "Development of fine pitch flip chip interconnection using solder bump," Proceedings of Microelectronics Symposium, 143 (2007) (in Japanese).

## 第五章 結論と今後の展望

5.1 結論

本論文は、超高周波用三次元高密度実装のためのダイレクト金めっきを用いた低応力接合技術について述べた。

第一章では、IoT 社会における三次元実装の課題として、放熱とパッケージ厚 みを挙げた。さらに、これらの課題に関する従来技術を纏め、本研究の目的に ついて述べた。

第二章では、銅ピラーを用いたフリップチップにおけるリフロー接合工法で ありながら、プロセス中に Low-k 層を保護できる銅ピラー・はんだ接合構造を 実現した。具体的には、銅パッドの表面処理を OSP から DIG に変えることに より、Low-k 層への応力が 15%低減することを見いだした。その理由を以下の ように考察している。先ず、DIG 表面上には、はんだが広く濡れ広がるため、 はんだ接合部に残るはんだ量が、DIG の場合は OSP よりも少なくなる。次に、 その結果として、OSP の場合は銅ピラーの側面にはんだが濡れ上がるのに対し、 DIG の場合は濡れ上がらなくなる。その形状が理由で、リフロー後の冷却時に チップ側にある銅ピラーがはんだによって側面から押される力が低減し、Low-k 層が銅ピラーから受ける応力が減少する。本章の結果により、チップ内の Low-k 層の機械的信頼性が向上し、絶縁層として、より誘電率の低い材料を使えるよ うになり、チップの発熱を抑制しつつ動作周波数を向上できることを見出した。

第三章では、銅の直接接合にナノメートルレベルの平坦化や真空が必要であ るという課題に着目した。そこで、柔らかく、酸化しにくく、かつ、銅へと拡 散する金を中間層として用いる工程を提案した。本工程は以下の3つの段階に 分けることができる。第1の段階では、加熱環境下で上下チップの銅上にある 金同士が接触し、金が塑性変形により表面粗さを吸収し平らにする。第2の段 階では、加熱・加圧環境下で金同士が固相拡散接合を起こす。第3の段階では、 加熱環境下で金が銅の中へと拡散し、擬似的な銅の直接接合が形成される。本 工程を実現する手段として DIG を用いた。これは、前述のナノメートルレベル での平坦化や真空を必要としない接合工程である。その結果、従来のはんだリ フロー工法では実現不可能な3µmの接合高さを実現した。銅の厚さを薄くする ことにより、この接合高さをさらに低減できる可能性を見出した。

第四章では、微細ピッチのフリップチップの両面実装について述べた。両面 実装では、一面目実装時の熱が二面目にもかかる。そのため、基板側の銅パッ ドが酸化したり、パッド表面処理が下地の銅と反応したりする課題がある。そ こで、OSP に加え、酸化しにくい金を用意した。金の表面処理の手段として、 ニッケル金めっきよりも微細ピッチに適した DIG を提案した。その結果、OSP が化学組成や膜厚に依存して濡れ不良を起こす一方で、DIG は厚みが十分に確 保されていれば濡れ不良が生じないことが判明し、微細ピッチのフリップチッ プにおける両面実装を実現した。更なる微細ピッチには、はんだのブリッジが 生じにくい DIG の方が OSP より有望である。

以上より、超高周波用三次元高密度実装において key になる要素技術を確立 できた。

5.2 今後の展望

本論文の成果は三次元実装を必要とする様々な分野へ応用できる。その応用 例を本節で述べる。

#### 5.2.1 ミリ波通信

自動車通信では 77 GHz の超高周波が用いられる[1]。このような超高周波向 けの三次元実装では、配線や TSV とともに信号を損失させる要素として、銅ピ ラーとはんだを組み合わせたフリップチップ接合が電気測定評価されている[1]。 はんだよりも電気抵抗が小さい銅をダイレクト接合させることにより、損失を さらに低減できる。

5.2.2. チップ間のリフロー接合